## **TECHNICAL MANUAL**

## OPERATOR'S, UNIT AND INTERMEDIATE DIRECT SUPPORT, AND GENERAL SUPPORT MAINTENANCE MANUAL

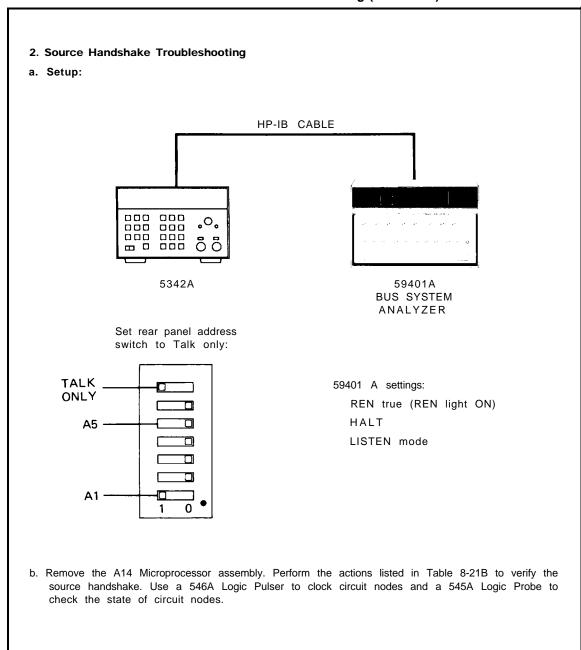

## MICROWAVE FREQUENCY COUNTER TD-1225A(V)2/U (HEWLETT-PACKARD MODEL 5342A/H16) (NSN 6625-01-121-6934)

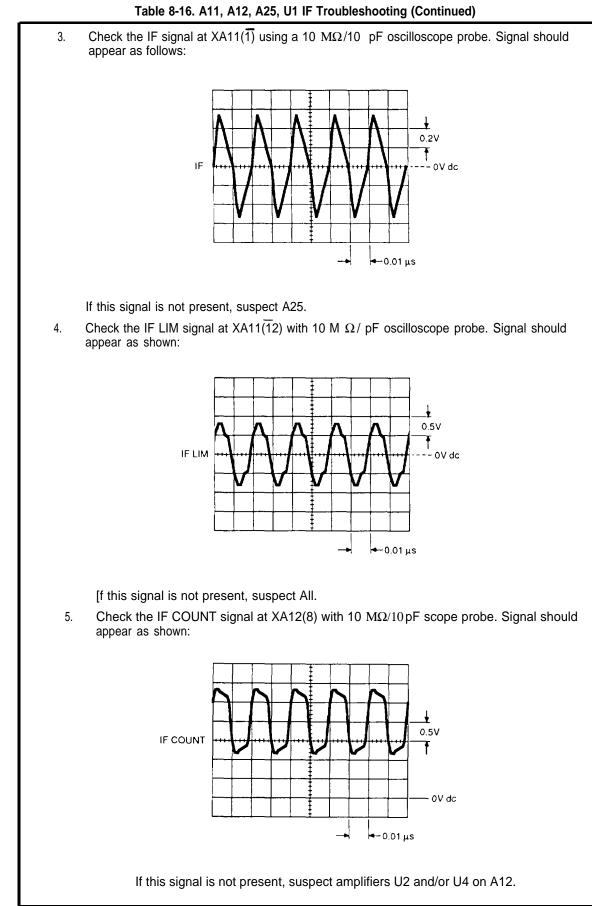

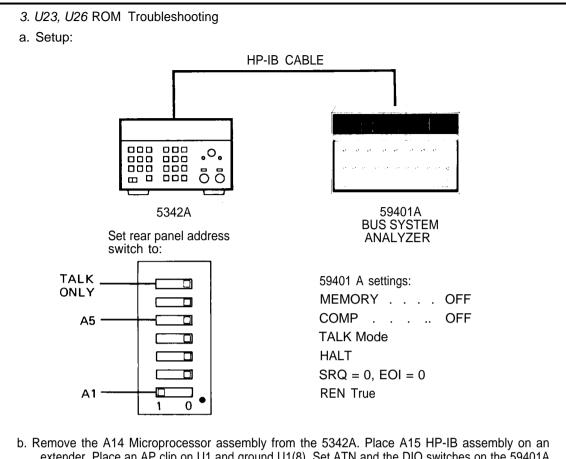

Distribution authorized to the Department of Defense and DOD contractors only for official use or far administration or operational purposes. This determination was mode on 20 June 1988. Other requests far this document will be referred to Commander, US Army Communications-Electronics Command and Fort Monmouth, ATTN: AMSEL-LC-ME-P, Fart Monmouth, NJ 07703-5000.

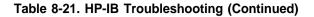

DESTRUCTION NOTICE – Destroy by any method that will prevent disclosure of contents or reconstruction of the document.

HEADQUARTERS, DEPARTMENT OF THE ARMY 1 OCTOBER 1988

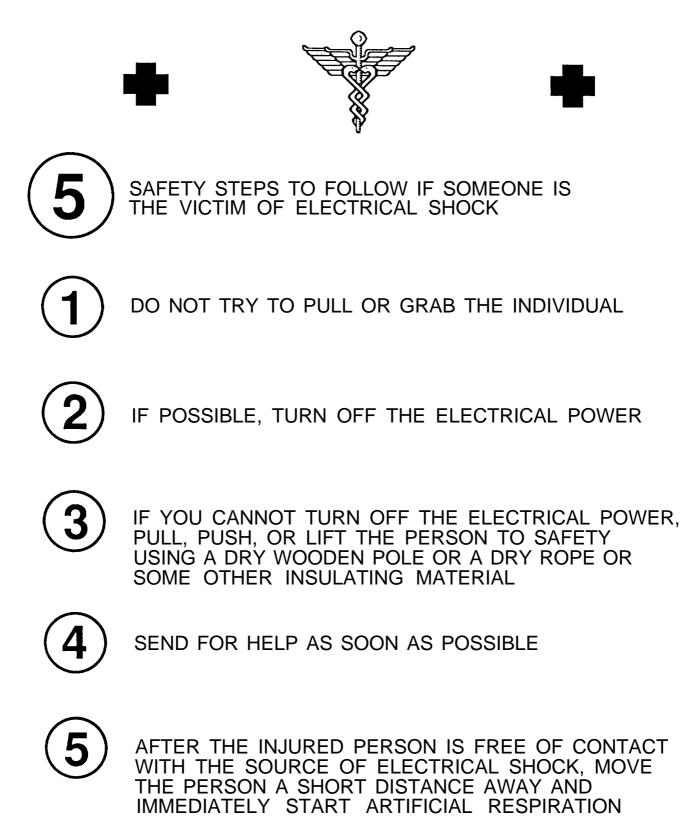

## WARNING

## HIGH VOLTAGE

is used in the operation of this equipment

## DEATH ON CONTACT

may result if personnel fail to observe safety precautions

Never work on electric equipment unless there is another person nearby who is familiar with the operation and hazards of the equipment and who is competent in administering first aid. When technicians are aided by operators, they must be warned about dangerous areas.

Be careful not to contact high-voltage connections of 115-volt ac input when installing or operating this equipment.

Whenever the nature of the operation permits, keep one hand away from the equipment to reduce the hazard of current flowing through vital organs of the body.

Do not be misled by the term "LOW VOLTAGE". Potentials as low as 50 volts may cause death under adverse conditions,

For Artificial Respiration refer to FM 21-11.

# CAUTION

## THIS EQUIPMENT CONTAINS PARTS AND ASSEMBLIES SENSITIVE TO DAMAGE BY ELECTROSTATIC DISCHARGE (ESD). USE ESD PRECAUTIONARY PROCEDURES WHEN TOUCHING, REMOVING OR INSETING PRINTED CIRCUIT BOARDS.

## ESD CLASS 1

## NOTE

The symbol for static sensitive devices in military inventory is as depicted in the caution block above

GENERAL HANDLING PROCEDURES FOR ESDS ITEMS

.USE WRIST GROUND STRAPS OR MANUAL .GROUNDING PROCEDURES .KEEP ESDS ITEMS IN PROTECTIVE COVERING .WHEN NOT IN USE .GROUND ALL ELECTRICAL TOOLS AND TEST .EQUIPMENT PERIODICALLY CHECK CONTINUITY AND RESISTANCE OF GROUNDING SYSTEM

USE ONLY METALIZED SOLDER SUCKER HANDLING

ESDS ITEMS ONLY IN PROTECTED AREAS

## MANUAL GROUNDING PROCEDURES

. MAKE CERTAIN EQUIPMENT IS POWERED DOWN .TOUCH GROUND PRIOR TO INSERTING REPLACEMENT • TOUCH GROUND PRIOR TO REMOVING ESDS ITEMS ESDS ITEMS

.TOUCH PACKAGE OF REPLACEMENT ESDS ITEM TO

GROUND BEFORE OPENING

## ESD PROTECTIVE PACKAGING AND LABELING

INTIMATE COVERING OF ANTISTATIC MATERIAL WITH AN OUTER WRAP OF EITHER TYPE 1 ALUMINIZED MATERIAL OR CONDUCTIVE PLASTIC FILM OR HYBRID LAMINATED BAGS HAVING AN INTERIOR OF ANTISTATIC MATERIAL WITH AN OUTER METALIZED LAYER

LABEL WITH SENSITIVE ELECTRONIC SYMBOL AND CAUTION NOTE

Devices such as CMOS, NMOS, MNOS, VMOS, HMOS, thin-film resistors PMOS, and MOSFET used in many equipments can be damaged by static voltages present in most repair facilities. Most of the components contain internal gate protection circuits that are partially effective, but sound maintenance practice and the cost of equipment failure in time and money dictate careful handling of all electrostatic sensitive components.

The following precautions should be observed when handling all electrostatic sensitive components and units containing such components.

Failure to observe all of these precautions can cause permanent damage to the electrostatic sensitive device. This damage can cause the device to fail immediately or at a later date when exposed to an adverse environment.

- STEP 1 Turn off and/or disconnect all power and signal source and loads used with the unit.

- STEP 2 Place the unit on grounded conductive work surfaces.

- STEP 3 Ground the repair operator using a conductive wrist strap or other device using a 1 -M series resistor to protect the operator.

- STEP 4 Ground any tools (including soldering equipment) that will contact the unit. Contact with the operator's hand provides a sufficient ground for tools that are otherwise electrically isolated.

- STEP 5 All electrostatic sensitive replacement components are shipped in conductive foam or tubes and must be stored in the original shipping container until installed,

- STEP 6 When these devices and assemblies are removed from the unit, they should be placed in the conductive work surface or in conductive containers.

- STEP 7 When not being worked on, wrap disconnected circuit boards in aluminum foil or in plastic bags that have been coated or impregnated with a conductive material.

- STEP 8 Do not handle these device unnecessarily or remove from their packages until actually used or tested.

Page

This Manual includes copyright material reproduced by permission of Hewlett-Packard Company.

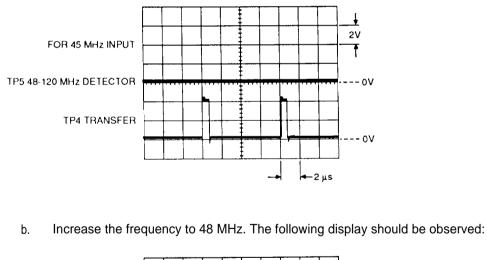

Technical Manual

No. 11-6625-3014-14-1

HEADQUARTERS DEPARTMENT OF THE ARMY Washington, DC, 1 October 1988

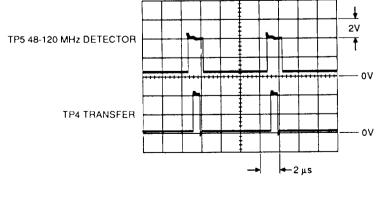

## OPERATOR'S, UNIT AND INTERMEDIATE DIRECT SUPPORT, AND GENERAL SUPPORT MAINTENANCE MANUAL FOR MICROWAVE FREQUENCY COUNTER TD 1225A(V)2/U (HEWLETT-PACKARD MODEL 5342A/H16) (NSN 6625-01-121-6934)

## REPORTING ERRORS AND RECOMMENDING IMPROVEMENTS

You can help improve this manual. If you find any mistakes or if you know of a way to improve the procedures, please let us know. Mail your letter, DA Form 2028, (Recommended Changes to Publications and Blank Forms) or 2028-2 located in back of this manual direct to: Commander, U.S. Army Communications-Electronics Command, ATTN: AMSEL-LC-ME-PS, Fort Monmouth, New Jersey 07703-5000,

In either case, a reply will be furnished to you.

## TABLE OF CONTENTS

#### Section

| 0 | GEN  | GENERAL INFORMATION                                     |     |  |  |  |

|---|------|---------------------------------------------------------|-----|--|--|--|

|   | 0-1  | Scope                                                   | 0-1 |  |  |  |

|   | 0-2  | Consolidated Index of Army Publications and Blank Forms | 0-1 |  |  |  |

|   | 0-3  | Maintenance Forms, Records, and Reports                 | 0-1 |  |  |  |

|   |      | Report of Maintenance and Unsatisfactory Equipment      | 0-1 |  |  |  |

|   |      | Reporting of Item and Packaging Discrepancies           | 0-1 |  |  |  |

|   |      | Transportation Discrepancy Report(TDR)                  | 0-1 |  |  |  |

|   | 0-4  | Reporting Equipment Improvement Recommendations (EIR's) | 0-1 |  |  |  |

|   | 0-5  | Administrative Storage                                  | 0-1 |  |  |  |

|   | 0-6  | Destruction of Army Electronics Materiel                | 0-1 |  |  |  |

|   | 0-7  | Warranty Information                                    | 0-1 |  |  |  |

|   | 0-8  | Safety Considerations                                   | 0-1 |  |  |  |

|   | 0-9. | Tools and Test Equipment Cross Reference                | 0-2 |  |  |  |

This manual is an authentication of the manufacturer's commercial literature which, through usage, has been found to cover the data required to operate and maintain this equipment, Since the manual was not prepared in accordance with military specifications, the format has not been structured to consider levels of maintenance.

## TABLE OF CONTENTS

| Section | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page                                                                          |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| I       | GENERAL INFORMATION         1-1.       Introduction         1-3.       Specifications         1-5.       Safety Considerations         1-7.       Instrument Identification         1-9.       Accessories         1-11.       Description         1-13.       Deleted                                                                                                                                                                                            | 1-1<br>1-3<br>1-3<br>1-3<br>1-3<br>1-3                                        |

|         | 1-15.       Service Equipment Available         1-17.       Recommended Test Equipment                                                                                                                                                                                                                                                                                                                                                                            |                                                                               |

| Ι       | INSTALLATION         2-1.       Introduction         2-3.       Unpacking and Inspection         2-5.       Installation Requirements         2-9.       Power Cable         2-11.       Operating Environment         2-15.       Storage and Shipment         2-16.       Environment         2-19.       Packaging         2-22.       Deleted         2-24.       Deleted         2-26.       Deleted         2-30.       Deleted         2-32.       Deleted | 2-1<br>2-1<br>. 2-2<br>. 2-3<br>. 2-3<br>. 2-3<br>. 2-3                       |

|         | <ul> <li>2-34. Deleted</li> <li>2-36. HP-IB Interconnections</li></ul>                                                                                                                                                                                                                                                                                                                                                                                            | . 2-4                                                                         |

| III     | OPERATION         3-1.       Introduction         3-3.       Operating Characteristics         3-5.       Operating Ranges         3-7.       Resolution Keys         3-10.       CHECK, DAC, and ENTER Keys         3-12.       FREQ Keys         3-14.       Automatic Mode         3-16.       Manual Mode         3-18.       Offset Frequencies         3-20.       Deleted                                                                                  | . 3-1<br>. 3-1<br>. 3-1<br>. 3-1<br>. 3-1<br>. 3-2<br>. 3-2<br>. 3-2<br>. 3-2 |

|         | 3-22.Deleted3-24.SET, RESET, RECALL, and CHS Keys3-26.SAMPLE RATE, GATE, and REMOTE3-30.AM Tolerance3-32.FM Tolerance3-34.Automatic Amplitude Discrimination3-36.Maximum Input Signal Power3-39.Input Cable Considerations                                                                                                                                                                                                                                        | . 3-3<br>. 3-3<br>. 3-3<br>. 3-3<br>. 3-3                                     |

| Section | Title                                                  | Page   |  |  |  |

|---------|--------------------------------------------------------|--------|--|--|--|

| Ш       | OPERATION (Continued)                                  |        |  |  |  |

|         | 3-41. Controls, Indicators, and Connectors             | . 3-4  |  |  |  |

|         | 3-43. Operating Procedures                             |        |  |  |  |

|         | 3-45. Operator Key board Check                         |        |  |  |  |

|         | 3-47. Error Code Displays                              |        |  |  |  |

|         | 3-49. Instrument Error Displays                        | 3-14   |  |  |  |

|         | 3-51. Operator Error Displays                          | 3-15   |  |  |  |

|         | 3-53. Limit Errors and Sequence Errors                 | 3-16   |  |  |  |

|         | 3-57. Deleted                                          |        |  |  |  |

|         | 3-59. Time Base                                        | . 3-16 |  |  |  |

|         | 3-61. Deleted                                          |        |  |  |  |

|         | 3-63. Deleted                                          |        |  |  |  |

|         | 3-65. HP-IB Interface                                  | 3-16   |  |  |  |

|         | 3-67. Deleted                                          |        |  |  |  |

|         | 3-69. HP-IB Programming                                |        |  |  |  |

|         | 3-79. 9825A Program Examples                           |        |  |  |  |

|         | 3-81. HP-IB Programming Notes                          | 3-25   |  |  |  |

|         | 3-83. Deleted                                          |        |  |  |  |

| lv      | PERFORMANCE TESTS                                      | . 4-1  |  |  |  |

|         | 4-1. Introduction                                      | . 4-1  |  |  |  |

|         | 4-3. Operational Verification                          | . 4-1  |  |  |  |

|         | 4-5. Complete Performance Test.                        | . 4-1  |  |  |  |

|         | 4-7. Equipment Required                                | . 4-1  |  |  |  |

|         | 4-9. Test Record                                       |        |  |  |  |

|         | 4-11. Operational Verification Procedures              |        |  |  |  |

|         | 4-12. Self-Check                                       |        |  |  |  |

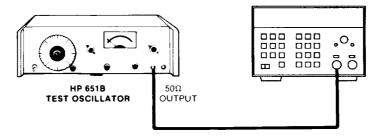

|         | 4-13. 10 Hz—500MHz input Sensitivity Test, 50 W /1 Mel | . 4-2  |  |  |  |

|         | 4-14. Deleted                                          |        |  |  |  |

|         | 4-15. Deleted                                          |        |  |  |  |

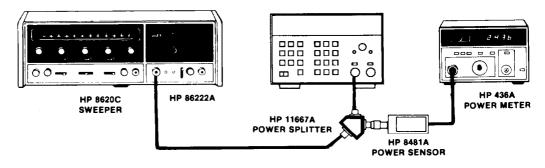

|         | 4-16. 500 MHz-18 GHz Input Sensitivity Test            | . 4-3  |  |  |  |

|         | 4-17. Deleted                                          |        |  |  |  |

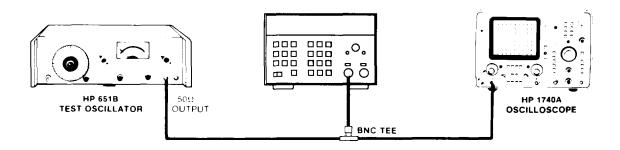

|         | 4-18. 500 MHz—18 GHz High Level Test                   | 4-4    |  |  |  |

|         | 4-19. HP-IB Verification Program.                      |        |  |  |  |

|         | 4-27. Deleted                                          |        |  |  |  |

|         | 4-28. Performance Test Procedures                      | 4-13   |  |  |  |

|         | 4-29. 10 Hz—500MHz Input Sensitivity Test, 50 $\Omega$ | 4-13   |  |  |  |

|         | 4-30. 10 Hz—500MHz Input Sensitivity Test, 1M $\Omega$ | 4-14   |  |  |  |

|         | 4-31. 500 MHz-18 GHz Input Sensitivity Test            |        |  |  |  |

|         | 4-32. Deleted                                          |        |  |  |  |

|         | 4-33. Deleted                                          |        |  |  |  |

|         | 4-34. FM Tolerance Test                                |        |  |  |  |

|         | 4-35. Automatic Amplitude Discrimination Test          | 4-18   |  |  |  |

| Section | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Page                                                                      |  |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|--|

| lv      | PERFORMANCE TESTS (Continued)<br>4-36. Deleted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                           |  |  |

|         | 4-37. Deleted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                           |  |  |

|         | 4-38. Deleted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                           |  |  |

|         | 4-39. Deleted<br>4-40. Deleted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                           |  |  |

| V       | ADJUSTMENTS         5-1.       Introduction         5-4.       Equipment Required         5-6.       Factory Selected Components         5-8.       Adjustment Locations         5-10.       Safety Considerations         5-12.       Adjustment Procedures         5-13.       Power Supply Adjustments         5-14.       Adjustment Procedures         5-15.       Power Supply Adjustments         5-16.       Safety Considerations         5-17.       Main Synthesizer Adjustment         5-19.       Offset Synthesizer Adjustments         5-21.       IF Adjustment         5-28.       Direct Count Adjustment         5-30.       Oscillator Adjustments         5-31.       Deleted         5-32.       Oven Oscillator         5-33.       Deleted         5-34.       Deleted         5-39.       Deleted         5-39.       Deleted         5-40.       Deleted         5-41.       Deleted | 5-1<br>5-1<br>5-1<br>5-1<br>5-3<br>5-3<br>5-3<br>5-5<br>5-9<br>5-9<br>5-9 |  |  |

| VI      | DELETED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                           |  |  |

VI

VII DELETED

| VIII | SERV | 'ICE                                                    |

|------|------|---------------------------------------------------------|

|      | 8-1. | Introduction                                            |

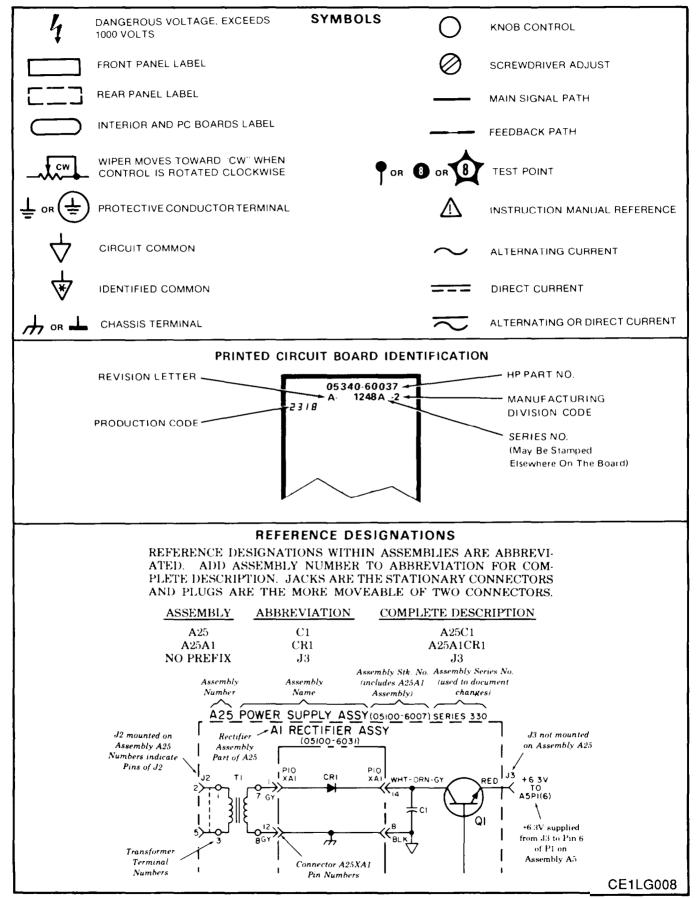

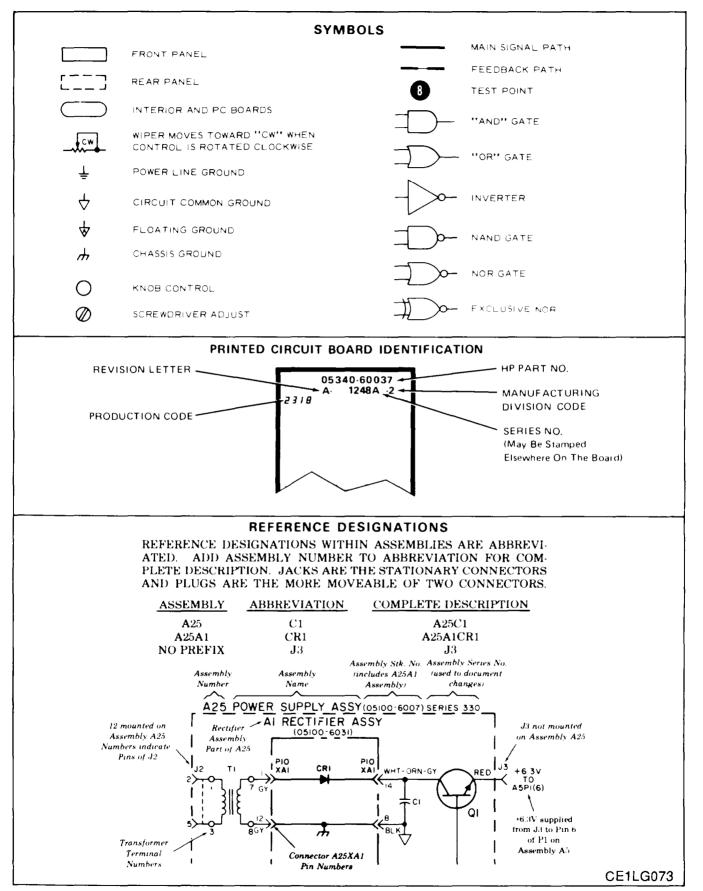

|      | 8-3. | Schematic Diagram Symbols and Reference Designators 8-1 |

|      | 8-5. | Reference Designations 8-1                              |

| Section | Title               | Page                                                                             |  |  |  |  |

|---------|---------------------|----------------------------------------------------------------------------------|--|--|--|--|

| VIII    | SERVICE (Continued) |                                                                                  |  |  |  |  |

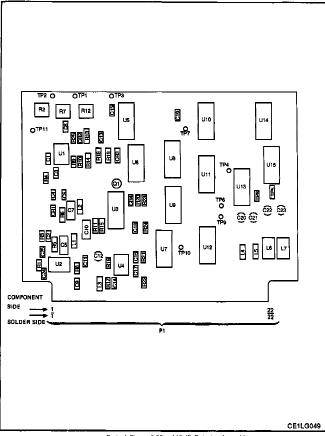

|         | 8-7.                | Identification Markings on Printed-Circuit Boards 8-2                            |  |  |  |  |

|         | 8-11.               | Assembly Identification                                                          |  |  |  |  |

|         | 8-13.               | Safety Considerations                                                            |  |  |  |  |

|         | 8-18.               | Safety Symbols                                                                   |  |  |  |  |

|         | 8-20.               | Signal Names                                                                     |  |  |  |  |

|         | 8-22.               | Disassembly and Reassembly 8-12                                                  |  |  |  |  |

|         | 8-24.               | Top Cover Removal                                                                |  |  |  |  |

|         | 8-26.               | Bottom Cover Removal8-12                                                         |  |  |  |  |

|         | 8-28.               | Front Frame Removal                                                              |  |  |  |  |

|         | 8-30.               | Removal of A1 Display Assembly and A2 Display<br>Assembly from Front Panel Frame |  |  |  |  |

|         | 8-32.               | Replacement of LED's in Front Panel Switches                                     |  |  |  |  |

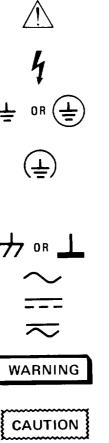

|         | 8-34.               | Removal of U1 Sampler, A25 Preamplifier, and A26 Sampler Driver                  |  |  |  |  |

|         | 8-36.               | Factory Selected Components                                                      |  |  |  |  |

|         | 8-38.               | Procedure for Selecting Resistor R15 on                                          |  |  |  |  |

|         | 0 00.               | Direct Count Amplifier                                                           |  |  |  |  |

|         | 8-40.               | Procedure for Selecting Resistor R16 for Capacitor C10                           |  |  |  |  |

|         |                     | on Direct Count Amplifier A3                                                     |  |  |  |  |

|         | 8-42.               | Procedures for Selecting Resistor R16 on<br>Main Loop Amplifier A9               |  |  |  |  |

|         | 8-44.               | Deleted                                                                          |  |  |  |  |

|         | 8-46.               | Service Accessory Kit 10842A8-18                                                 |  |  |  |  |

|         | 8-48.               | Equipment Supplied                                                               |  |  |  |  |

|         | 8-50.               | Replaceable Parts                                                                |  |  |  |  |

|         | 8-52.               | Using ExtenderBoard 05342-60036                                                  |  |  |  |  |

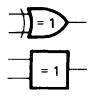

|         | 8-58.               | Logic Symbols                                                                    |  |  |  |  |

|         | 8-60.               | Logic Concepts                                                                   |  |  |  |  |

|         | 8-62.               | Negation                                                                         |  |  |  |  |

|         | 8-64.               | Logic implementation and Polarity Indication 8-23                                |  |  |  |  |

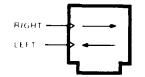

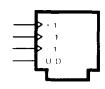

|         | 8-73.               | Other Symbols                                                                    |  |  |  |  |

|         | 8-75.               | Dependency Notation "C" "G" "V" 'F"                                              |  |  |  |  |

|         | 8-77.               | Control Blocks                                                                   |  |  |  |  |

|         | 8-79.               | Complex Logic Devices                                                            |  |  |  |  |

|         | 8-81.               | Theory of Operation                                                              |  |  |  |  |

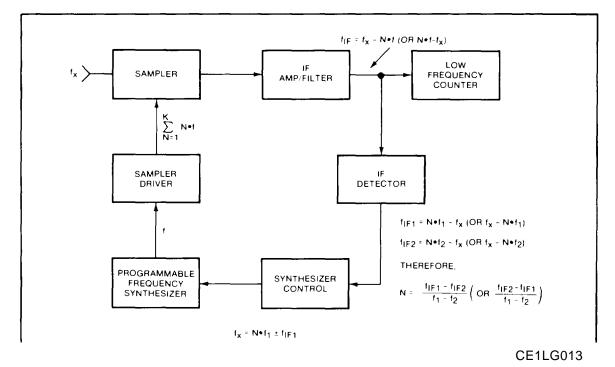

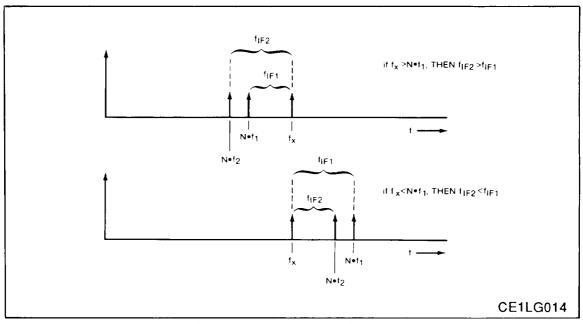

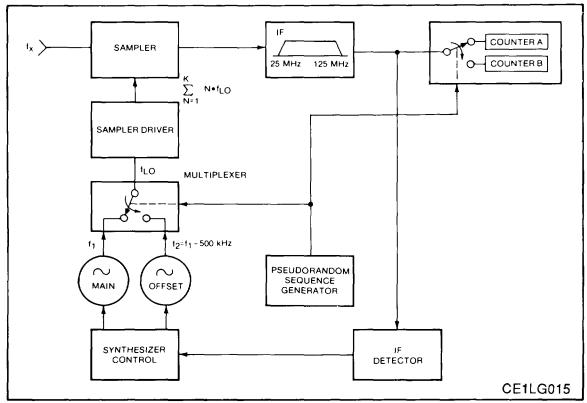

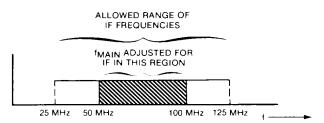

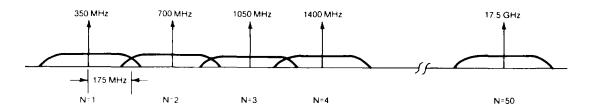

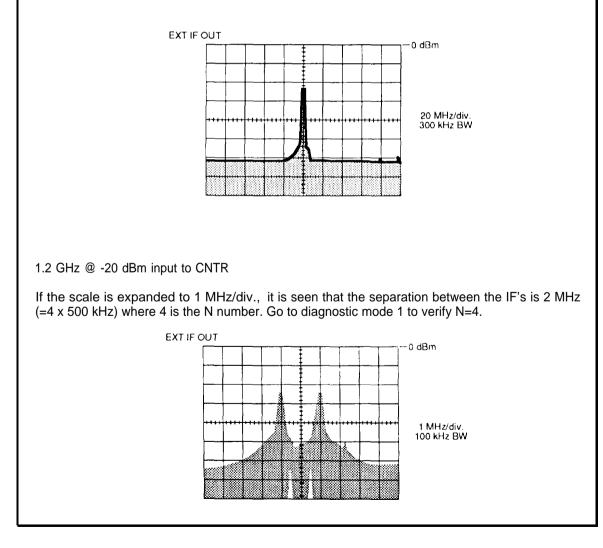

|         | 8-83.               | Harmonic Heterodyne Technique 8-36                                               |  |  |  |  |

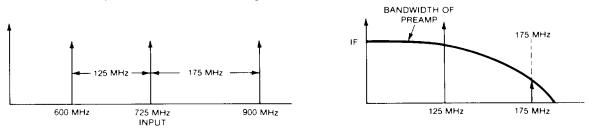

|         | 8-94.               | HP 5342A Overall Operation 8-39                                                  |  |  |  |  |

|         | 8-99.               | FM Tolerance                                                                     |  |  |  |  |

|         | 8-101.              | Automatic Amplitude Discrimination                                               |  |  |  |  |

|         | 8-105.              | Sensitivity                                                                      |  |  |  |  |

|         | 8-110.              | HP 5342A Block Diagram Description                                               |  |  |  |  |

|         | 8-112.              | Direct Count Section                                                             |  |  |  |  |

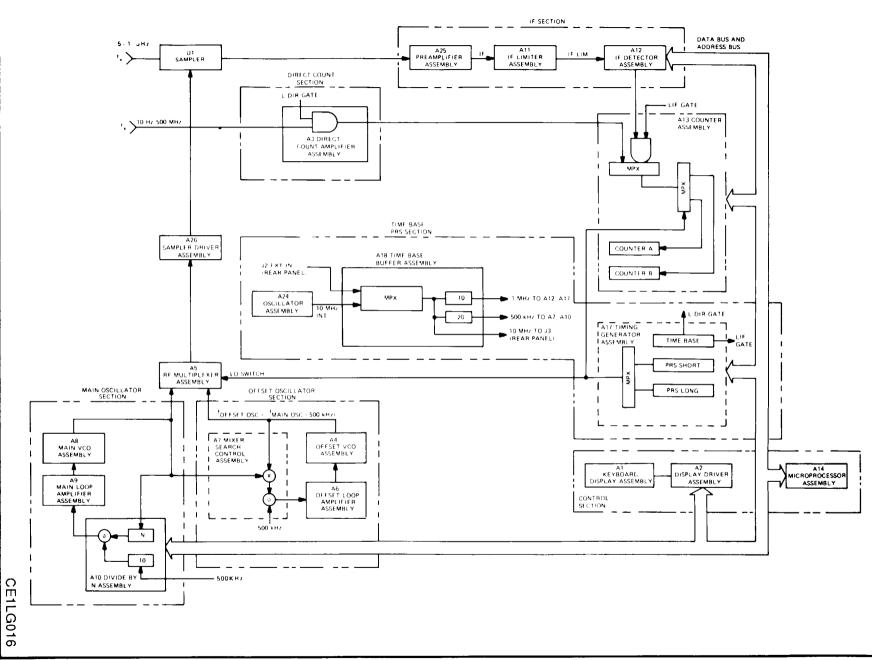

|         | 8-114.              | Synthesizer Section 8-42                                                         |  |  |  |  |

|         | 8-116.              | Main Loop Operation                                                              |  |  |  |  |

|         | 8-120.              | Offset Loop Operation 8-43                                                       |  |  |  |  |

|         | 8-124.              | IF Section                                                                       |  |  |  |  |

|         | 8-126.              | Time Base/PSRSection                                                             |  |  |  |  |

|         | 8-128.              | Control Section                                                                  |  |  |  |  |

|         | 8-130.              | Detailed Theory of Operation8-46                                                 |  |  |  |  |

| Section | Title            | Page                                                                                         |

|---------|------------------|----------------------------------------------------------------------------------------------|

|         | VIII             | SERVICE (Continued)                                                                          |

|         | 8-132.           | Al Display Assembly and A2 Display Driver Assembly 8-46                                      |

|         | 8-138.           | Key board Operation                                                                          |

|         | 8-145.           | A3 Direct Count Amplifier Assembly                                                           |

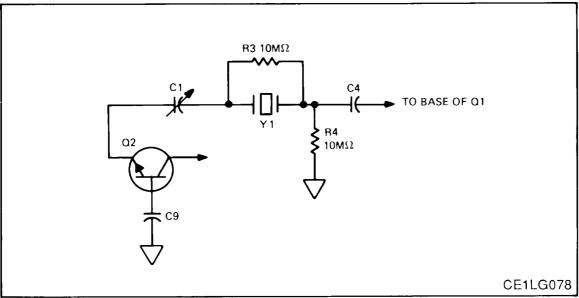

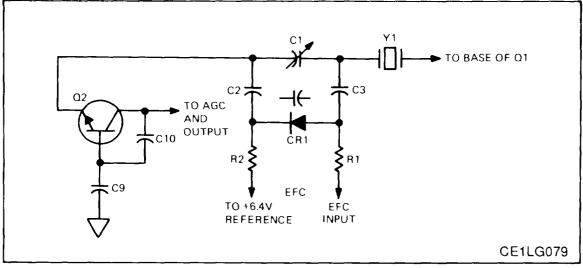

|         | 8-152.           | A4 Offset VCO                                                                                |

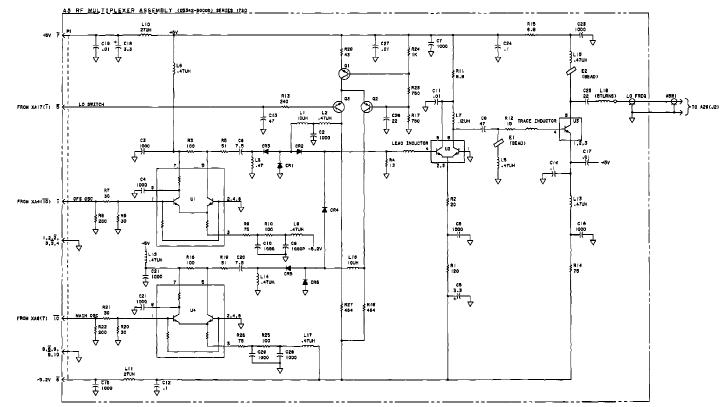

|         | 8-154.           | A5 RF Multiplexer Assembly                                                                   |

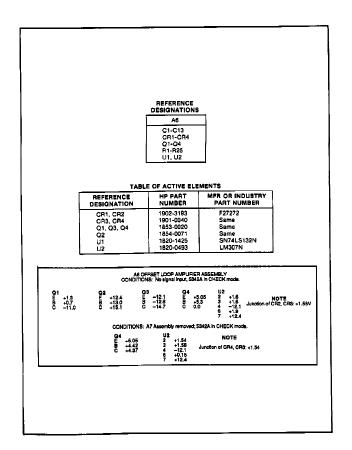

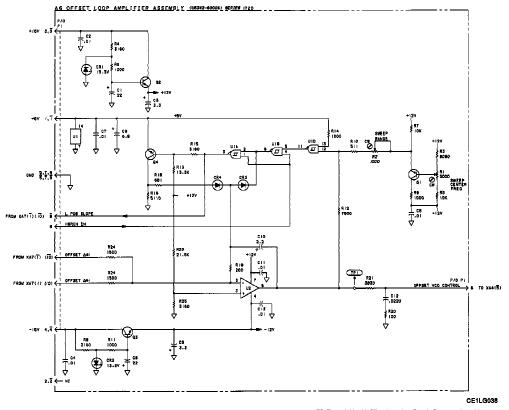

|         | 8-158.           | A6 Offset Loop Amp/Search Generator Assembly                                                 |

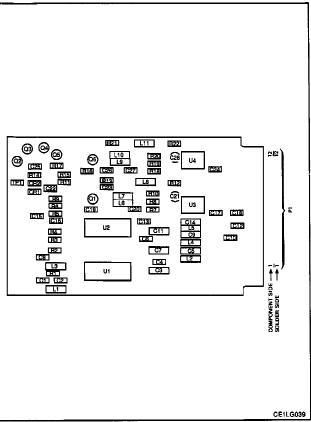

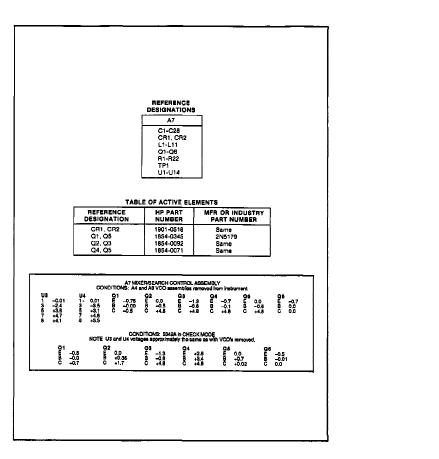

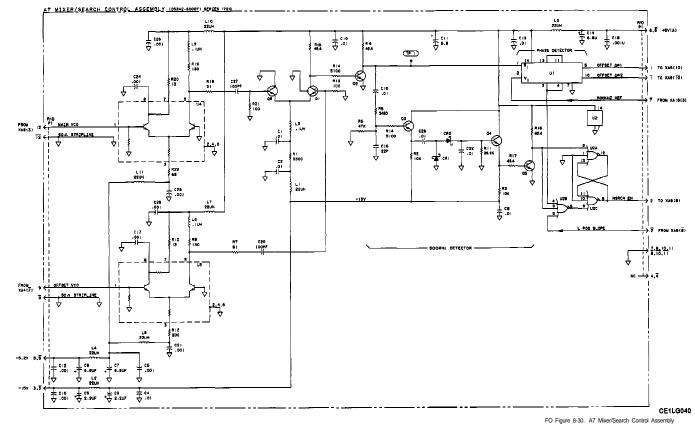

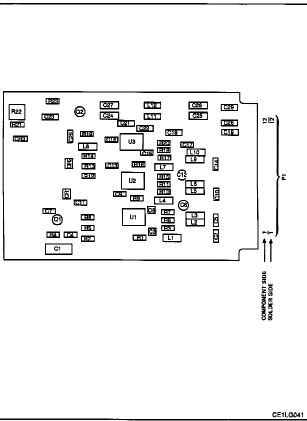

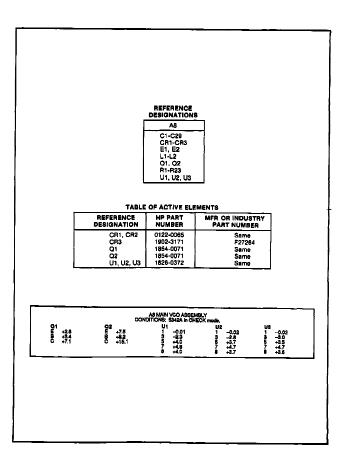

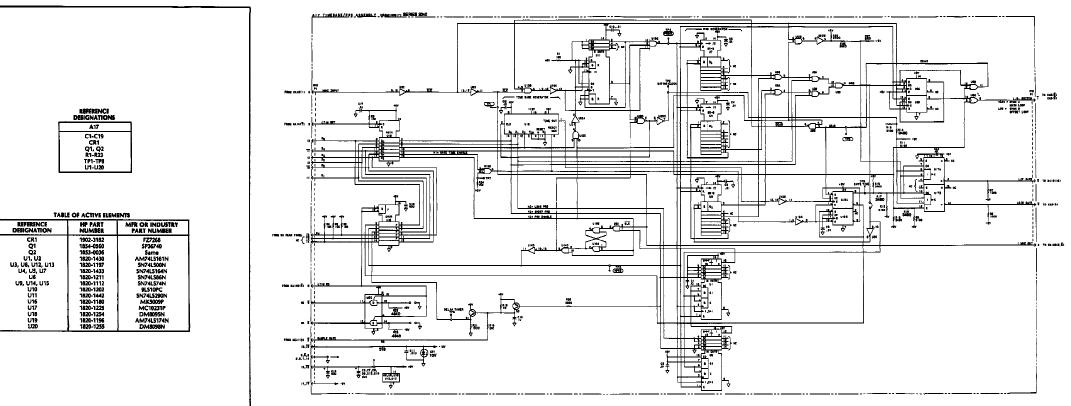

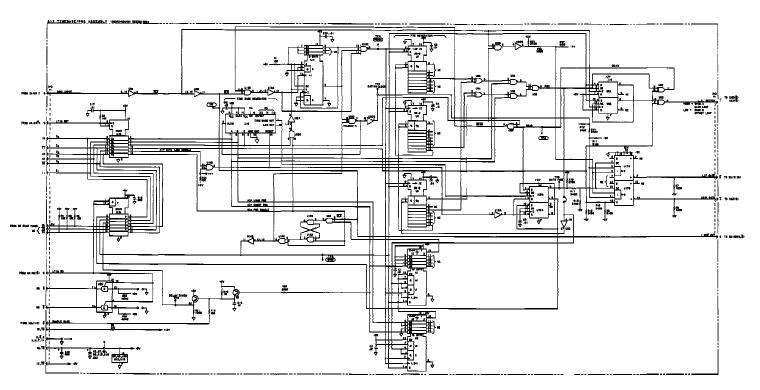

|         | 8-166.           | A7 Mixer/Search Control Assembly                                                             |

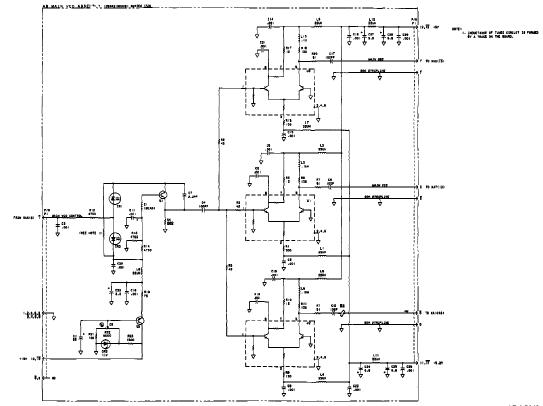

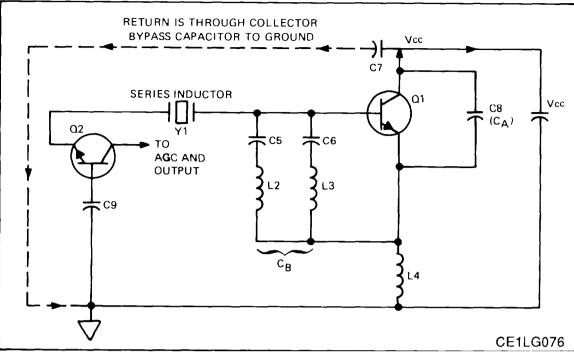

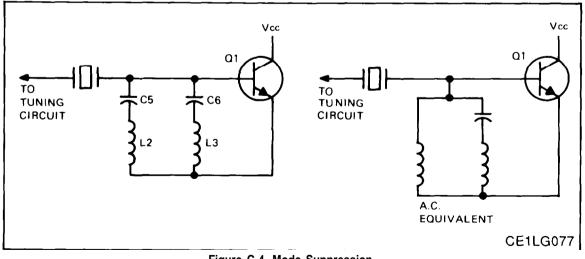

|         | 8-172.           | A8 Main VCO Assembly                                                                         |

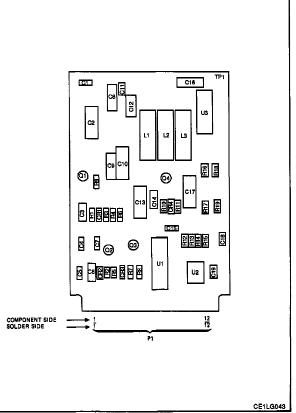

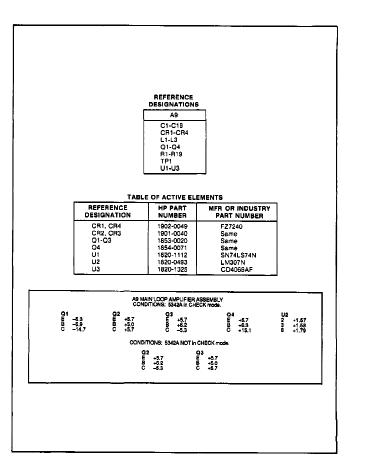

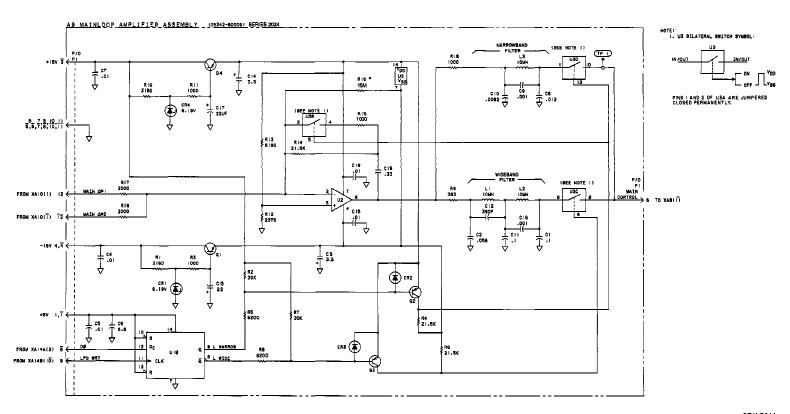

|         | 8-176.           | A9 Main Loop Amplifier Assembly8-53                                                          |

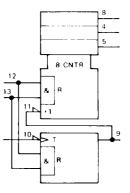

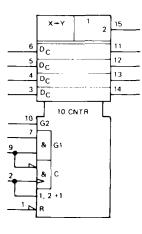

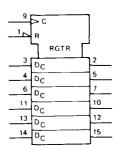

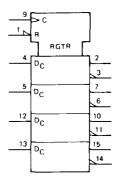

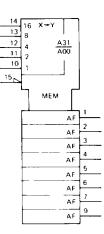

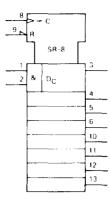

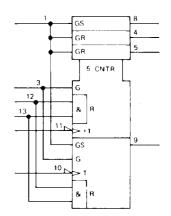

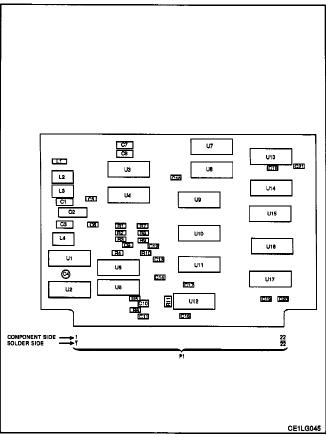

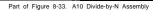

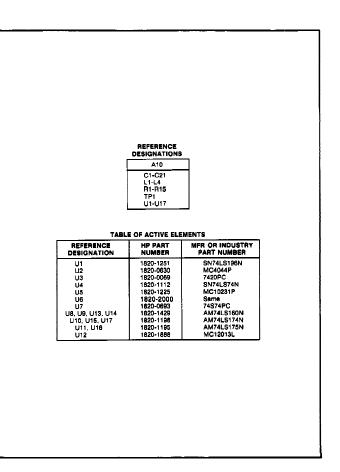

|         | 8-181.           | A10 Divide-by-N Assembly                                                                     |

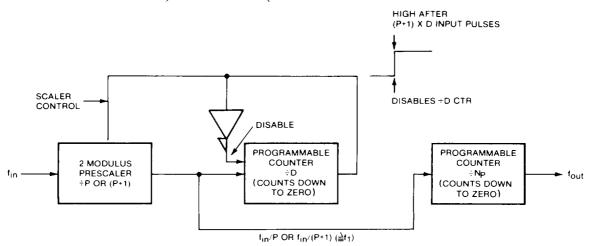

|         | 8-190.           | Two Modulus Prescaler Technique                                                              |

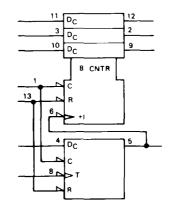

|         | 8-198            | Counter (Divider) Chain Utilizing 9's Complement 8-56                                        |

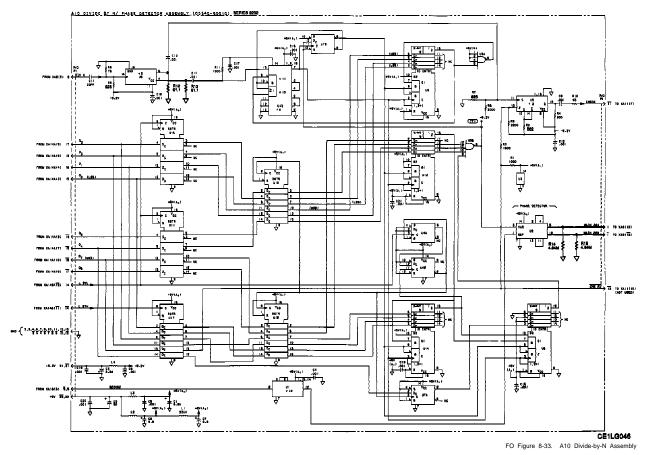

|         | 8-202.           | All IF Limiter Assembly                                                                      |

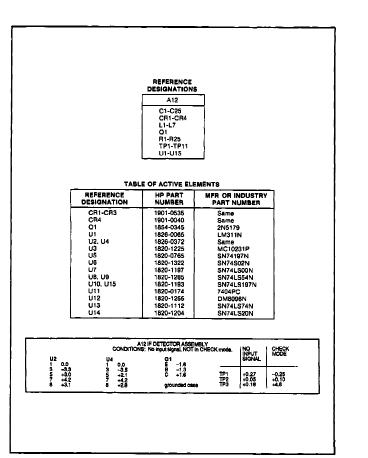

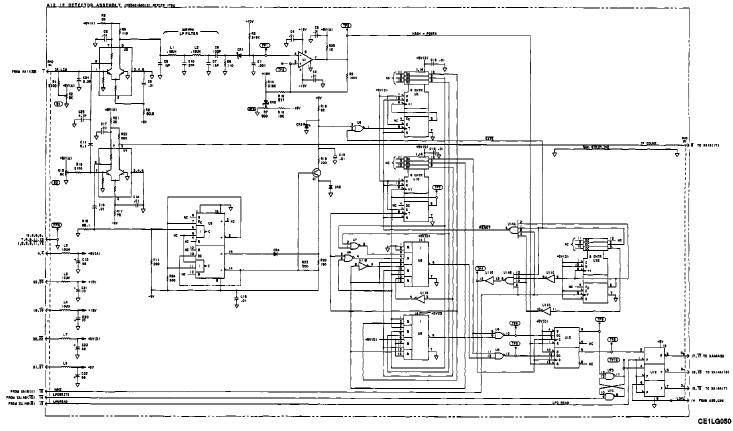

|         | 8-206.           | A12 IF Detector Assembly                                                                     |

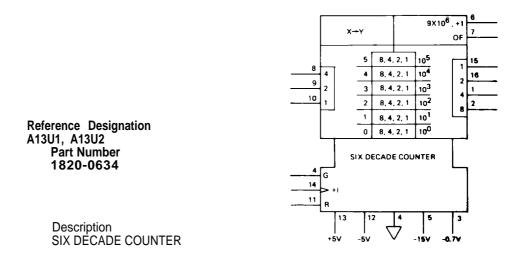

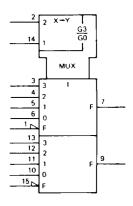

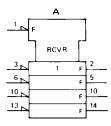

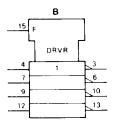

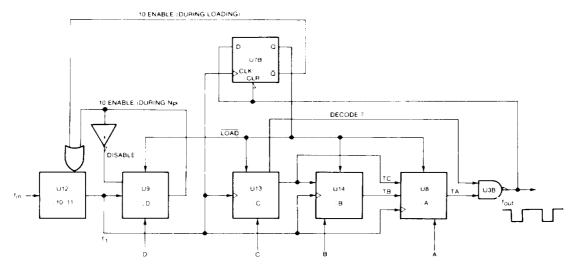

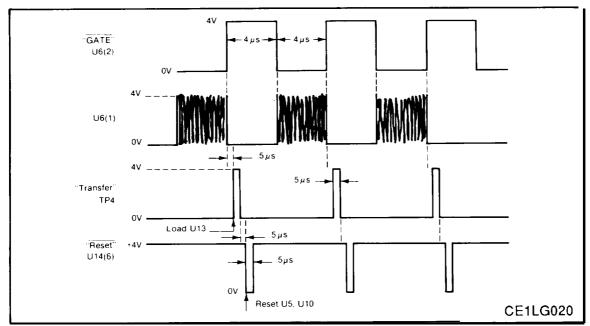

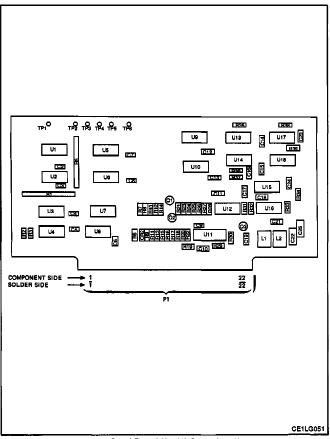

|         | 8-215.           | A13 Counter Assembly                                                                         |

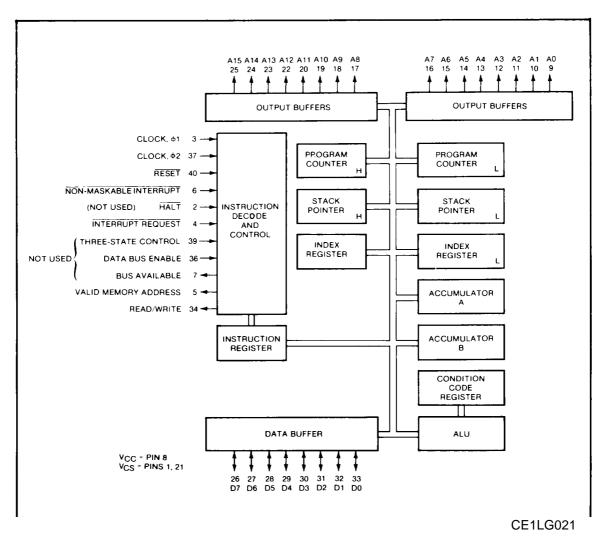

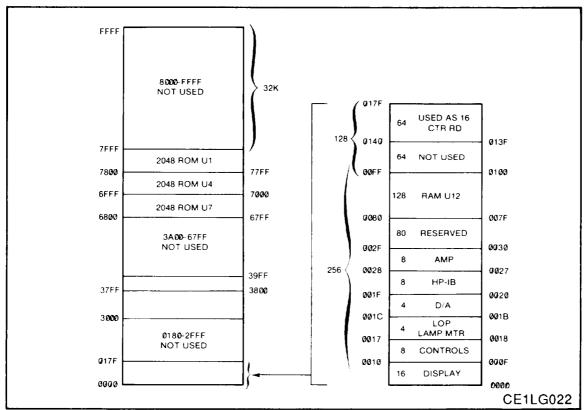

|         | 8-225.           | A14 Microprocessor Assembly                                                                  |

|         | 8-228.           | Microprocessor Operation                                                                     |

|         | 8-240.           | HP-IB Assembly                                                                               |

|         | 8-242.           | Deleted                                                                                      |

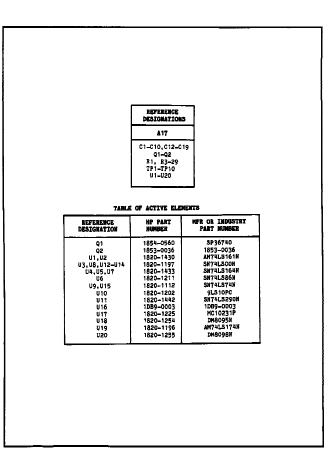

|         | 8-244.           | A17 Timing Generator Assembly                                                                |

|         | 8-247.           | Pseudorandom Sequence Generation                                                             |

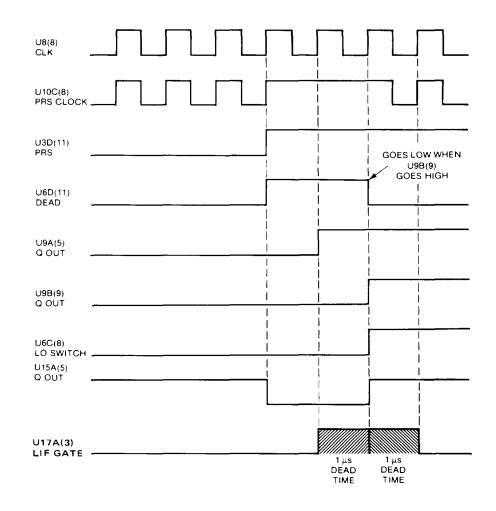

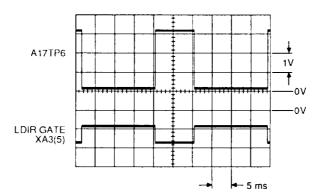

|         | 8-257.           | Gate Time Generation                                                                         |

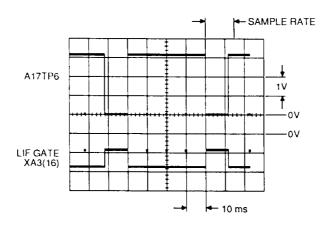

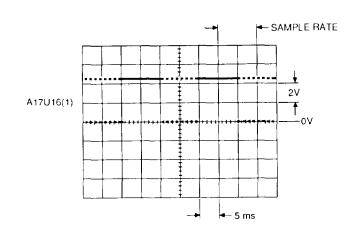

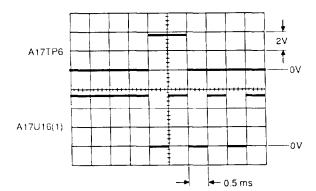

|         | 8-262.           | Sample Rate Generation                                                                       |

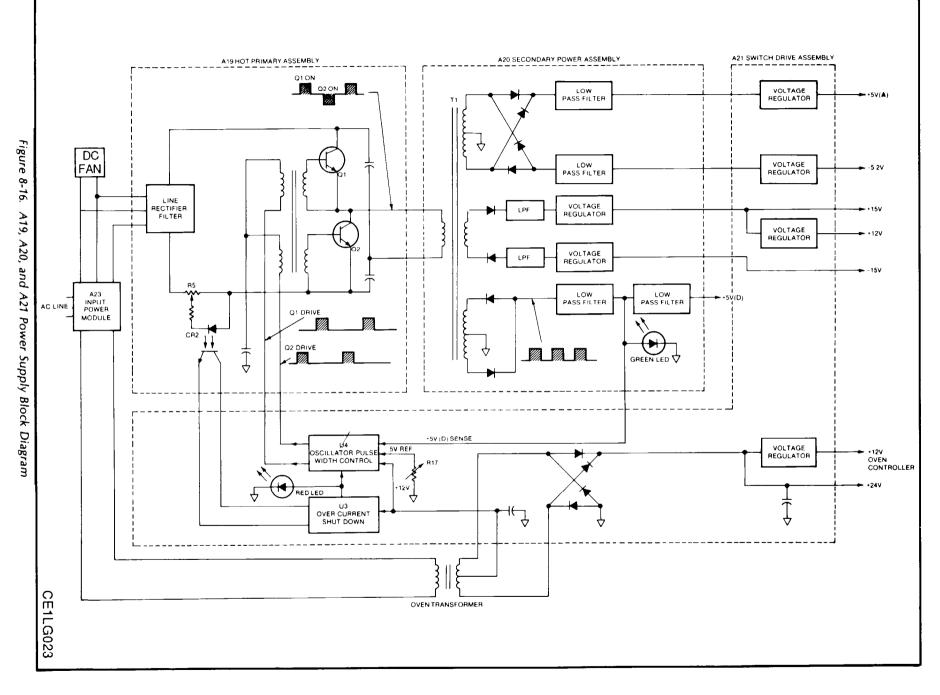

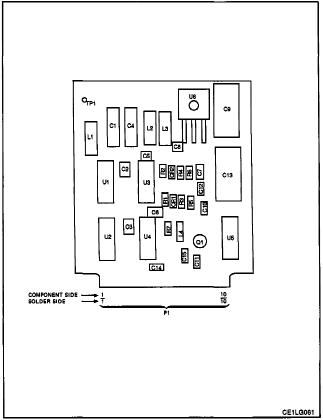

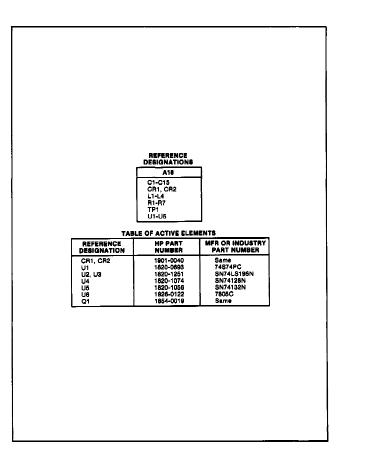

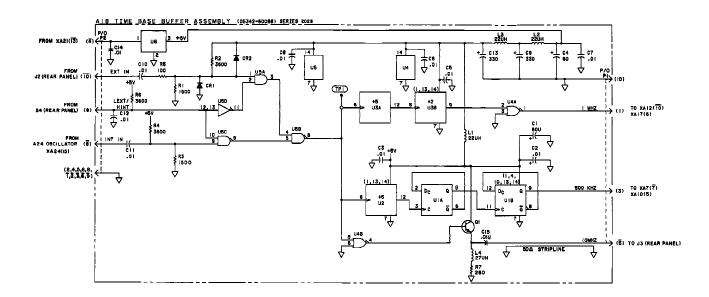

|         | 8-266.<br>8-269. | A18 Time Base Buffer Assembly         8-68           A19, A20, A21 Power Supply         8-69 |

|         | 8-209.<br>8-278. | A22 Motherboard                                                                              |

|         | 8-280.           | A22 Modifier Doald                                                                           |

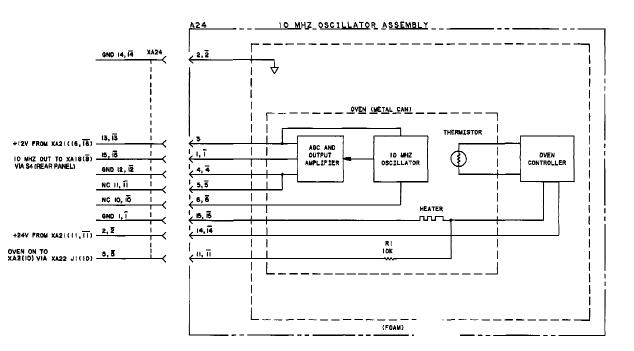

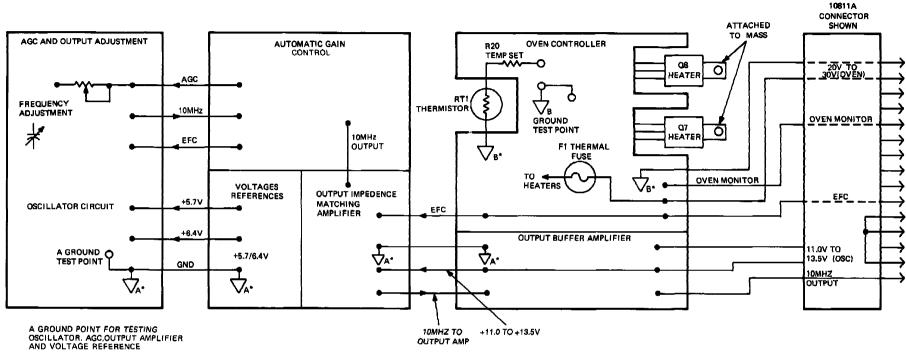

|         | 8-282.           | A24 Oscillator Assembly                                                                      |

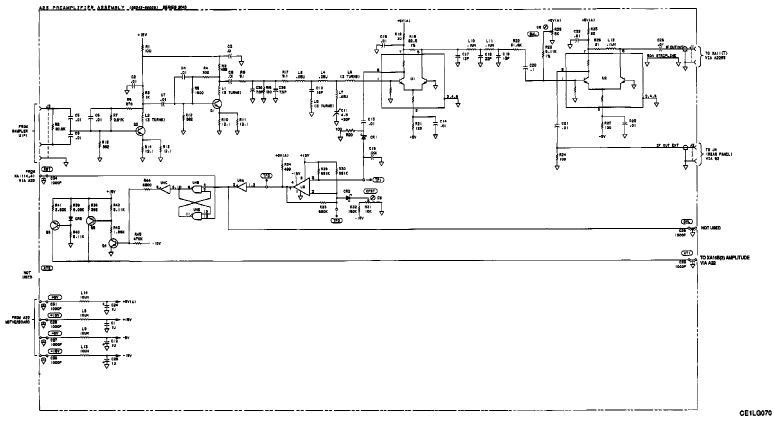

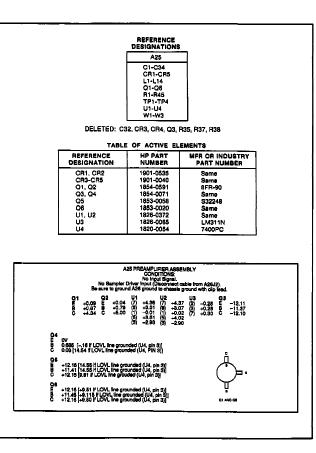

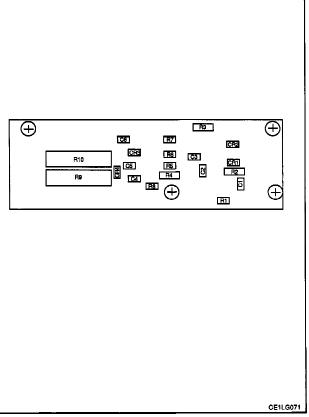

|         | 8-284.           | A25 Preamplifier                                                                             |

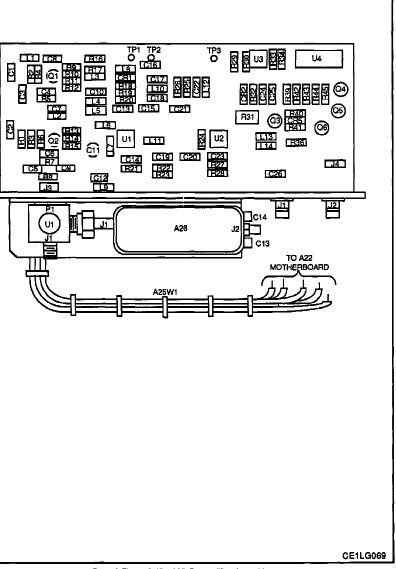

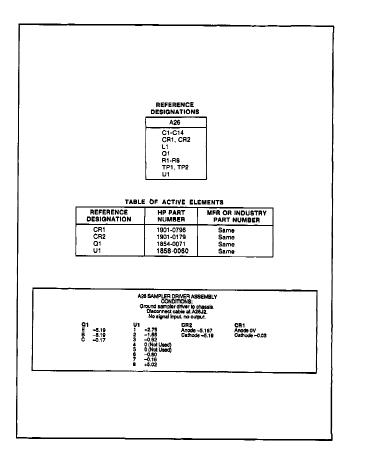

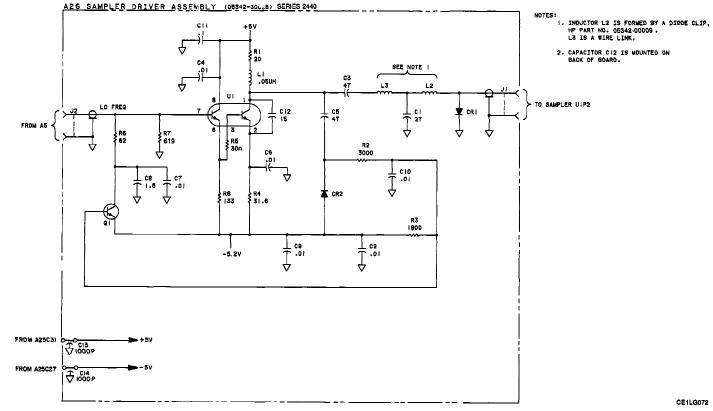

|         | 8-290.           | A26 Sampler Driver Assembly                                                                  |

|         | 8-294.           | Deleted                                                                                      |

|         | 8-296.           | Deleted                                                                                      |

|         | 8-297.           | Deleted                                                                                      |

|         | 8-300.           | Deleted                                                                                      |

|         | 8-305.           | Deleted                                                                                      |

|         | 8-306.           | Deleted                                                                                      |

|         | 8-310.           | Deleted                                                                                      |

|         | 8-314.           | Deleted                                                                                      |

|         | 8-331.           | Deleted                                                                                      |

|         | 8-340.           |                                                                                              |

|         | 8-346.           | Hewlett-Packard interface Bus(HP-IB)                                                         |

|         | 8-347.           | Introduction                                                                                 |

|         | 8-349.           | Interface Registers                                                                          |

|         | 8-358.           | Command Decoding ROM's                                                                       |

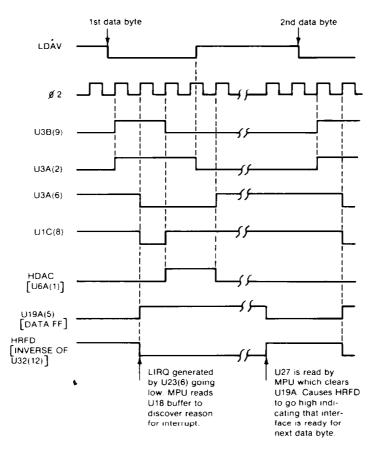

|         | 8-366.<br>8 260  | Acceptor Handshake                                                                           |

|         | 8-369.<br>8-372. | Source Handshake                                                                             |

|         | 8-372.<br>8-374. | Troubleshooting to the Assembly Level (Standard instrument) 8-78                             |

|         | 8-374.<br>8-375. | Troubleshooting Technique                                                                    |

|         | 8-379.           | Recommended Test Equipment                                                                   |

|         |                  |                                                                                              |

| Section   | Title   |                                                    | Page |

|-----------|---------|----------------------------------------------------|------|

| APPENDIX  | A REFEF | RENCES                                             |      |

|           | A-1.    | Scope                                              | A-1  |

|           | A-2.    | Forms                                              | A-1  |

|           | A-3.    | Technical Manuals                                  | A-1  |

|           | A-4.    | Miscellaneous                                      | A-1  |

| APPENDIX  | B MAINT | ENANCE ALLOCATION                                  |      |

| Section I | INTRO   | DUCTION                                            | B-1  |

|           | B-1.    | General                                            | B-1  |

|           | B-2.    | Maintenance Functions                              | B-1  |

|           | B-3.    | Explanation of Columns in MAC, Sectional           | B-2  |

|           | B-4.    | Explanation of Columns in Tool and Test Equipment, |      |

|           |         | Requirements, Section III                          | B-3  |

|           | B-5.    | Explanation of Columns in Remarks, Section IV      | B-3  |

|           | MAINT   | ENANCE ALLOCATION CHART                            | B-4  |

| III       | TOOL    | AND TEST EQUIPMENT REQUIREMENTS                    | B-5  |

| IV        | REMA    | RKS                                                | B-6  |

| APPENDIX  | CA24 O  | SCILLATOR REPAIR                                   |      |

| I         | INTRO   |                                                    | C-1  |

|           | C-1.    | Scope                                              | C-1  |

|           | C-3.    | General                                            | C-1  |

| Ш         | ADJU    | STMENTS                                            | C-1  |

|           | C-5.    |                                                    | C-1  |

| Ш | SERVICE |                                                     |      |  |

|---|---------|-----------------------------------------------------|------|--|

|   | C-6.    | Introduction                                        | C-1  |  |

|   | C-8.    | Schematic Diagram Symbols and Reference Designators | C-1  |  |

|   | C-10.   | Reference Designators                               | C-1  |  |

|   | C-11.   | Theory of Operation                                 | C-1  |  |

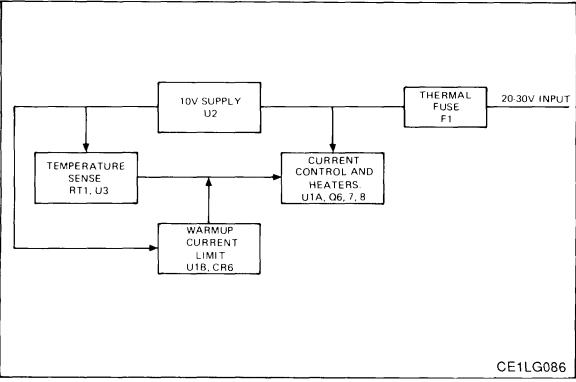

|   | C-13.   | Overall Block Diagram Theory                        | C-4  |  |

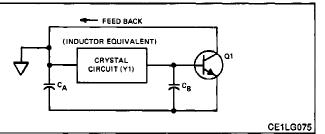

|   | C-18.   | Main Oscillator Theory of Operation                 | C-4  |  |

|   | C-23.   | Electronic Frequency Control (EFC)                  | C-6  |  |

|   | C-25.   | Automatic Gain Control (AGC)                        | C-7  |  |

|   | C-28.   | RF Output impedance Matching and Output Buffer      | C-8  |  |

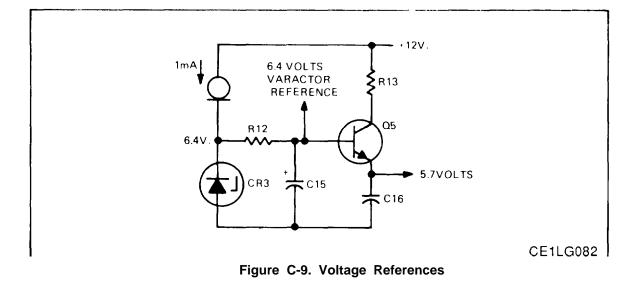

|   | C-30.   | Voltage References (5.7V and 6.4V)                  | C-8  |  |

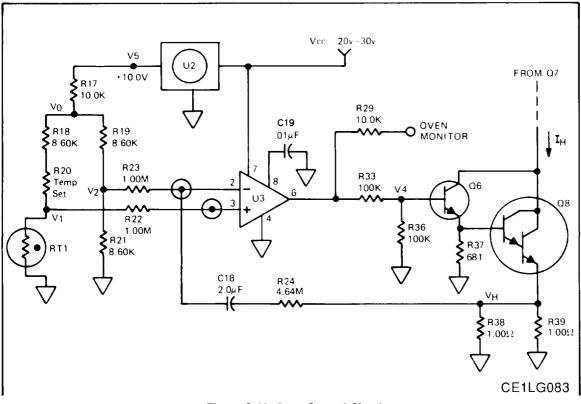

|   | C-32.   | Oven Heater and Controller Theory                   | C-9  |  |

|   | C-40.   | Precision Voltage Reference                         | C-10 |  |

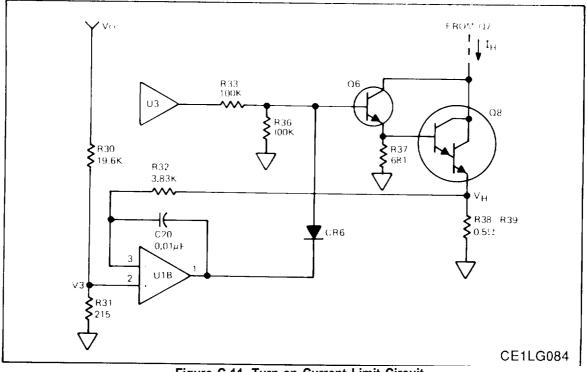

|   | C-42.   | Oven Controller Turn-On Current Limiting            | C-10 |  |

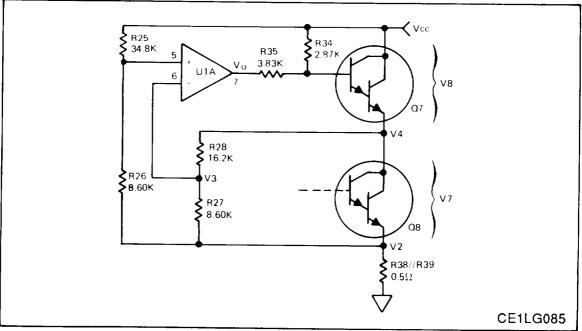

|   | C-44.   | Heater Transistor Balance                           | C-11 |  |

|   | C-46.   | Repair and Troubleshooting                          | C-12 |  |

|   | C-47.   | Inspection                                          | C-12 |  |

| Section | Title | Page                                           |

|---------|-------|------------------------------------------------|

|         | C-49. | Repair                                         |

|         | C-50. | Printed Circuit Component Replacement          |

|         | C-52. | Replacing Integrated Circuits C-12             |

|         | C-55. | Troubleshooting                                |

|         | C-62. | Disassembly for Troubleshooting and RepairC-14 |

|         | C-66. | Special Parts Replacement Considerations       |

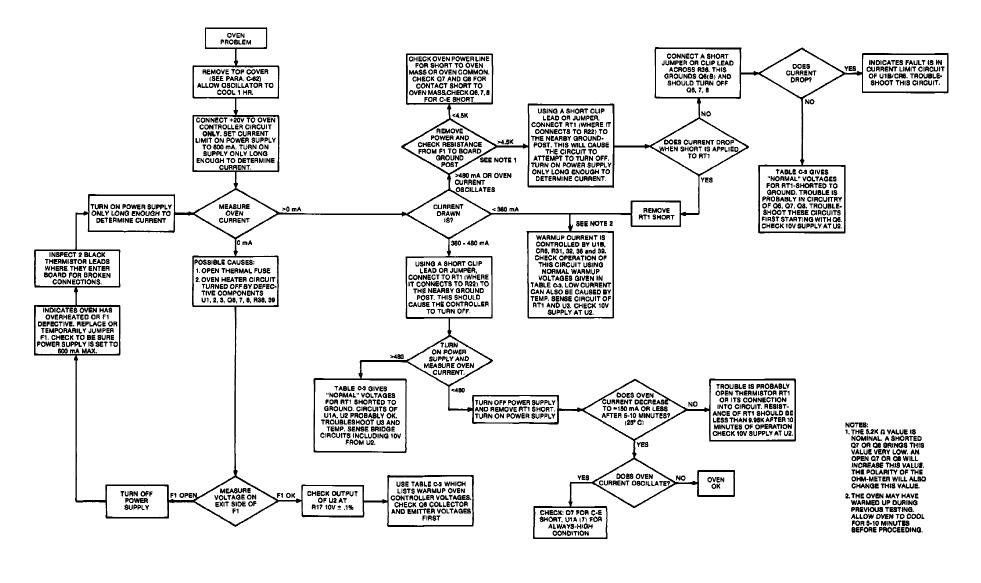

|         | C-68. | Öven Controller Troubleshooting C-16           |

|         | C-69. | General                                        |

|         | C-73. | Normal Operation                               |

|         | C-75. | Troubleshooting                                |

|         | C-79. | Troubleshooting Cautions C-I7                  |

|         | C-81. | Flex Damage                                    |

|         | C-83. | Oscillator Troubleshooting C-20                |

|         | C-85. | Normal Operation                               |

|         | C-87. | Oscillator Troubleshooting Techniques C-20     |

|         | C-90. | Helpful Hints                                  |

|         | C-91. | Troubleshooting Information C-21               |

## LIST OF FIGURES

| Figure               | Title                                                    | Page     |

|----------------------|----------------------------------------------------------|----------|

| 1-1.                 | Model 5342A Microwave Frequency Counter                  | 1-1      |

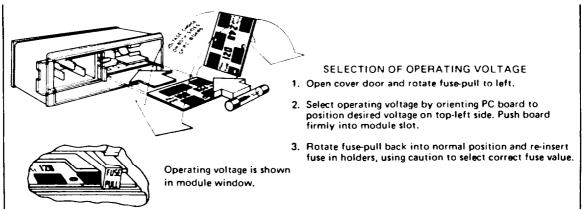

| 2-1.                 | Line Voltage Selection                                   | 2-1      |

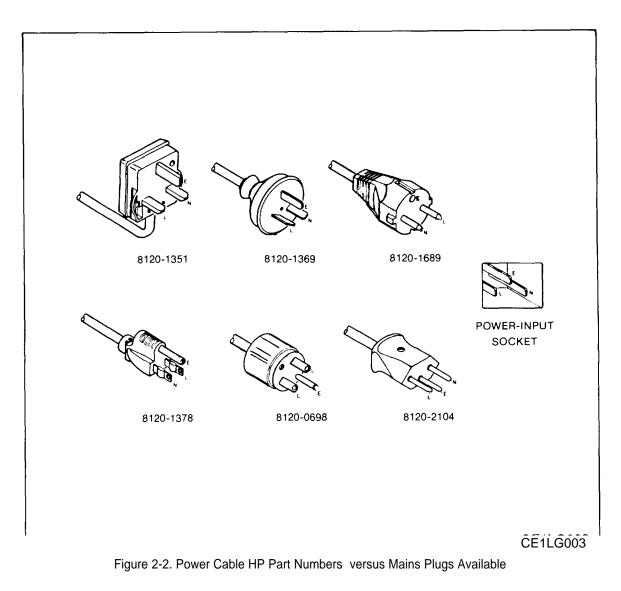

| 2-2.                 | Power Cable HP Part Numbers versus Mains Plugs Available | 2-2      |

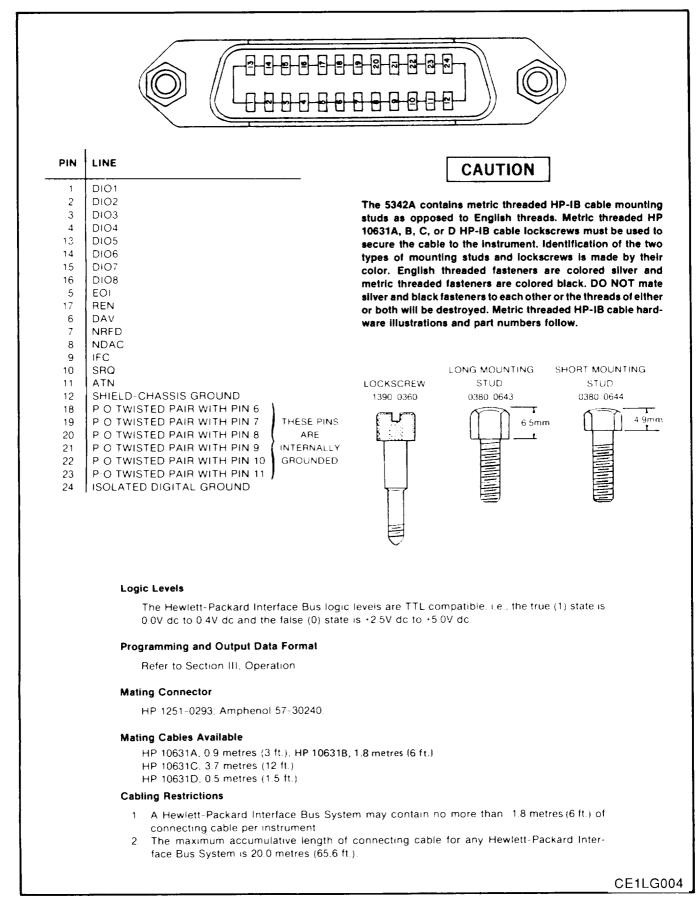

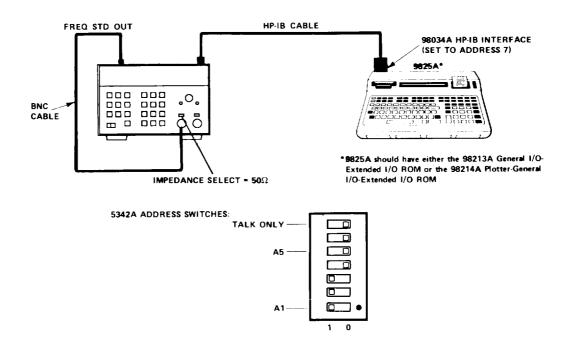

| 2-3.                 | Hewlett-Packard Interface Bus Connection                 | 2-5      |

| 3-1.                 | Front Panel Controls and Indicators                      | 3-5      |

| 3-2.                 | Rear Panel Controls and Connectors                       |          |

| 3-3.                 | Operating Procedures                                     |          |

| 3-4.                 | Deleted                                                  |          |

| 3-5.                 | Deleted                                                  |          |

| 8-1.                 | Schematic Diagram Notes                                  | 8-3      |

| 8-2.                 | Front Frame, A25, A26, and U1 Removable                  |          |

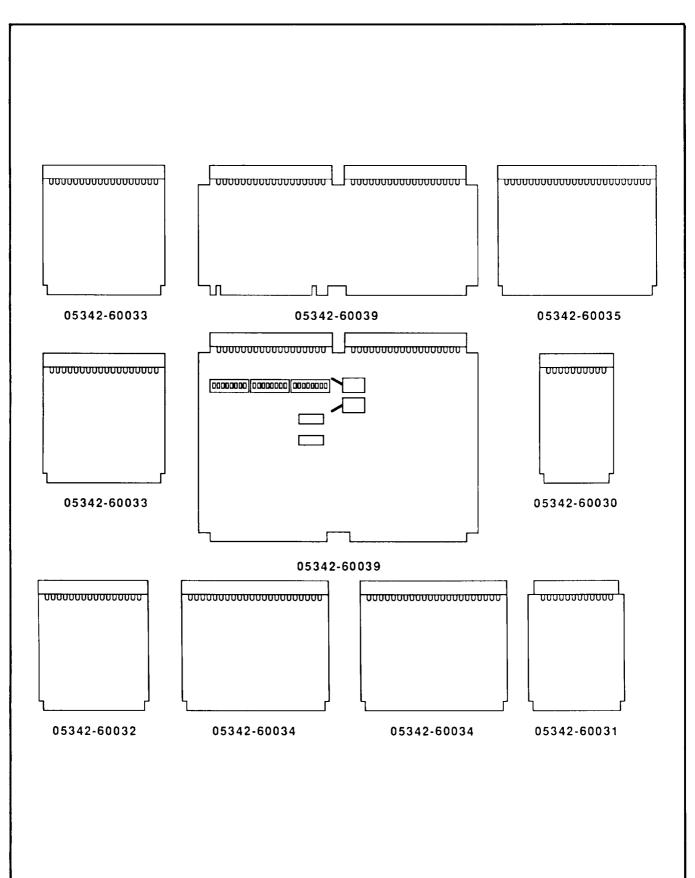

| 8-3.                 | 10842A Service Accessory Kit                             |          |

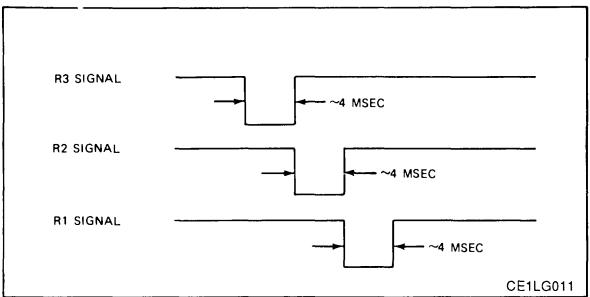

| 8-4.                 | Extender Board (05342-60036) Test Points R1, R2, and R3  |          |

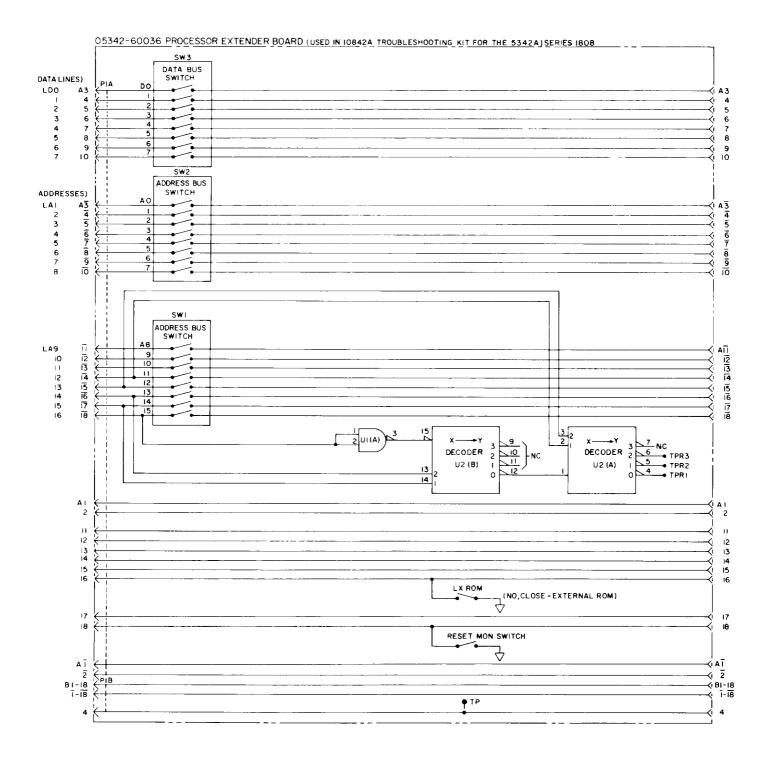

| 8-5.                 | Extender Board (05342-60036) Schematic Diagram           |          |

| 8-6.                 | Harmonic Heterodyne Technique                            |          |

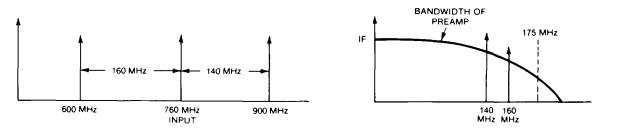

| 8-7.                 | Frequency Relationships                                  |          |

| 8-8.                 | HP 5342A Simplified Block Diagram                        |          |

| 8-9.                 | HP 5342A Block Diagram                                   |          |

| 8-10.                | Block Diagram of Synthesizer Section                     |          |

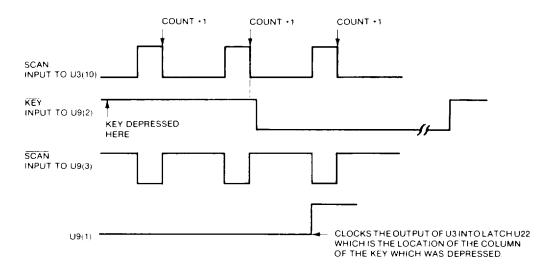

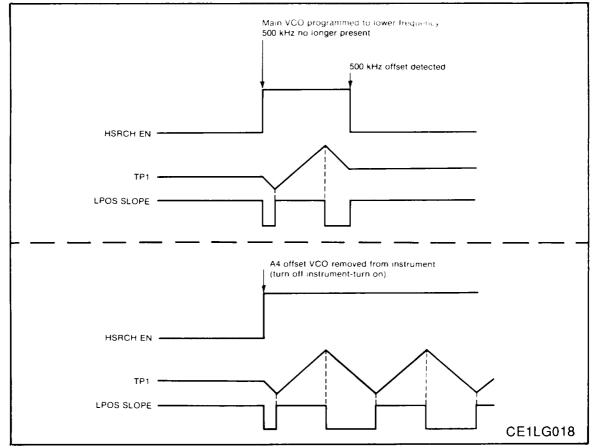

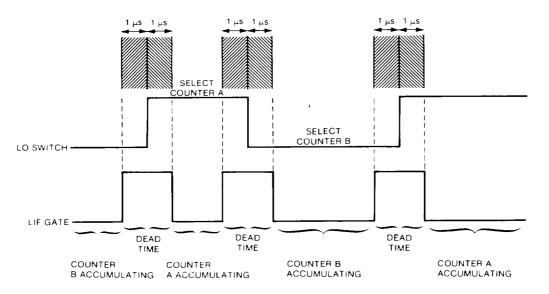

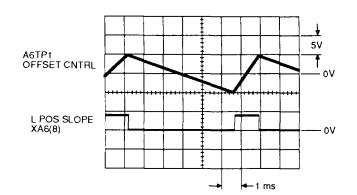

| 8-11.                | Timing Diagram of A6 Search Generator Operation          | 8-51     |

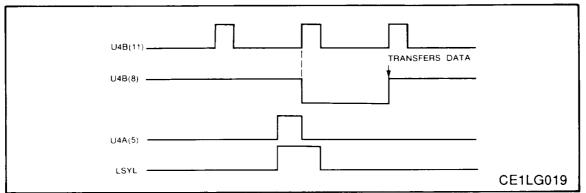

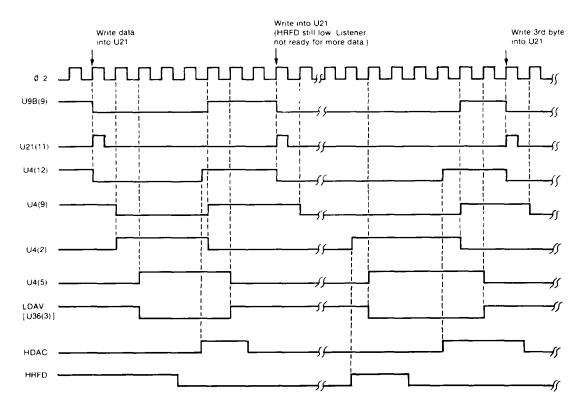

| 8-12.                | Data Transfer Timing in A10 Circuit                      |          |

| 8-13.                | Filter Timing on A12 IF Detector                         | 8-58     |

| 8-14.                | A14U21 Expanded Block Diagram                            | 8-61     |

| 8-15.                | Memory Arrangement                                       |          |

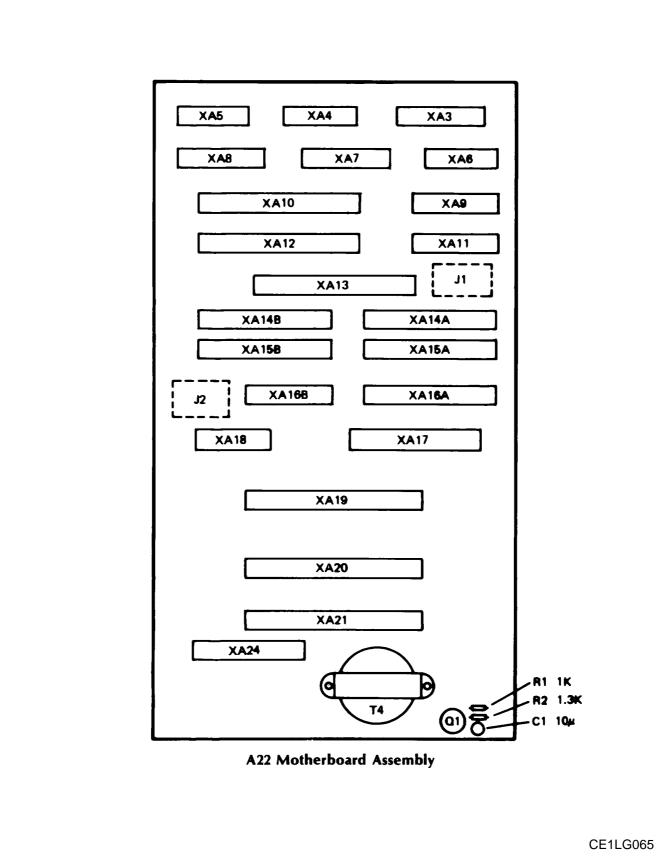

| 8-16.                | A19, A20, and A21 Power Supply Block Diagram             | 8-70     |

| 8-17.                | Deleted                                                  |          |

| 8-18.                | Deleted                                                  |          |

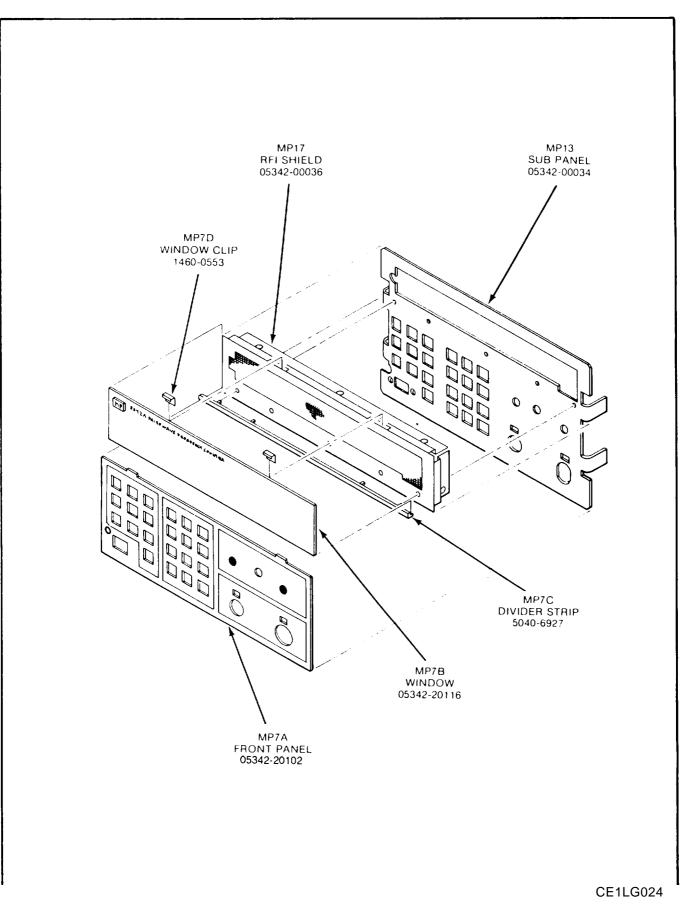

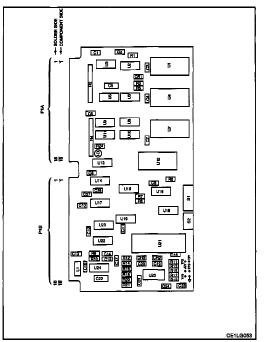

| 8-19.                | 5342A Front Panel Assembly                               |          |

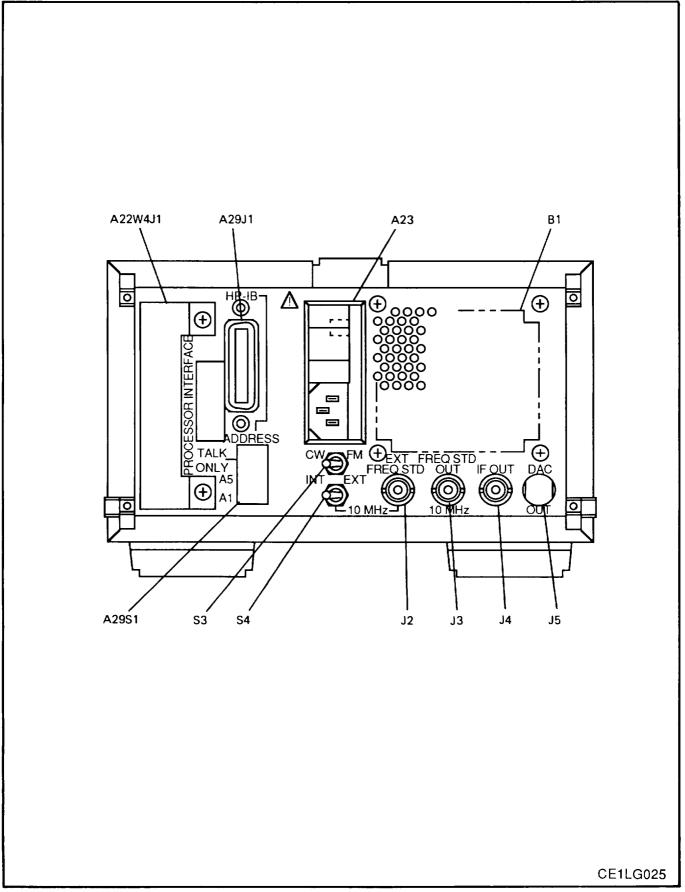

| 8-20.                | 5342A Rear View                                          |          |

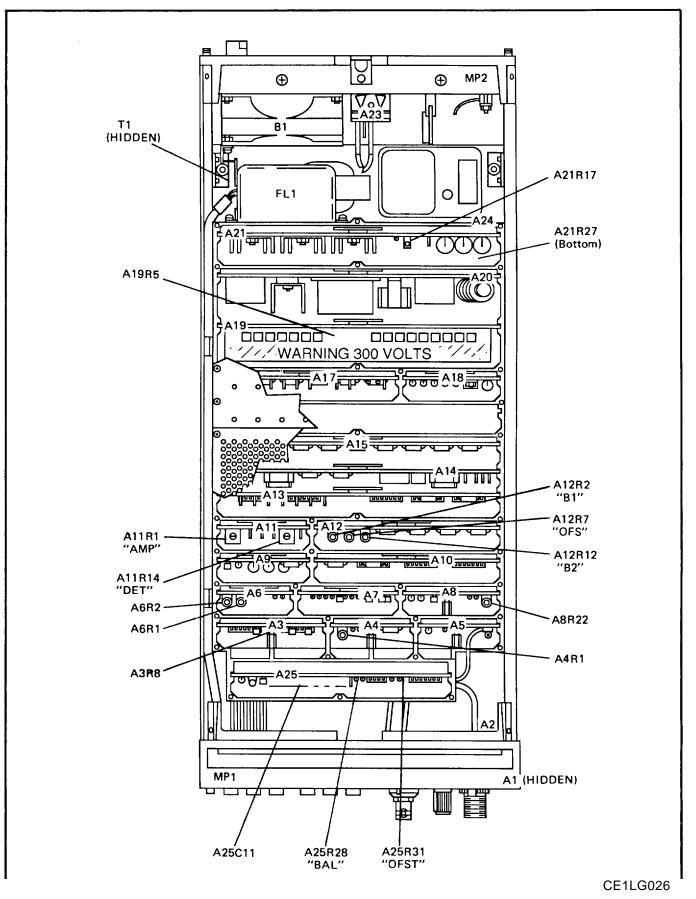

| 8-21.                | 5342A Top View (Assembly Locations and Adjustments)      |          |

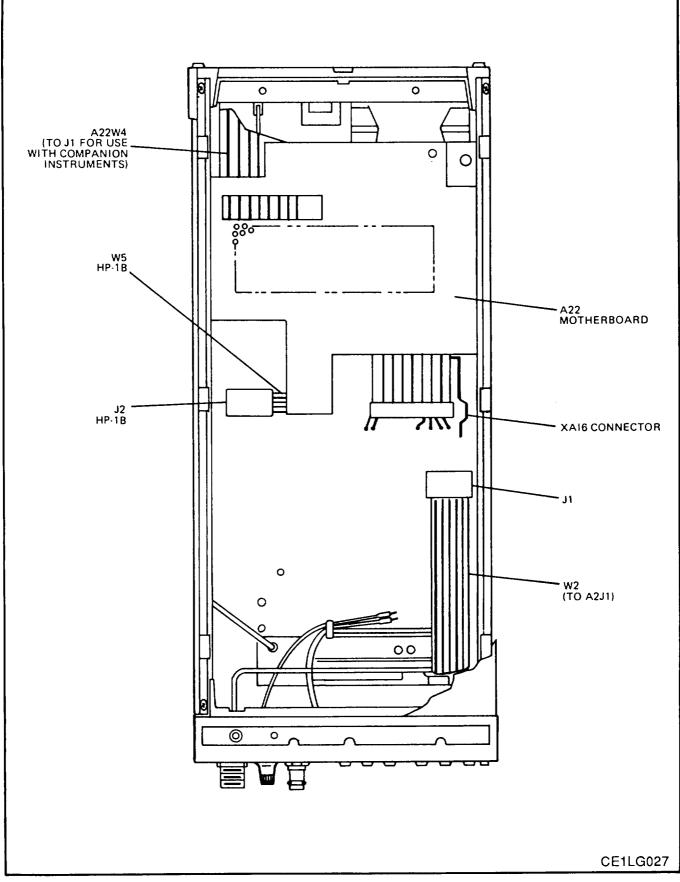

| 8-22.                | 5342A Bottom View, OptionsInstalled                      |          |

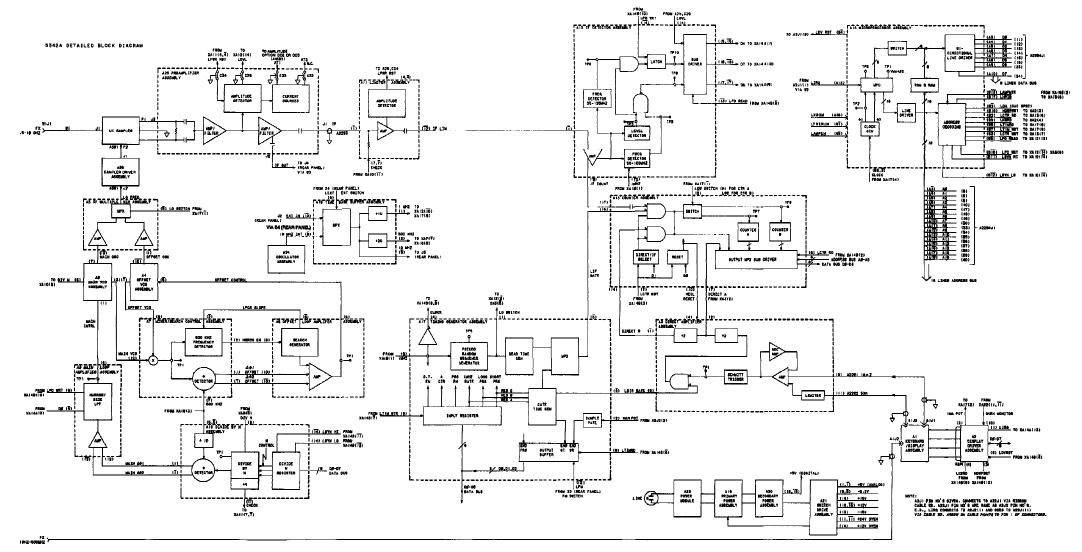

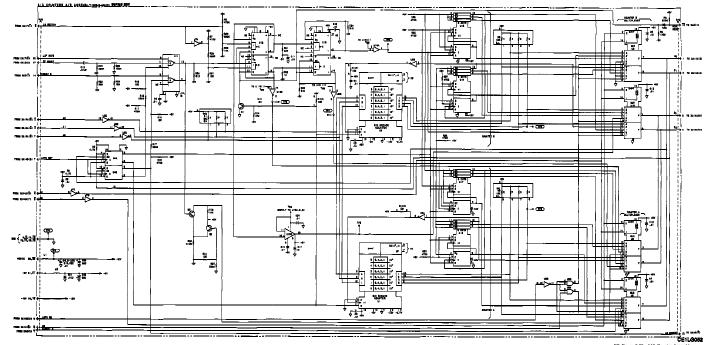

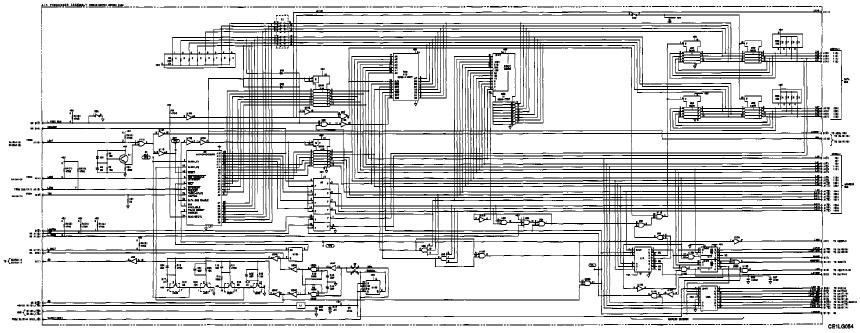

| FO 8-23.             | 5342A Detailed Block Diagram                             |          |

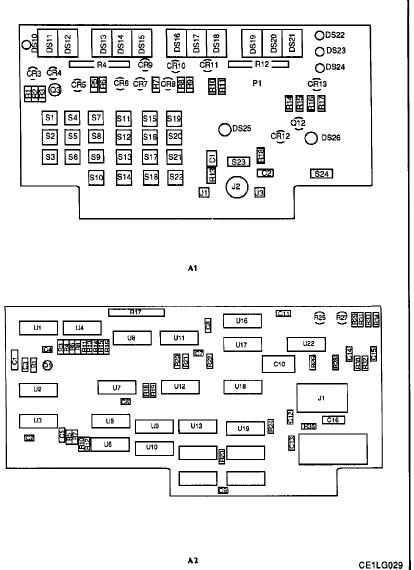

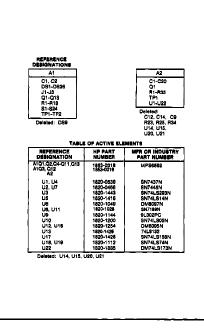

| FO 8-24.             | A1 Display Assembly and A2 Display Drive Assembly        | FP8-133  |

| 8-25.<br>FO 8-26.    | Deleted                                                  | ED 0 125 |

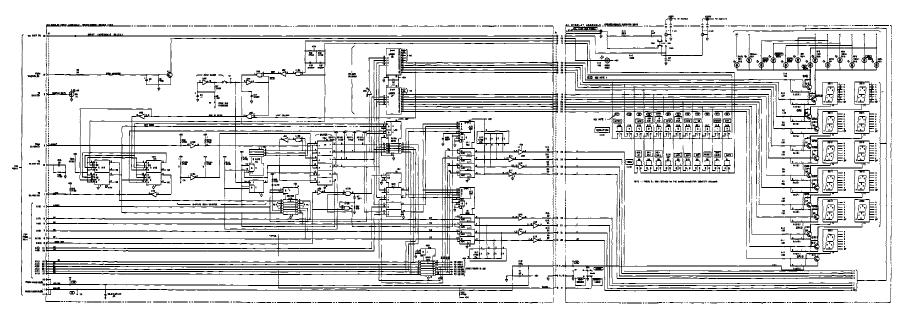

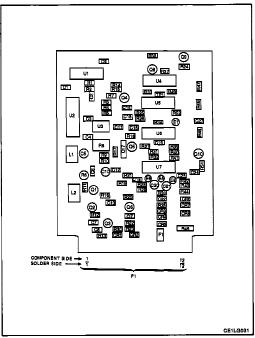

|                      | A3 Direct Count Amplifier Assembly                       |          |

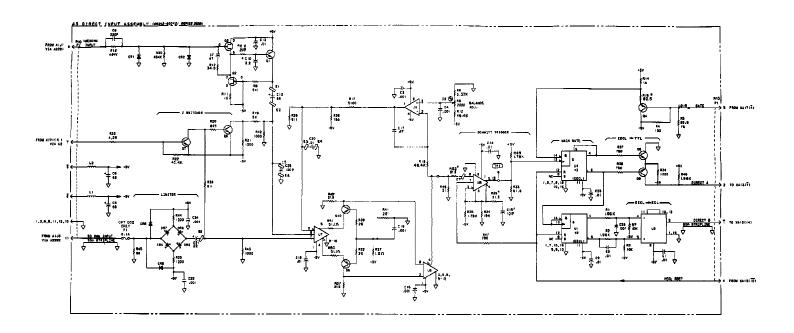

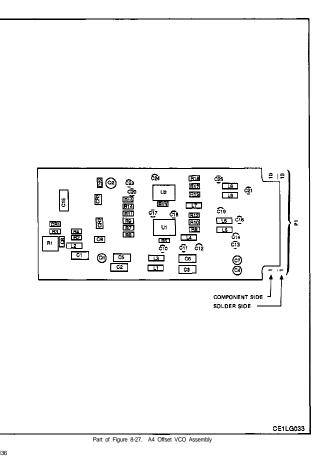

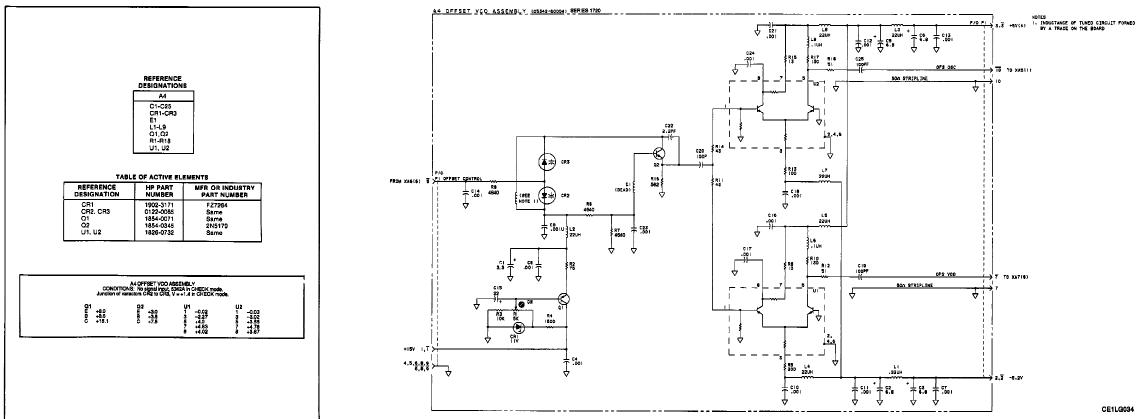

| FO 8-27.<br>FO 8-28. | A4 Offset VCO Assembly                                   |          |

| FO 8-28.<br>FO 8-29. | A6 OffsetLoopAmp/SearchGenerator Assembly                |          |

| FO 8-30.             | A7 Mixer/SearchControlAssembly                           |          |

| FO 8-31.             | A8 Main VCO Assembly                                     |          |

| FO 8-31.<br>FO 8-32. | A9 Main Loop Amplifier Assembly                          |          |

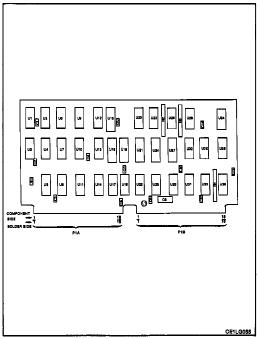

| FO 8-33.             | A10 Divide-by-N Assembly                                 |          |

| FO 8-34.             | A10 Divide by N Assembly                                 |          |

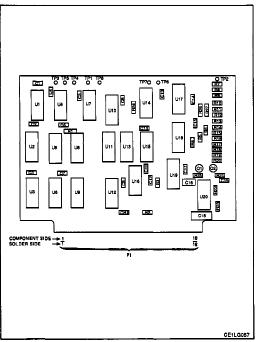

| FO 8-35.             | A12 IF Detector Assembly                                 |          |

| FO 8-36.             | A13 Counter Assembly.                                    |          |

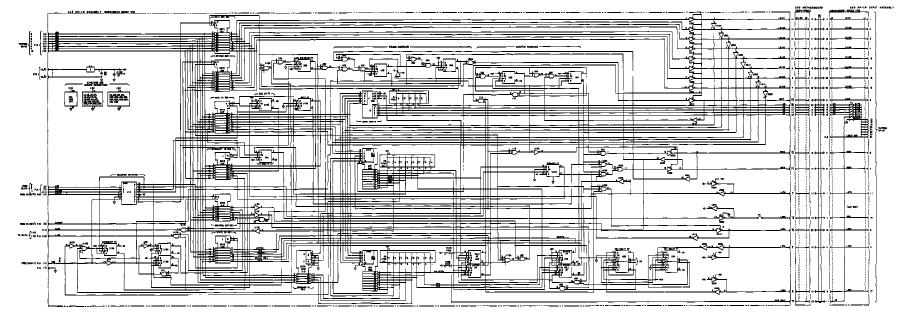

| FO 8-37.             | A14 Microprocessor Assembly                              |          |

| FO 8-38.             | A15 HP-IB Assembly                                       |          |

## LIST OF FIGURES (Continued)

| Figure | Title   | Page |

|--------|---------|------|

| 8-39.  | Deleted |      |

| 8-40.     | Deleted                                                                            |

|-----------|------------------------------------------------------------------------------------|

| FO 8-41.  | A17 Timing Generator Assembly FP 8-161                                             |

| FO 8-41A. | A17 Timing Generator Assembly (Series 2826 and higher) ., ,                        |

| FO 8-42.  | A18 Time Base Buffer Assembly FP 8-163                                             |

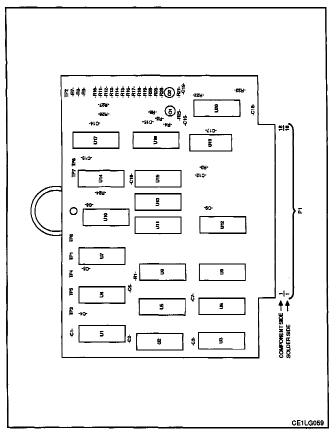

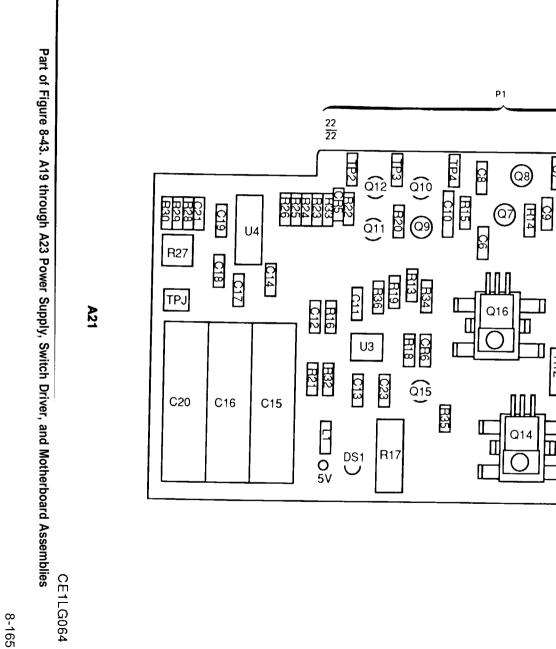

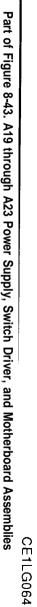

| FO 8-43.  | A19 through A23 Power Supply, Switch Driver, and Motherboard Assemblies . FP 8-165 |

| FO 8-44.  | A24 Oscillator Assemblies FP 8-169                                                 |

| FO 8-45.  | A25 Preamplifier Assembly FP 8-171                                                 |

| FO 8-46.  | A26 Sampler Driver Assembly FP 8-173                                               |

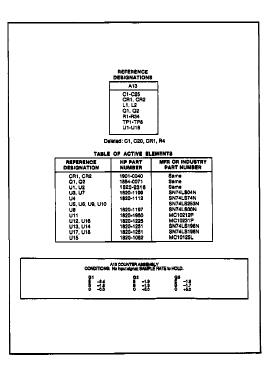

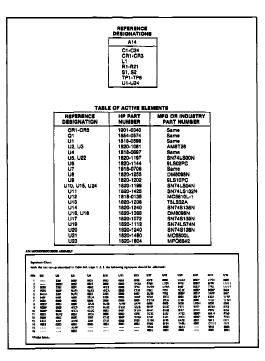

| C-1.     | Schematic Diagram Notes             | C-2    |

|----------|-------------------------------------|--------|

| FO C-2.  | 10811A Overall Block Diagram        | C -3   |

| C-3A.    | Basic Colpitts-Type Oscillator      | C-4    |

| C-3B.    | Main Oscillator Schematic Design    | C-5    |

| C-4.     | Mode Suppression                    | C-5    |

| C-5.     | Frequency Tuning Circuit            | C-6    |

| C-6.     | EFC                                 | C-7    |

| C-7.     | Automatic Gain Control (AGC)        | C-7    |

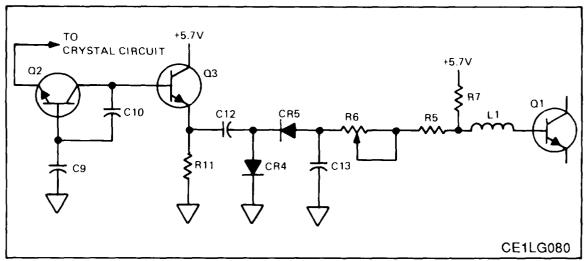

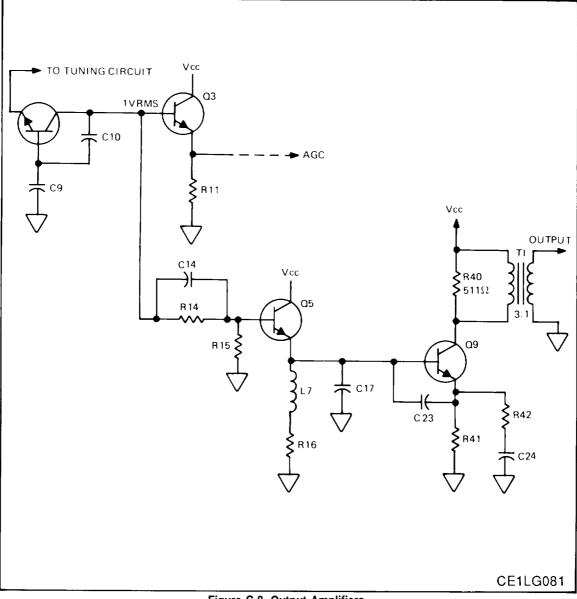

| C-8.     | Output Amplifiers                   | C-8    |

| C-9.     | Voltage References                  | C-9    |

| C-10.    | Oven Control Circuits               | C-10   |

| C-11.    | Turn-on Current Limit Circuit       | C-11   |

| C-12.    | Heater Transistor Balance Circuit   | C-11   |

| C-13.    | Oven Controller Block Diagram       | C-16   |

| FO C-14. | 10811A Oscillator Schematic Diagram | ' C-25 |

|          |                                     |        |

## LIST OF TABLES

| Table                                                                                                                                                                  | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 1-1.<br>1-2.<br>1-3.<br>1-4.                                                                                                                                           | Model 5342A/H16 Specifications<br>Equipment Supplied<br>Accessories Available<br>Recommended Test Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 1-3<br>. 1-4           |

| 3-1.<br>3-2.<br>3-3.<br>3-4.                                                                                                                                           | HP-IB Interface Capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-18<br>3-19             |

| 4-1.<br>4-2.<br>4-3.<br>4-4.<br>4-5.                                                                                                                                   | Operational Verification Record .<br>Model 5342A Program .<br>Model 9825A Program Description .<br>Sample Printout .<br>Performance Test Record                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | · ·4 - 7<br>4-10<br>4-12 |

| 5-1.                                                                                                                                                                   | Adjustments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-2                      |

| 6-1.<br>6-2.<br>6-3.<br>6-4.<br>6-5.<br>6-6.<br>6-7.<br>6-8.<br>6-9.                                                                                                   | Deleted<br>Deleted<br>Deleted<br>Deleted<br>Deleted<br>Deleted<br>Deleted<br>Deleted<br>Deleted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |

| 7-1.                                                                                                                                                                   | Deleted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |

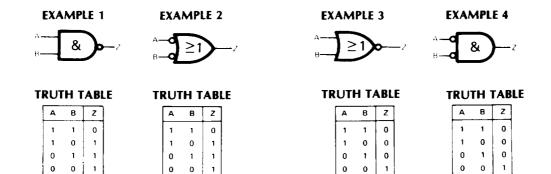

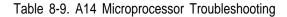

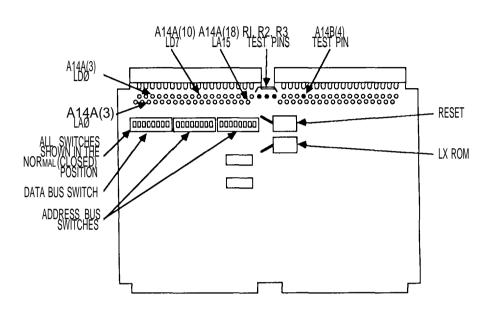

| 8-1.<br>8-2.<br>8-3.<br>8-4.<br>8-5.<br>8-6.<br>8-7.<br>8-8.<br>8-9.<br>8-10.<br>8-11.<br>8-12.<br>8-13.<br>8-14.<br>8-15.<br>8-16.<br>8-17.<br>8-18.<br>8-19.<br>8-20 | Assembly Identification .<br>Signal Names .<br>10842A Kit Contents .<br>Replaceable Parts for Extender Board 05342-60036 .<br>Overall Troubleshooting .<br>Assemblies Tested by Test Mode .<br>Probable Failed Assemblies by Test Mode .<br>Diagnostic Modes of the 5342A .<br>A14 Microprocessor Troubleshooting .<br>A19, A20,A21 Power Supply Troubleshooting .<br>A1,A2 Keyboard/DisplayTroubleshooting .<br>A3 Direct Count Amplifier Troubleshooting .<br>A13 Counter Troubleshooting .<br>A17 Timing Generator Troubleshooting .<br>A17, A12, A25, U1 IF Troubleshooting .<br>A1, A2, A7 Offset Loop Synthesizer Troubleshooting .<br>A4, A6, A7 Offset Loop Synthesizer Troubleshooting .<br>A5 RF Multiplexer Troubleshooting |                          |

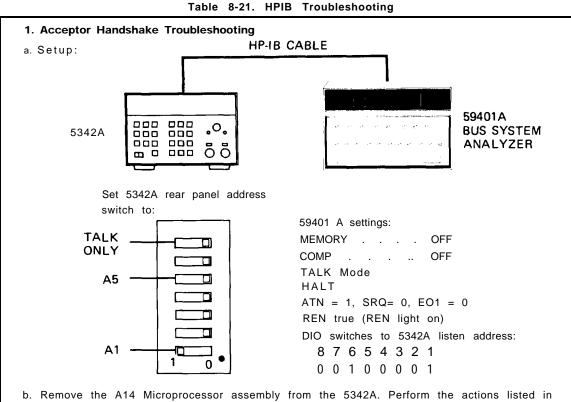

| 8-20.<br>8-21.<br>8-21A.<br>8-21B.<br>8-21C.                                                                                                                           | Deleted<br>HP-IB Troubleshooting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8-121<br>8-122           |

## LIST OF TABLES (Continued)

| Table   | Title                                  | Page   |

|---------|----------------------------------------|--------|

| C-1.    | Temperature Set Resistor List          | C-15   |

| FO C-2. | Oven Controller Troubleshooting Tree F | P C-19 |

| C-3.    | Oven Circuit Voltages                  | C-23   |

| C-4.    | Oscillator Section Normal Voltages     | C-23   |

#### Section 0 INTRODUCTION

## 0-1. SCOPE.

This manual contains instructions for the operation and maintenance of Microwave Frequency Counter TD-1225A(V)2/U. Throughout this manual, the Microwave Frequency Counter TD-1225A(V)2/U is referred to as either the Instrument, Frequency Counter, 5342A, or 5342A/H16.

## 0-2. CONSOLIDATED INDEX OF ARMY PUBLICATIONS AND BLANK FORMS.

Refer to the latest issue of DA Pam 25-30 to determine whether there are new editions, changes, or additional publications pertaining to the equipment.

## 0-3. MAINTENANCE FORMS, RECORDS, AND REPORTS.

a. Reports of Maintenance and Unsatisfactory Equipment. Department of the Army forms and procedures used for equipment maintenance will be those prescribed by DA Pam 738-750 as contained in Maintenance Management Update.

*b.* Reporting of Item and Packaging Deficiencies. Fill out and forward SF 364 Report of Discrepancy (ROD) as prescribed in AR 735-11-2/DLAR 4140.55 /SECNAVINST 4355.18/AFR 400-54/MCO 4430.3J.

*c.* Transportation Discrepancy Report (TDR) (SF 36D) Fill out and forward Transportation Discrepancy in Report (TDR) (SF 361) as prescribed in AR 55-38/NAVSUPINST 4610.33C/AFR 75-18/MCO P4610.19D/DLAR 4500.15.

## 0-4. REPORTING EQUIPMENT IMPROVEMENT RECOMMENDATIONS (EIR'S).

If your TD-1225A(V)2/U needs improvement, let us know. Send us an EIR. You, the user, are the only one who can tell us what you don't like about your equipment. Let us know why you don't like the design or performance. Put it on an SF 368 (Product Quality Deficiency Report). Mail it to: Commander, US Army Communications-Electronics Command and Fort Monmouth, ATTN: AMSEL-PA-MA-D, Fort Monmouth, New Jersey 07703-5000. We'll send you a reply.

#### 0-5. ADMINISTRATIVE STORAGE,

Administrative storage of equipment issued to and used by Army activities will have preventive maintenance performed in accordance with the PMCS charts before storing. When removing the equipment from administrative storage the PMCS should be performed to assure operational readiness.

#### 0-6. DESTRUCTION OF ARMY ELECTRONICS MATERIEL.

Destruction of Army electronics materiel to prevent enemy use shall be in accordance with TM 750-244-2.

### 0-7. WARRANTY INFORMATION.

The TD-1225A(V)2/U is warranted by Hewlett-Packard Company for one year. Warranty starts on the date of shipment to the original buyer. Report all defects in material or workmanship to your supervisor who will take appropriate action.

#### 0-8. SAFETY CONSIDERATIONS.

This product is a Safety Class I instrument; that is, one provided with a protective earth terminal. Before operating or servicing the TD-1225A(V)2/U, personnel should familiarize themselves with both the safety markings on the equipment and the safety information presented at the beginning of this manual.

## 0-9. TOOLS AND TEST EQUIPMENT CROSS REFERENCE.

The following is a cross-reference of test equipment from table 1-4 to Appendix B MAC test equipment.

| Table 1-4 Model Number/Name           | Appendix B MAC Tool Number/Name             |

|---------------------------------------|---------------------------------------------|

| AE 705-0048 Isolation Transformer     | GIS-1000 Isolation Transformer              |

| HP 10842A Extender Kit                | HP 10842A Service Accessory Kit             |

| HP 11667A Power Splitter              |                                             |

| HP 11048B 50 $\Omega$ Termination     |                                             |

| HP 1400-0734 AP Clips, 4 each         |                                             |

| HP 141T/8552A/8554B Spectrum Analyzer |                                             |

| HP 1607A Logic State Analyzer         |                                             |

| HP 1740A Oscilloscope                 | AN/USM-281C Oscilloscope System             |

| HP 3406A AC Voltmeter                 | ME-416/U Voltmeter, Sampling                |

| HP 3465A DC Voltmeter                 | HP 3490A and AN-PSM-45 Multimeter           |

| HP 436A Power Meter                   |                                             |

| HP 5004A Signature Analyzer           |                                             |

| HP 5345A Frequency Counter            |                                             |

| HP 545A Logic Probe                   |                                             |

| HP 546A Logic Pulser                  |                                             |

| HP 547A Current Tracer                |                                             |

| HP 59401A Bus System Analyzer         |                                             |

| HP 651 B Signal Generator             | SG-763/U or SG-1121 (A)1/U Signal Generator |

| HP 8481A Power Sensor                 |                                             |

| HP 8495B Step Attenuator              |                                             |

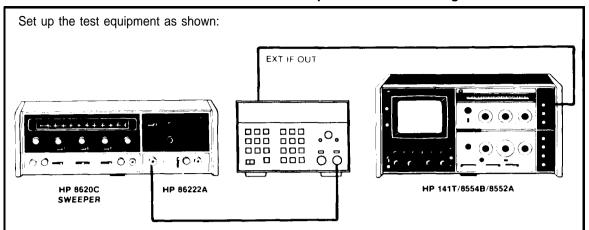

| HP 8620C/86222A Signal Generator      | HP 8620C/86222A Mainframe with Plug-in      |

| HP 8620C/86290A Signal Generator      | HP 8620C/86290A Mainframe with Plug-in      |

| HP 909A/012 50 $\Omega$ Termination   |                                             |

|                                       |                                             |

## SECTION I GENERAL INFORMATION

## **1-1. INTRODUCTION**

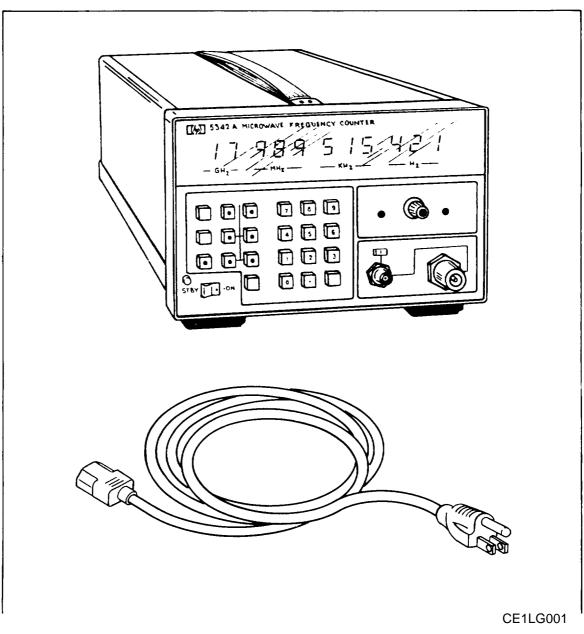

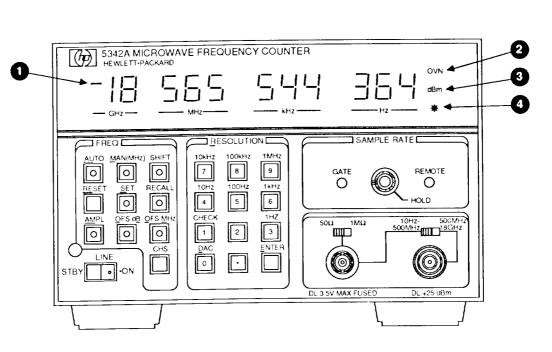

1-2. This manual provides operating and service information for the Hewlett-Packard Model 5342A Microwave Frequency Counter, shown in Figure 1-1.

## **1-3. SPECIFICATIONS**

1-4. Specifications of the 5342A are listed in Table 1-1.

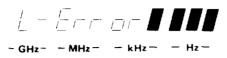

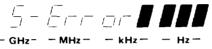

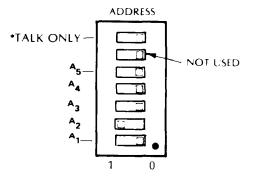

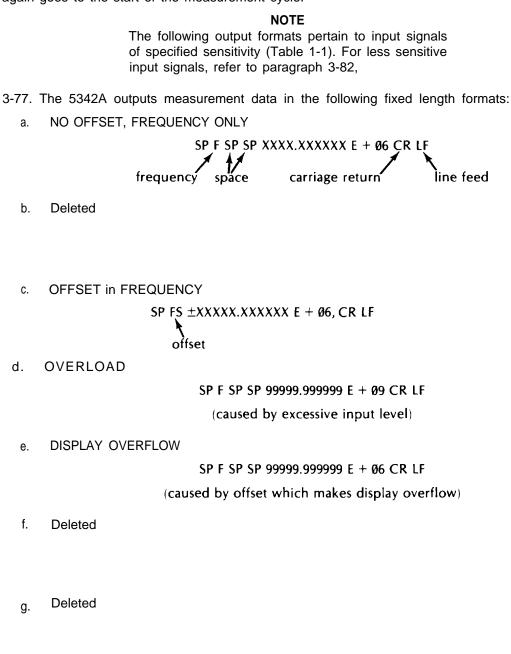

Figure 1-1. Model 5342A Microwave Frequency Counter