# TM 11-5805-367-35/3 DEPARTMENT OF THE ARMY TECHNICAL MANUAL

DS, GS, AND DEPOT MAINTENANCE MANUAL

# **MULTIPLEXERS**

# TD-352/U

# AND TD-353/U

This copy is a reprint which includes current pages from Changes 1 through 5.

HEADQUARTERS, DEPARTMENT OF THE ARMY 14 FEBRUARY 1967

# WARNING

Be careful when working on the 115-volt ac line connections. Serious injury or death may result from contact with these points.

### DON'T TAKE CHANCES!

TM 11-5805-367-35/3 C 5

HEADQUARTERS DEPARTMENT OF THE ARMY Washington, DC, 1 April 1987

# DS,GS, AND DEPOT MAINTENANCE MANUAL MULTIPLEXERS TD-352/U (NSN 5805-00-900-8199) AND TD-353/U (NSN 5805-00-900-9153)

TM 11-5805-367-35/3, 14 February 1967, is changed as follows:

1. Remove old pages and insert new pages as indicated below. New or changed material is indicated by a vertical bar in the margin of the page. Added or revised illustrations are indicated by a vertical bar adjacent to the identification number.

| Remove pages                                                                                                                                               | Insert pages                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Remove pages         i and i         iii through vi         1-1/(1-2 blank)         3-13/(3-14 blank)         6-1 and 6-2         A-1 and A-2         None | iii through vi<br>1-1/(1-2 blank)<br>3-13/(3-14 blank)<br>6-1 and 6-2<br>A-1 and A-2 |

| None                                                                                                                                                       | Figure FO 6-53.1                                                                     |

|                                                                                                                                                            |                                                                                      |

| Figure FO 6-59                                                                                                                                             |                                                                                      |

|                                                                                                                                                            |                                                                                      |

2. File this change sheet in the front of the publication for reference purposes.

This publication is required for official use or for administrative or for operational purposes only. Distribution is limited to US Government Agencies. Other requests for this document must be referred to Commander, US Army Communications-Electronics Command and Fort Monmouth,ATTN: AMSEL-ME-P, Fort Monmouth, NJ 07703-5000.

CHANGE

No.5

### By Order of the Secretary of the Army:

Official:

JOHN A. WICKHAM, JR. General, United States Army Chief of Staff

**R.L. DILWORTH** Brigadier General, United States Army The Adjutant General

**DISTRIBUTION:**

To be distributed in accordance with DA Form 12-51 literature requirements for TD-202/U, TD-203/U, TD-206/U, TD-352/U, and TD-353.

HEADQUARTERS DEPARTMENT OF THE ARMY Washington, DC, 3 February 1984

No.4

# DS, GS, AND DEPOT MAINTENANCE MANUAL MULTIPLEXERS TD-352/U (NSN 5805-00-900-8199) AND TD-353/U (5805-00-985-9153)

TM 11-5805-367-35/3, 14 February 1967, is changed as follows:

- 1. New or changed material is indicated by a vertical bar in the margin.

- 2. A new or changed illustration is indicated by a vertical bar next to the figure number.

- 3. Remove old pages and insert new pages as indicated below.

Remove pages

Insert pages

| i and ii          | i, ii and ii.1/(ii.2 blank)       |

|-------------------|-----------------------------------|

| 1-1               | 1-1/(1-2 blank)                   |

| 2-29 and 2-30     | 2-29 and 2-30                     |

| 2-33 and 2-34     | 2-33 and 2-34                     |

| 3-11 and 3-12     | 3-11 and 3-12                     |

| 4-3 and 4-4       | 4-3 and 4-4                       |

| 4-91 through 4-94 | 4-91 through 4-94                 |

| 5-1 and 5-2       | 5-1 and 5-2                       |

| 5-5 through 5-12  | 5-5 through 5-12.3/(5-12.4 blank) |

| 5-23 and 5-24     | 5-23 and 5-24                     |

| A-1               | A-1/(A-2 blank)                   |

|                   |                                   |

4. File this change in front of the publication for reference purposes.

CHANGE

By Order of the Secretary of the Army:

Official:

# **ROBERT M. JOYCE**

Major General, United States Army The Adjutant General

DISTRIBUTION:

To be distributed in accordance with DA Form 12-51C requirements for TD-352/U and TD-353/U.

JOHN A. WICKHAM JR. General, United States Army Chief of Staff

TM 11-5805-367-35/3

TECHNICAL MANUAL NO.11-5805-367-35/3

٢

#### HEADQUARTERS DEPARTMENT OF THE ARMY WASHINGTON, DC, 14 February 1967

# DS, GS, AND DEPOT MAINTENANCE MANUAL MULTIPLEXERS TD-352/U (NSN 5805-00-900-8199) AND TD-353/U (5805-00-985-9153)

|         |      | REPORTING ERRORS AND RECOMMENDING IMPROVEMENT                                                                                                                                                                                                                                                                                                                                                                                                                           | rs                          |      |      |

|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------|------|

|         |      | You can help improve this manual. If you find any mistakes or if you<br>know of a way to improve the procedures, please let us know. Ma<br>your letter, DA Form 2028 (Recommended Changes to Publication<br>and Blank Forms), or DA Form 2028-2 located in the back of thi<br>manual direct to: Commander, US Army Communications-Electronic<br>Command and Fort Monmouth, ATTN: AMSEL-ME-MP, Fo<br>Monmouth, New Jersey 07703-5000. A reply will be sent direct to you | ail<br>ns<br>is<br>is<br>rt |      |      |

| Chapter | 1.   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | aragraph                    | Page |      |

|         |      | Scope                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                             |      | 1-1  |

|         |      | Consolidated index of Army publications and blank forms                                                                                                                                                                                                                                                                                                                                                                                                                 |                             |      | 1-1  |

|         |      | Maintenance forms, records and reports                                                                                                                                                                                                                                                                                                                                                                                                                                  |                             |      | 1-1  |

|         |      | Deleted                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                             |      | 1-1  |

|         |      | Reporting equipment improvement recommendations (EIR)                                                                                                                                                                                                                                                                                                                                                                                                                   |                             |      | 1-1  |

|         |      | Differences between semiconductor subassemblies                                                                                                                                                                                                                                                                                                                                                                                                                         |                             | 6    | 1-1  |

| Chapter | 2.   | FUNCTIONING                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                             |      |      |

| Section | I.   | Block Diagram Analysis, Multiplexer TD-352/U                                                                                                                                                                                                                                                                                                                                                                                                                            |                             |      |      |

|         |      | General                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                             |      | 2-1  |

|         |      | Transmit circuits for TD-352/U                                                                                                                                                                                                                                                                                                                                                                                                                                          |                             |      | 2-1  |

|         |      | Receive circuits for TD-352/U                                                                                                                                                                                                                                                                                                                                                                                                                                           |                             |      | 2-2  |

|         |      | Monitoring and alarm circuits for TD-352/U                                                                                                                                                                                                                                                                                                                                                                                                                              |                             | 4    | 2-3  |

|         |      | Fault locator circuits for TD-352/U                                                                                                                                                                                                                                                                                                                                                                                                                                     |                             |      | 2-4  |

|         |      | Power supply circuits for TD-352/U                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-                          | 6    | 2-4  |

|         | II.  | Block Diagram Analysis, Multiplexer TD-353/U                                                                                                                                                                                                                                                                                                                                                                                                                            |                             |      |      |

|         |      | General                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                             |      | 2-4  |

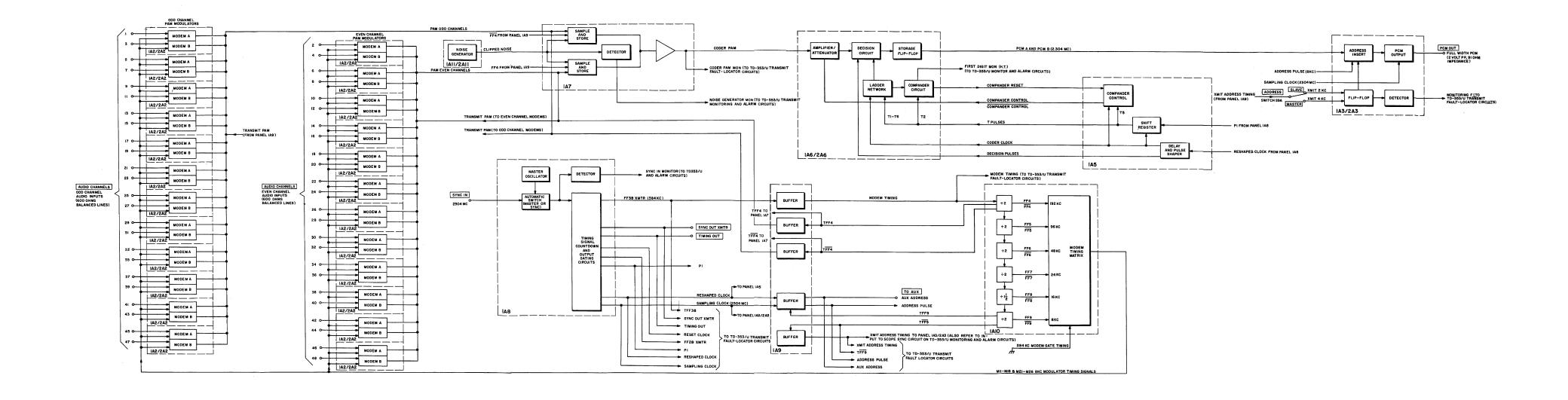

|         |      | Transmit circuits for TD 353/U                                                                                                                                                                                                                                                                                                                                                                                                                                          |                             |      | 2-4  |

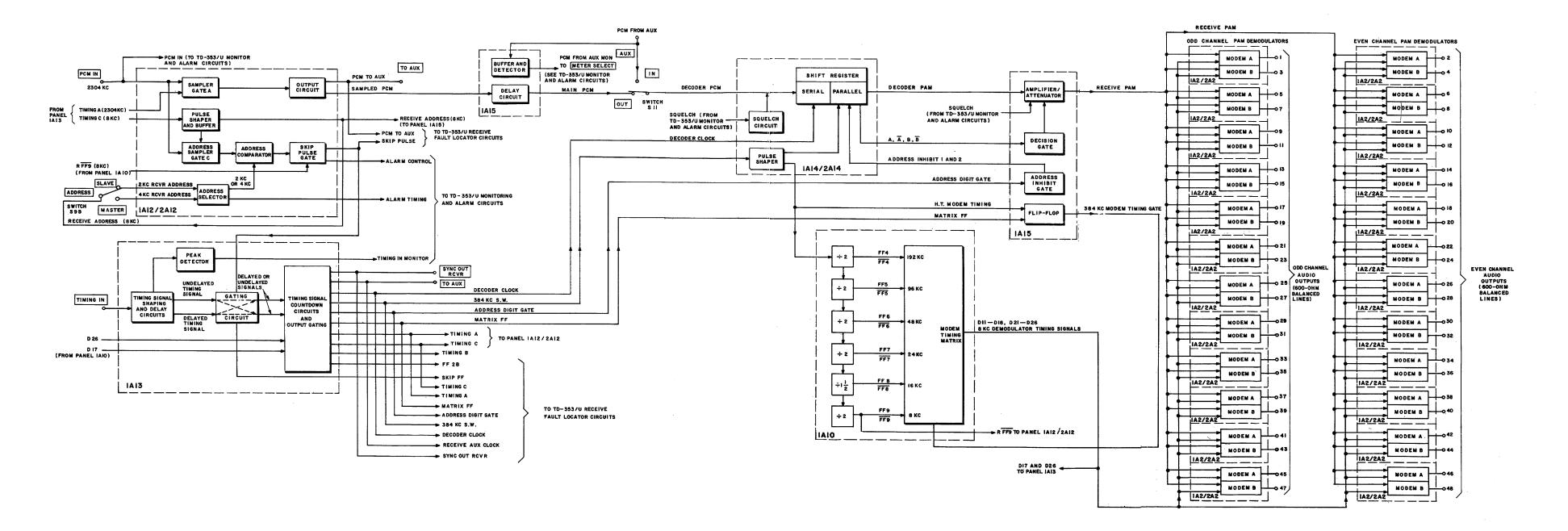

|         |      | Receive circuits for TD-353/U                                                                                                                                                                                                                                                                                                                                                                                                                                           |                             |      | 2-8  |

|         |      | Monitoring and alarm circuits for TD-353/U                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-                          | 10   | 2-10 |

|         |      | Fault locator circuits for TD 353/U                                                                                                                                                                                                                                                                                                                                                                                                                                     |                             |      | 2-10 |

|         |      | Power supply circuits for TD-3532U                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-                          | 12   | 2-10 |

|         | III. | Module Schematic Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                               |                             |      |      |

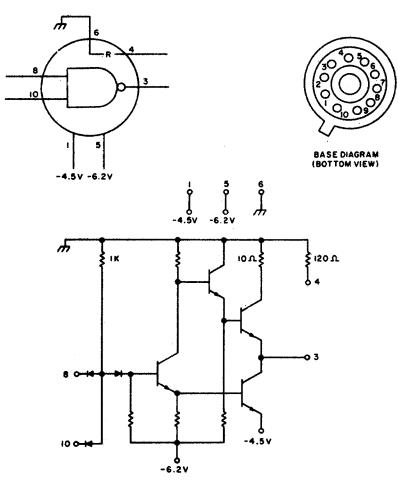

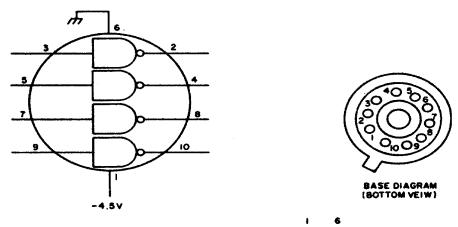

|         |      | Gate module 01                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-                          | 13   | 2-10 |

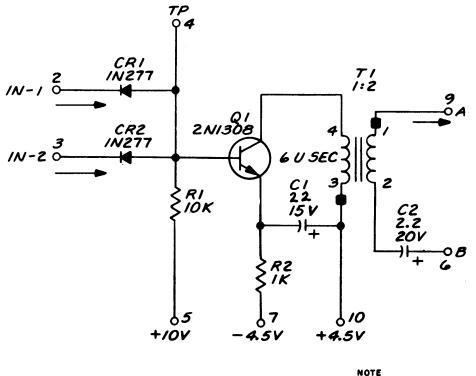

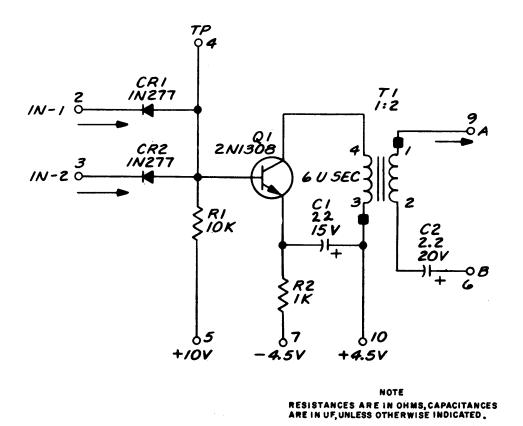

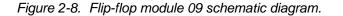

|         |      | Sampler module 08                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-                          | 14   | 2-13 |

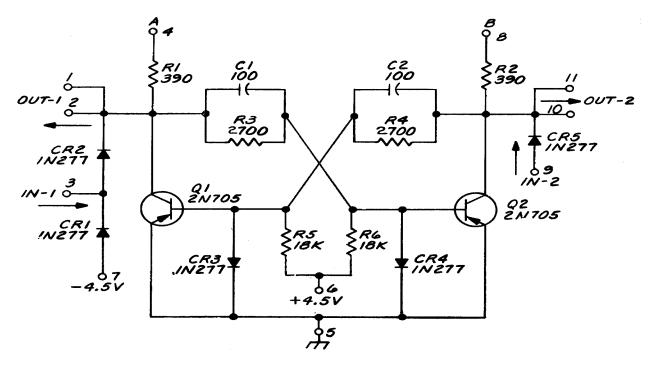

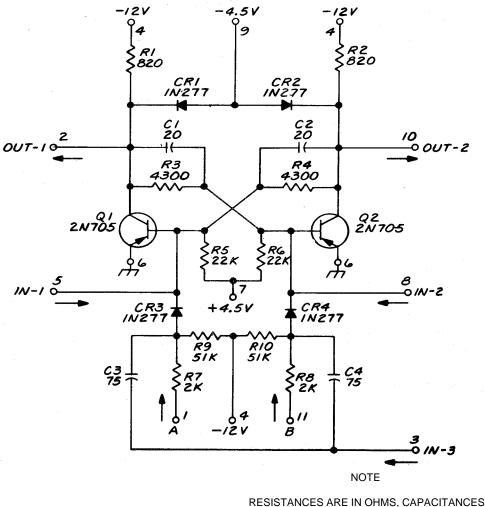

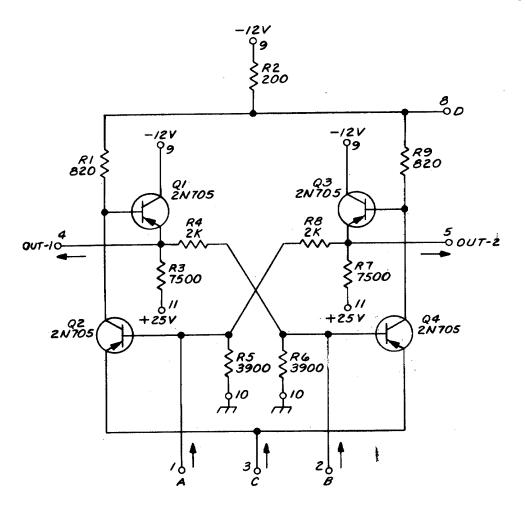

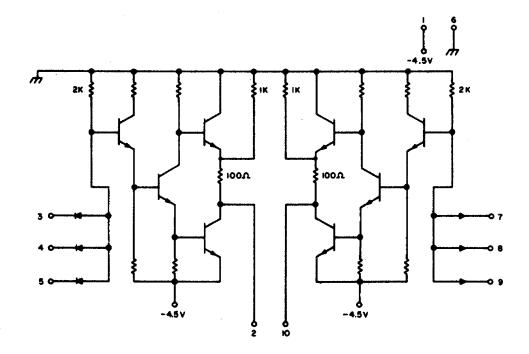

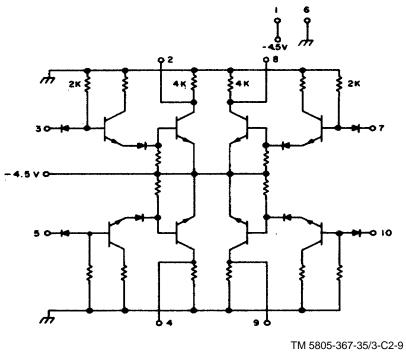

|         |      | Flip flop module 09                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-                          | 15   | 2-14 |

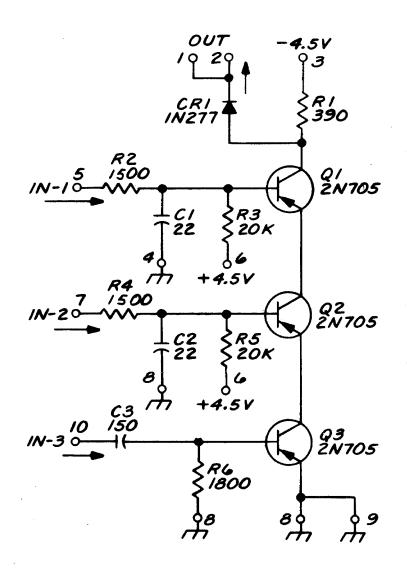

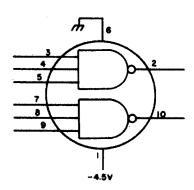

|         |      | NAND gate module 11                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-                          | 16   | 2-14 |

|         |      | Emitter follower module 15                                                                                                                                                                                                                                                                                                                                                                                                                                              |                             |      | 2-15 |

|         |      | Matrix module 16                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                             |      | 2-15 |

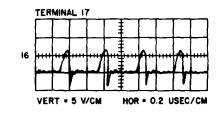

|         |      | Matrix module 17                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                             |      | 2-19 |

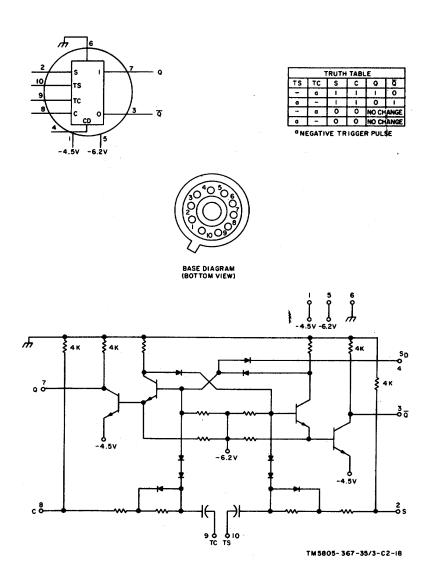

|         |      | Flip flop module 18                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                             |      | 2-19 |

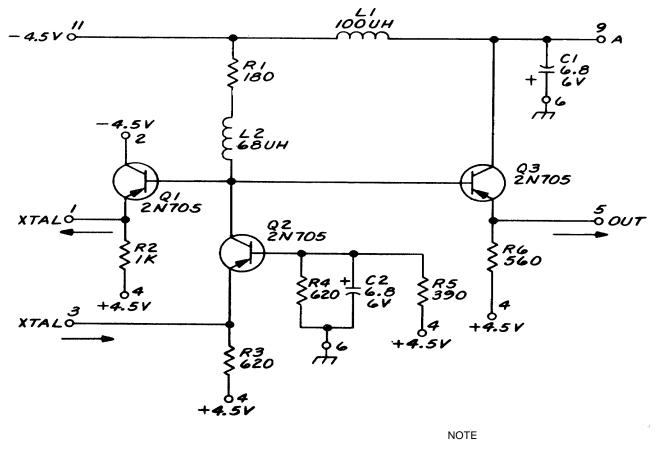

|         |      | Oscillator module 22                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                             |      | 2-19 |

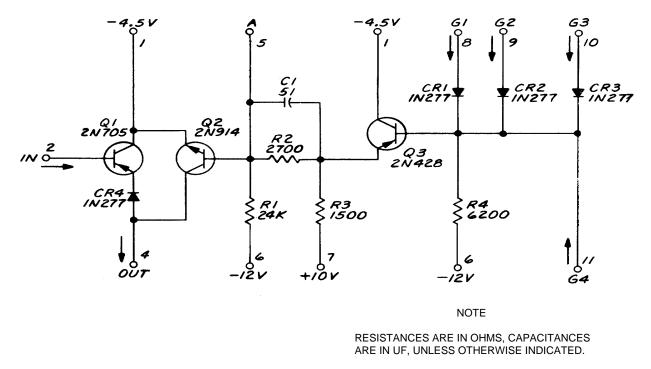

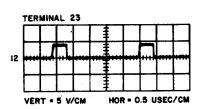

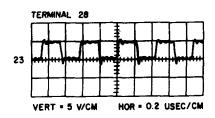

|         |      | Gate module 23                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                             | 22   | 2-21 |

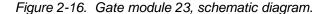

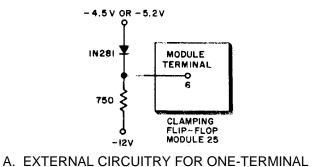

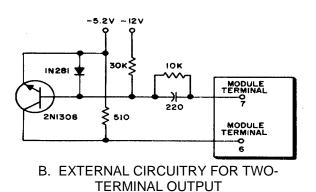

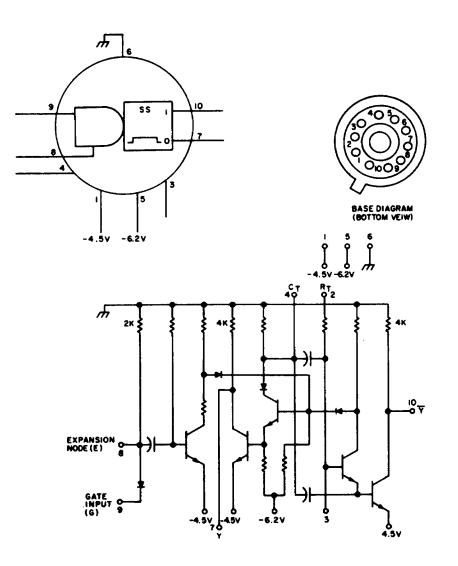

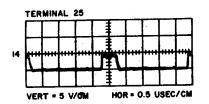

|         |      | Clamping flip flop module 25                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-2                         | 23   | 2-21 |

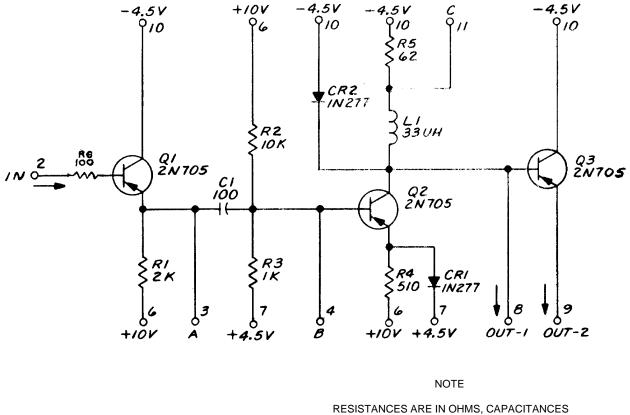

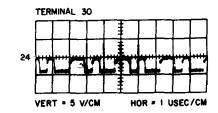

|         |      | Pulse shaper module 30                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                             |      | 2-22 |

|         |      | Amplifier module 31                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                             | 25   | 2-23 |

Change 5 i

|                    |          |                                                                         | Paragraph | Page |

|--------------------|----------|-------------------------------------------------------------------------|-----------|------|

|                    |          | Amplifier module 32                                                     |           | 2-24 |

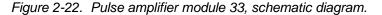

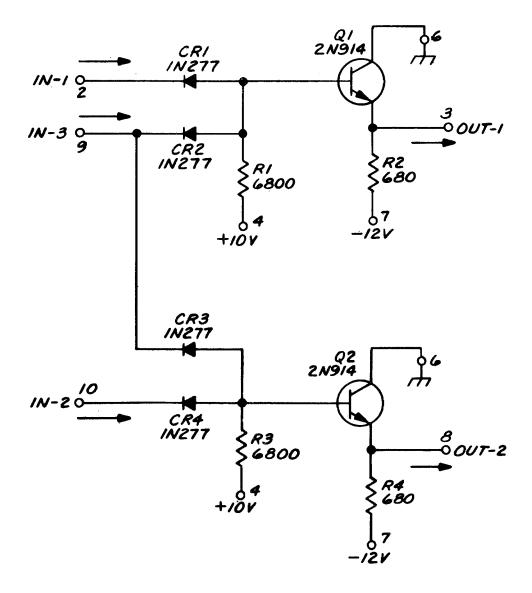

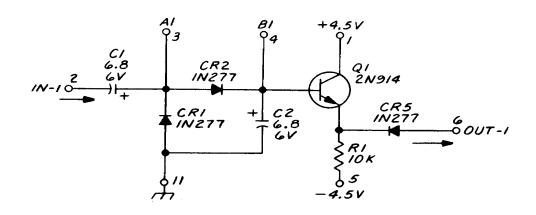

|                    |          | Pulse amplifier module 33                                               |           | 2-24 |

|                    |          | Gate module 35                                                          |           | 2-25 |

|                    |          | Detector module 36                                                      |           | 2-26 |

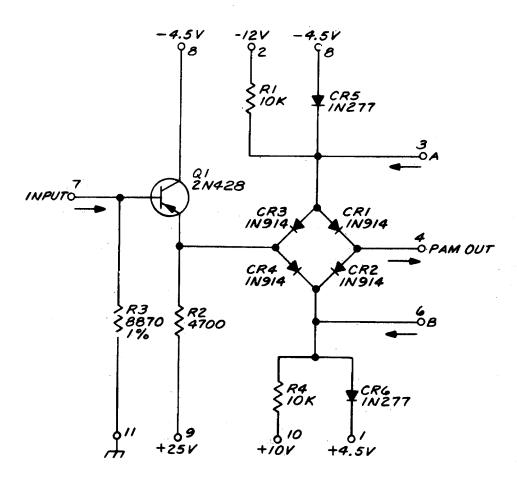

|                    |          | Sampler module 37                                                       |           | 2-26 |

|                    |          | Sampler module 38                                                       |           | 2-26 |

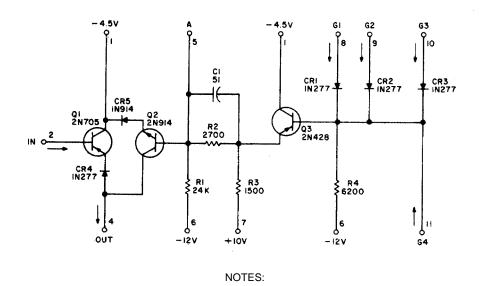

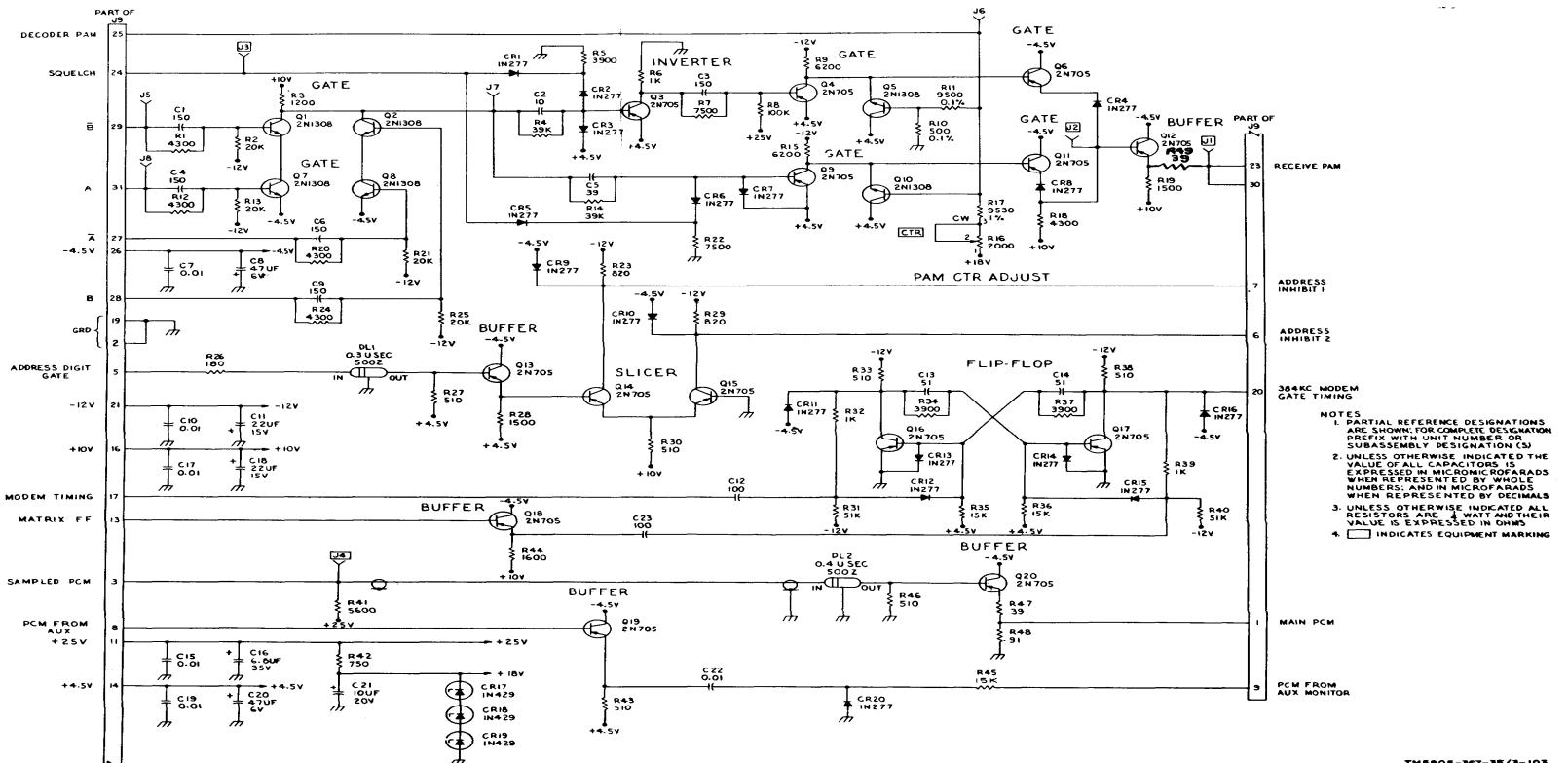

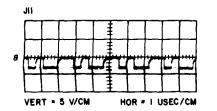

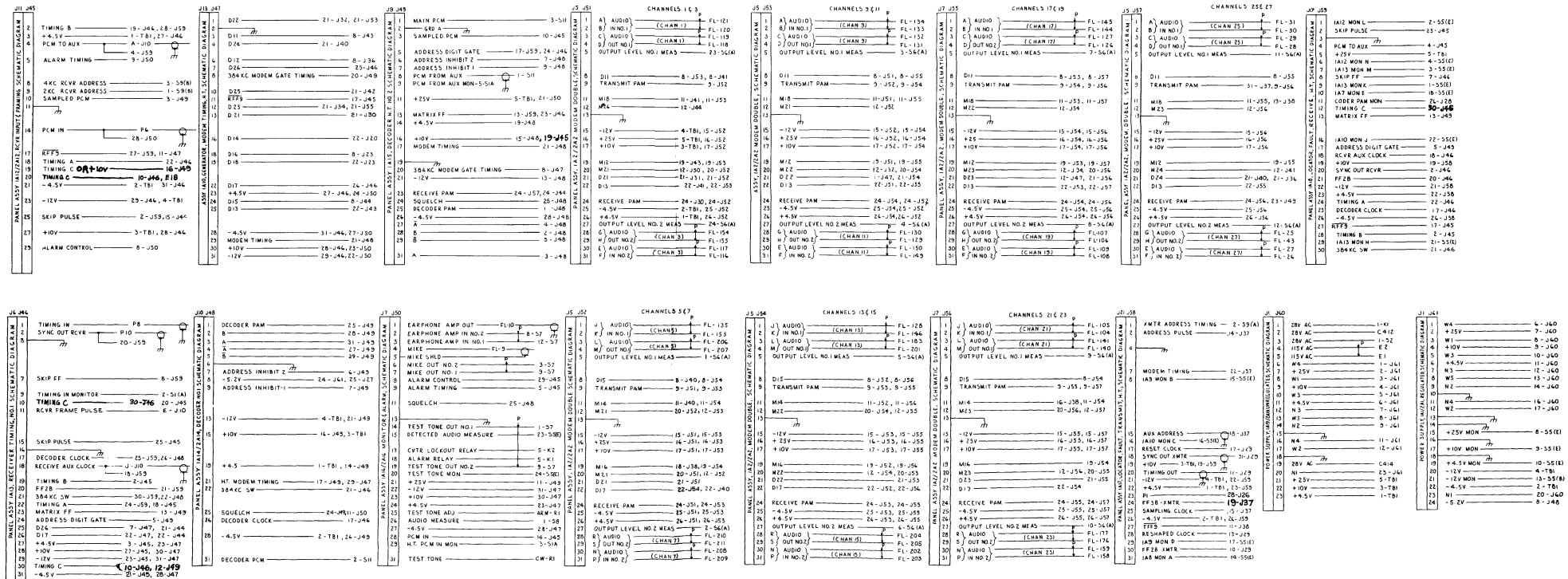

|                    | IV.      | Decision circuit module 42<br>Panel Schematic Analysis                  | 2-32      | 2-37 |

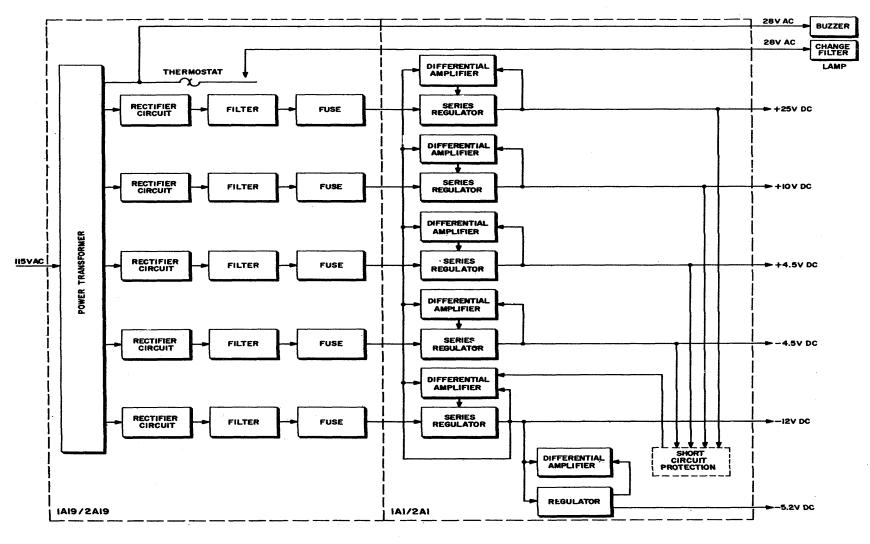

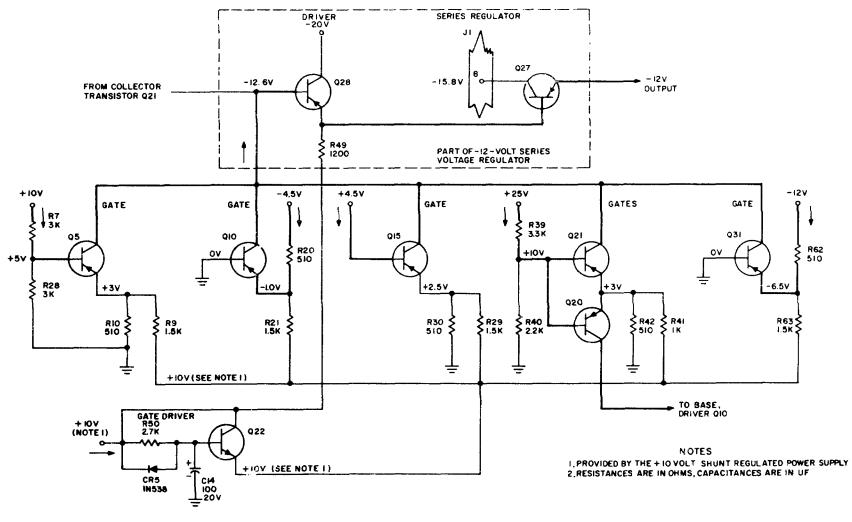

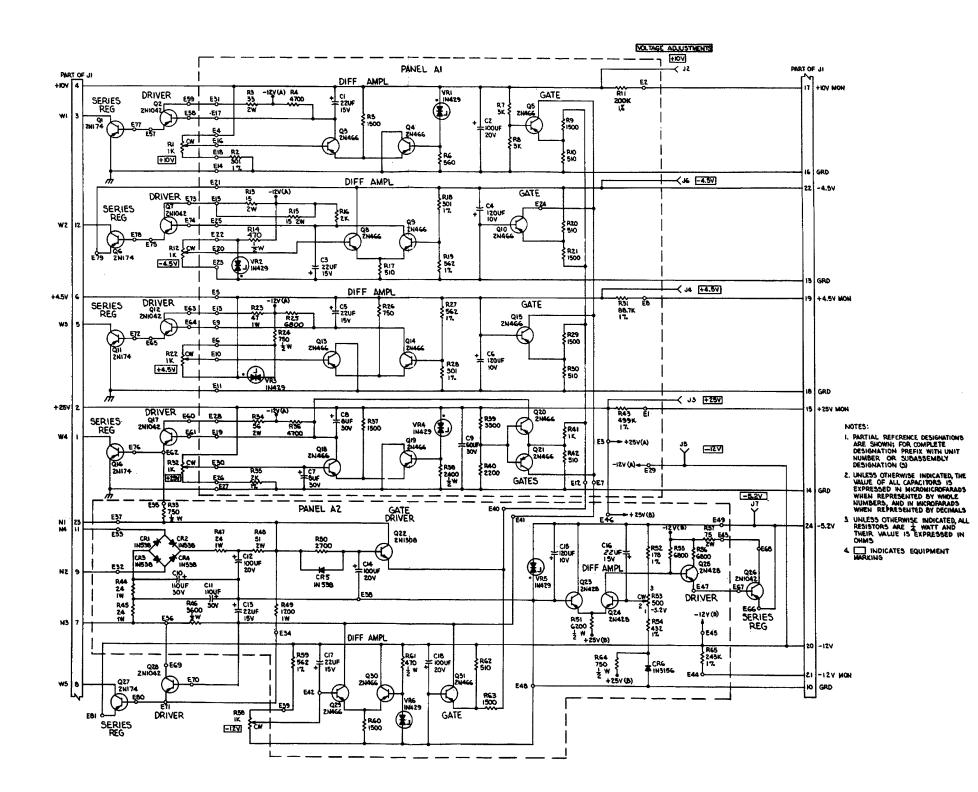

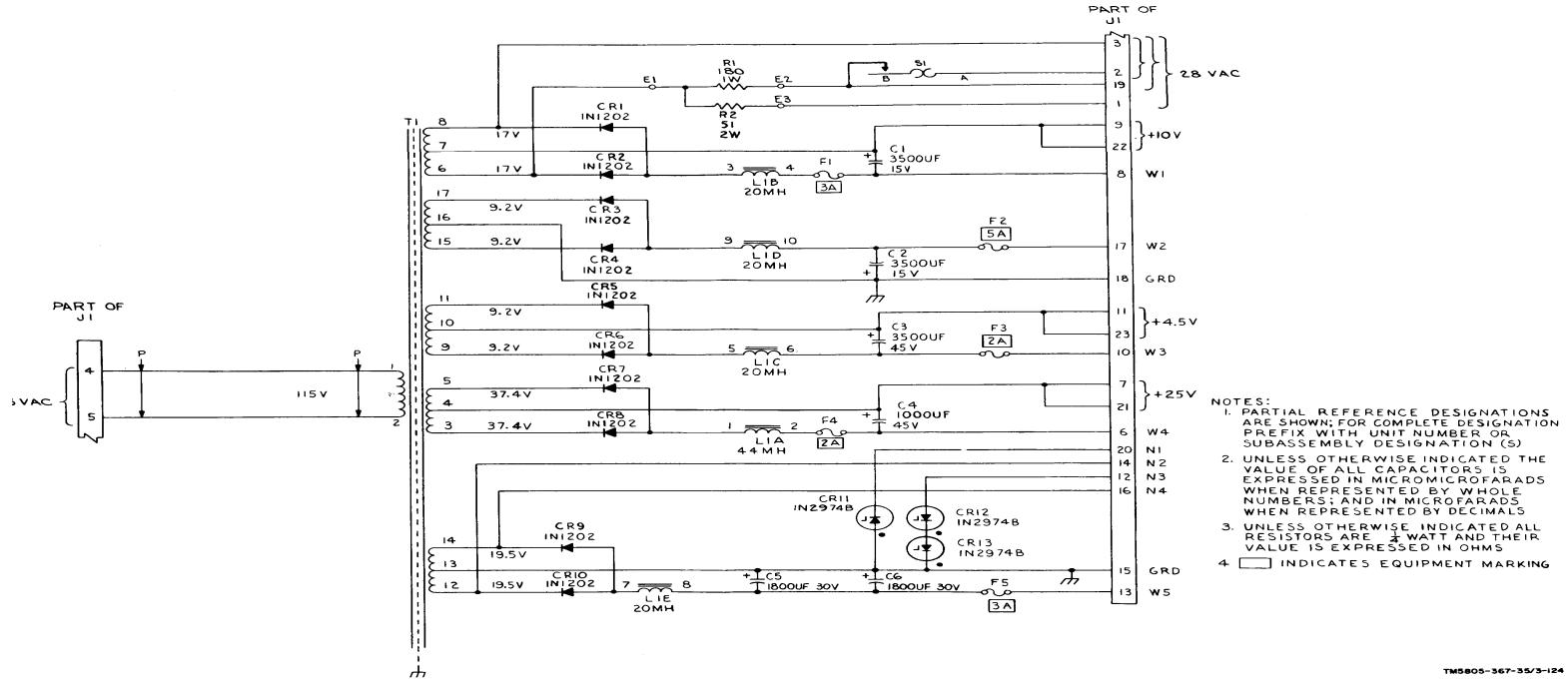

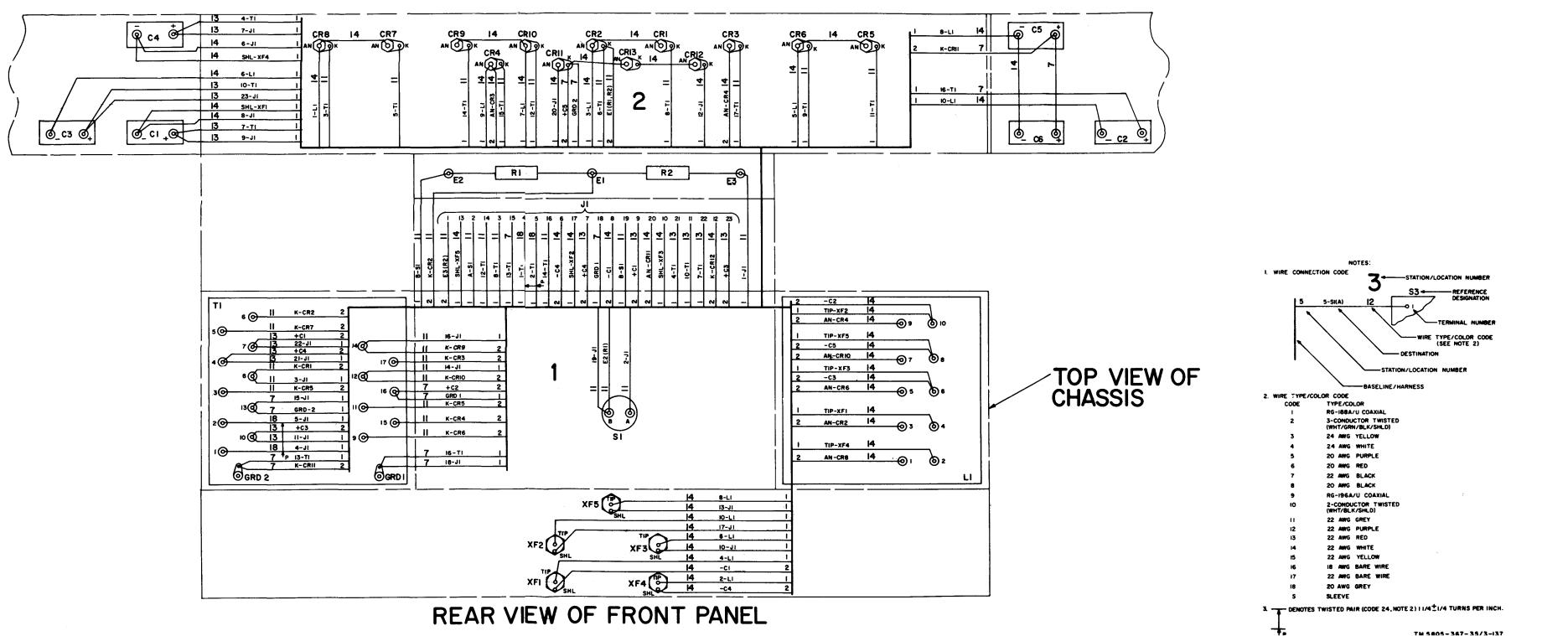

|                    |          | Regulated power supply panel 1A1/2A1                                    | 2-33      | 2-29 |

|                    |          | Double modem panel.1A2/2A2                                              | 2-34      | 2-38 |

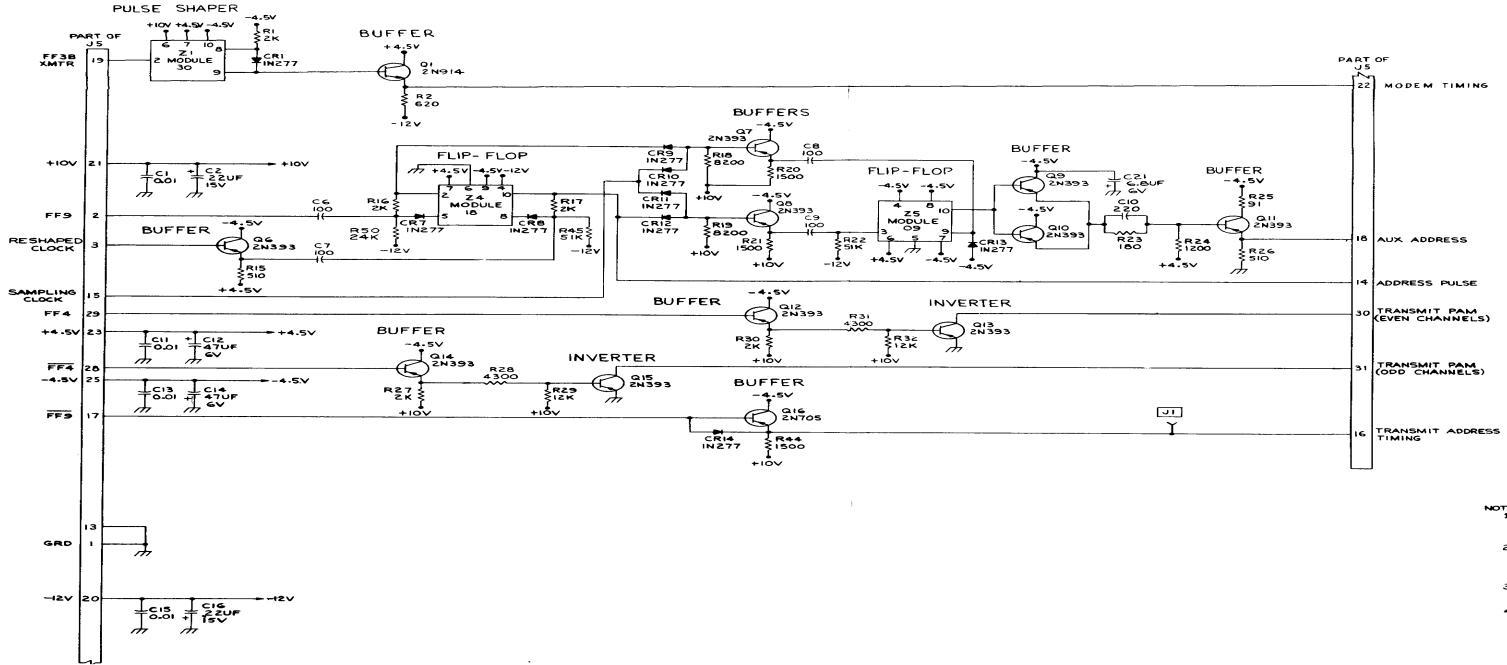

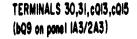

|                    |          | Pen output circuits, panel 1A3/2A3                                      | 2-35      | 2-40 |

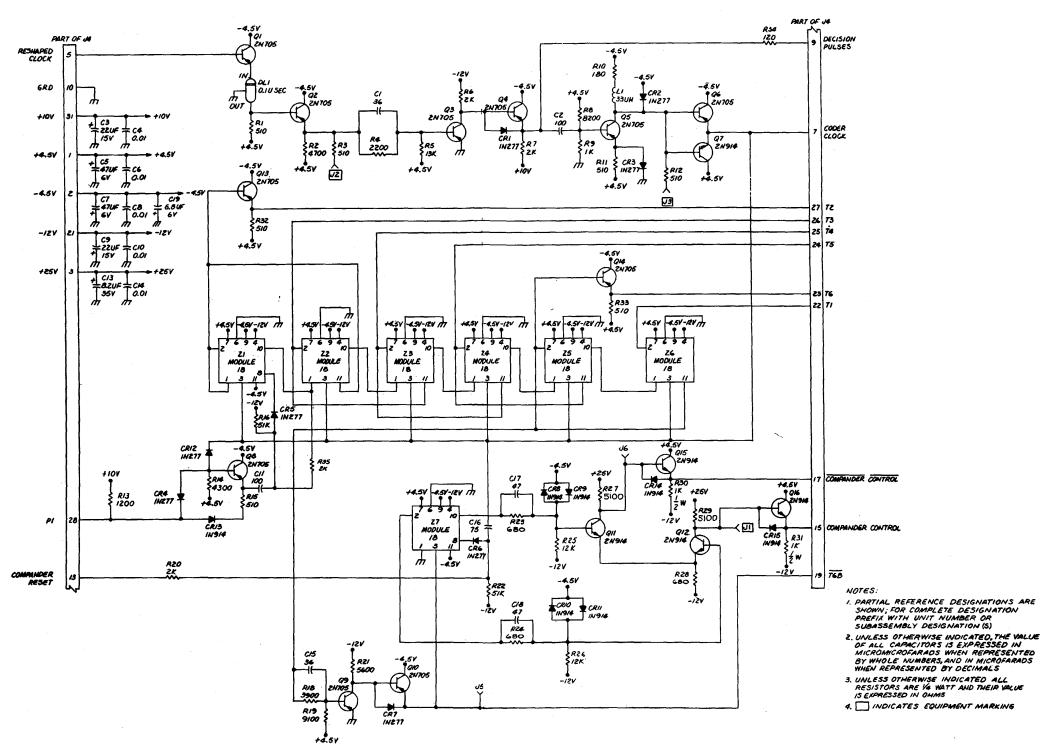

|                    |          | Coder timing (h.t.), panel 1A5                                          | 2-36      | 2-41 |

|                    |          | Coder timing (m.t.), panel 2A5                                          | 2-37      | 2-42 |

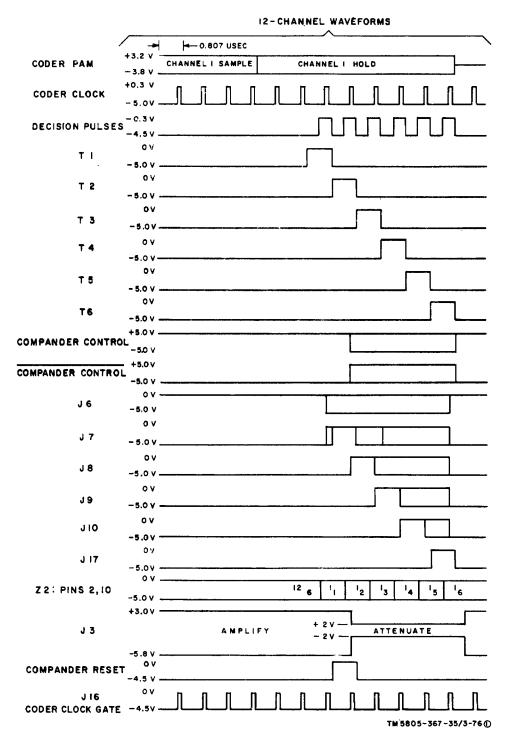

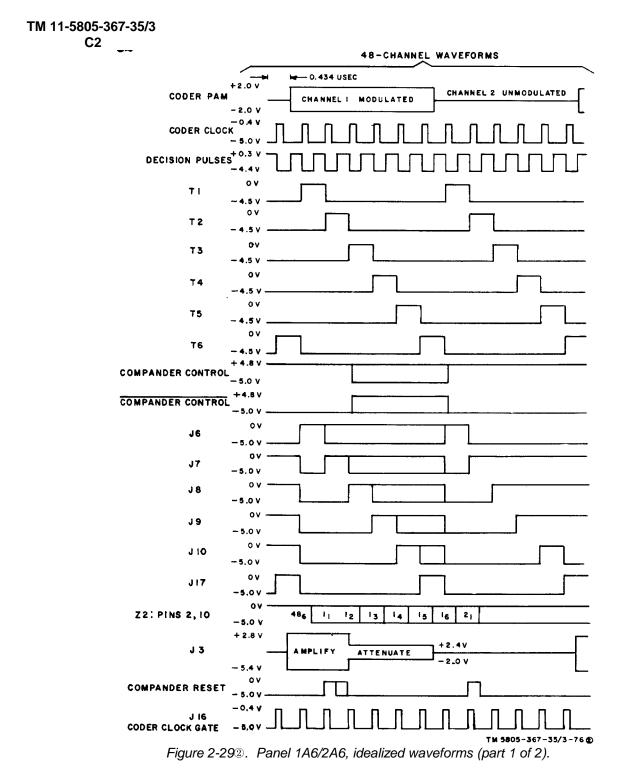

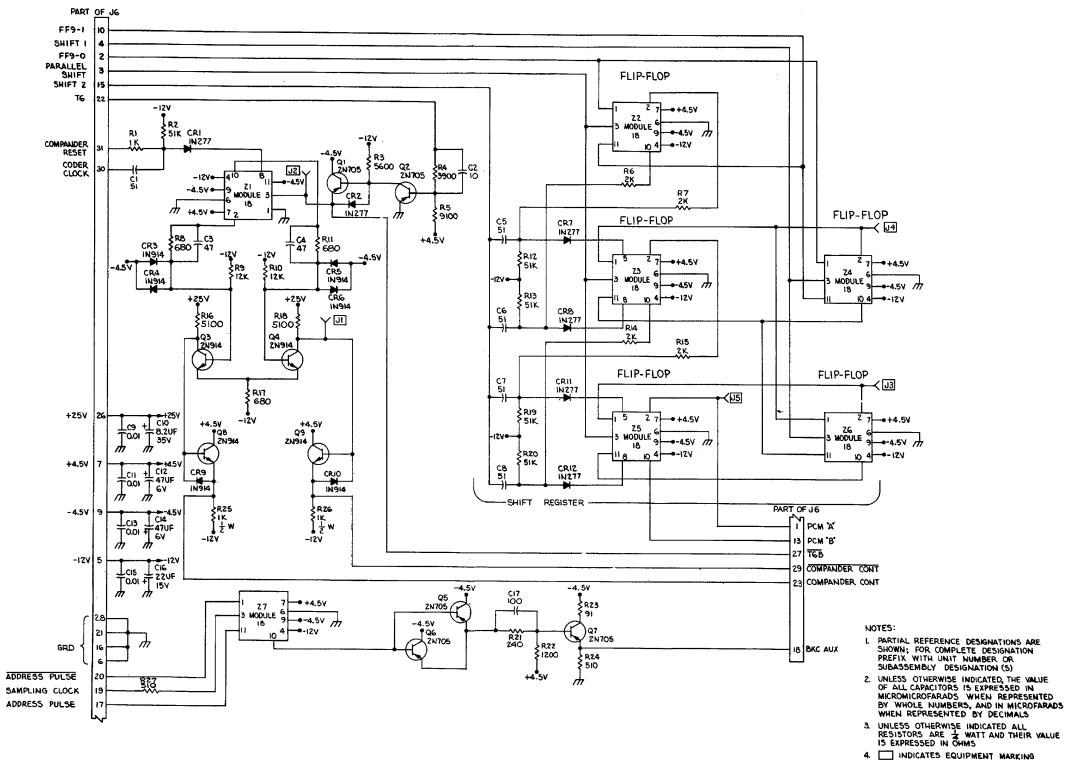

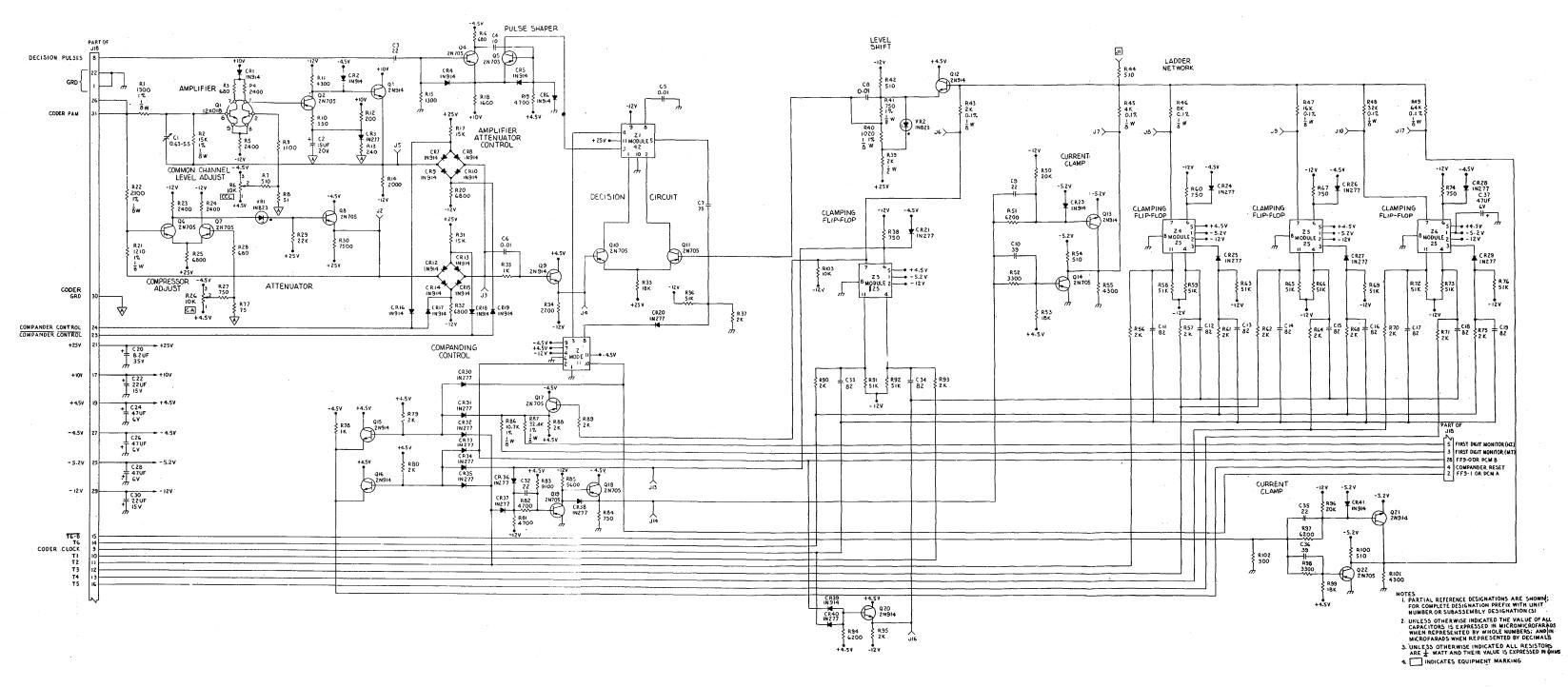

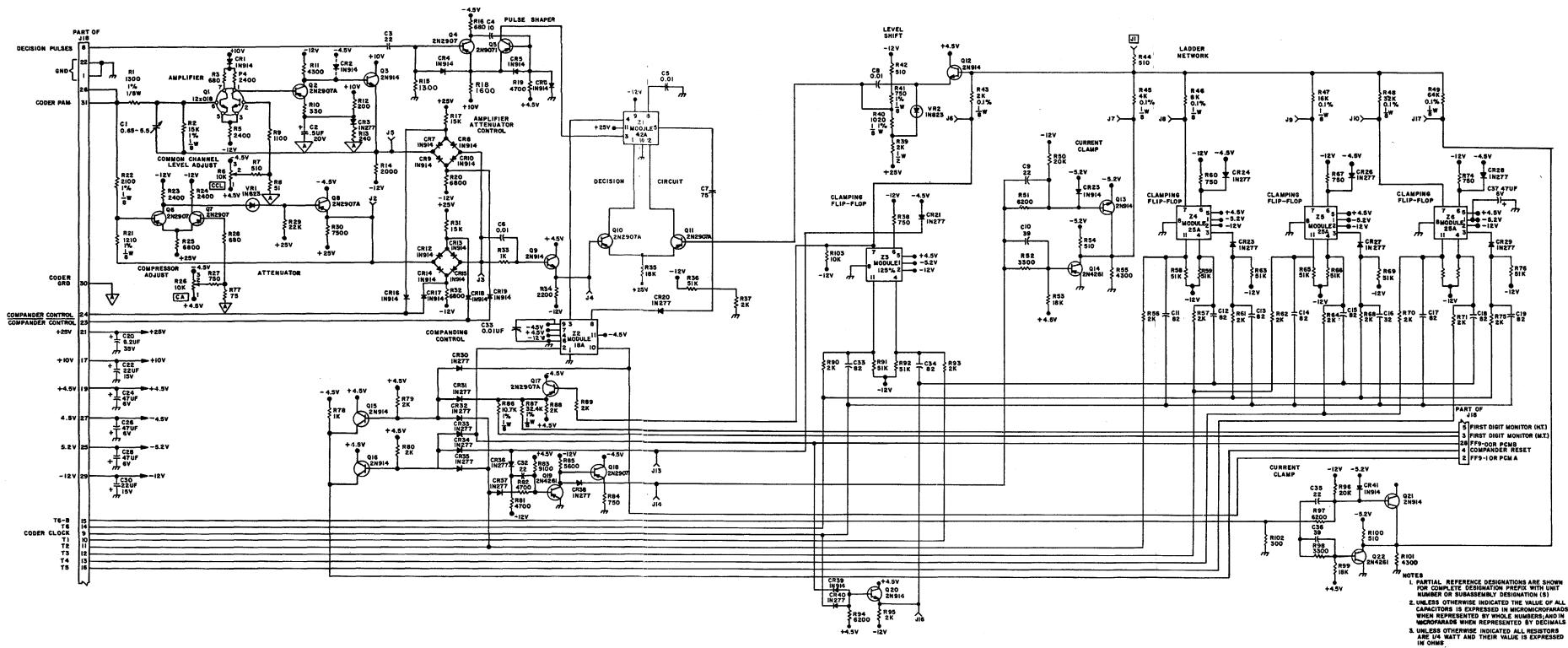

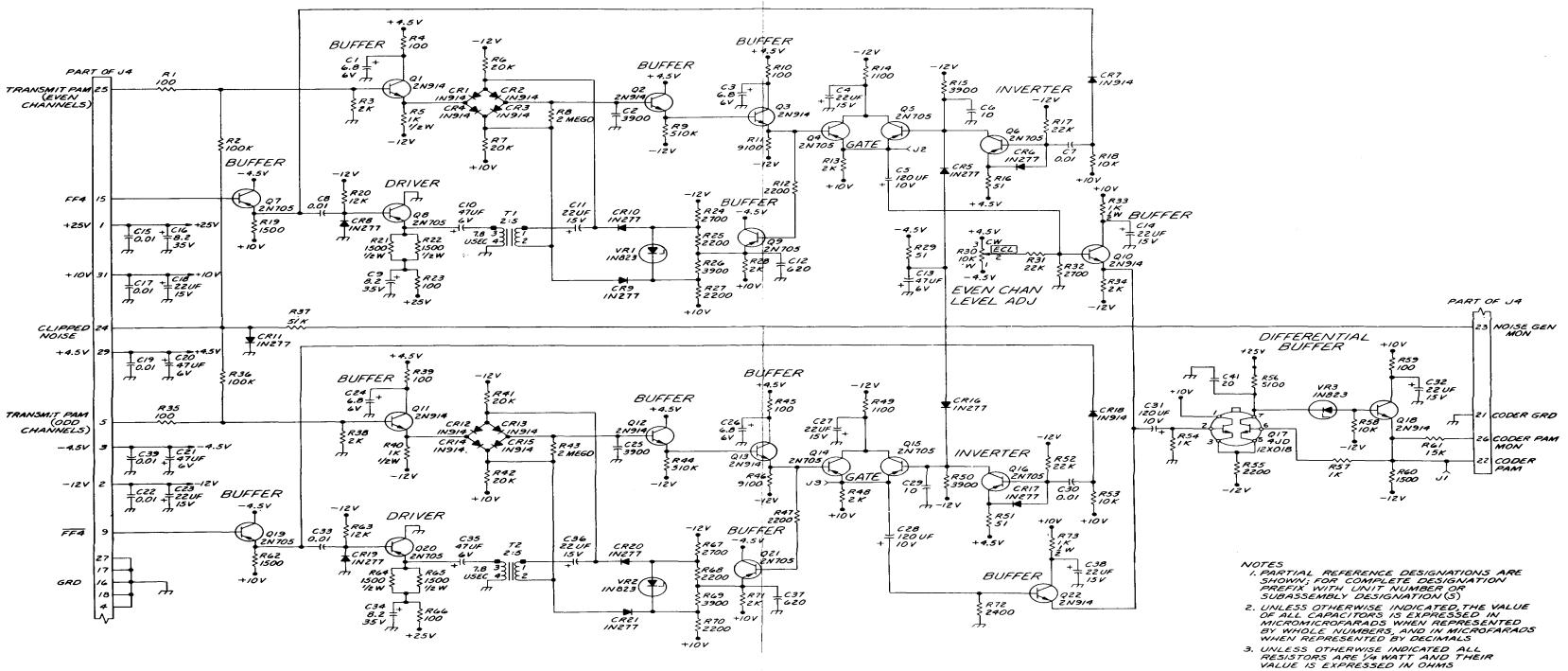

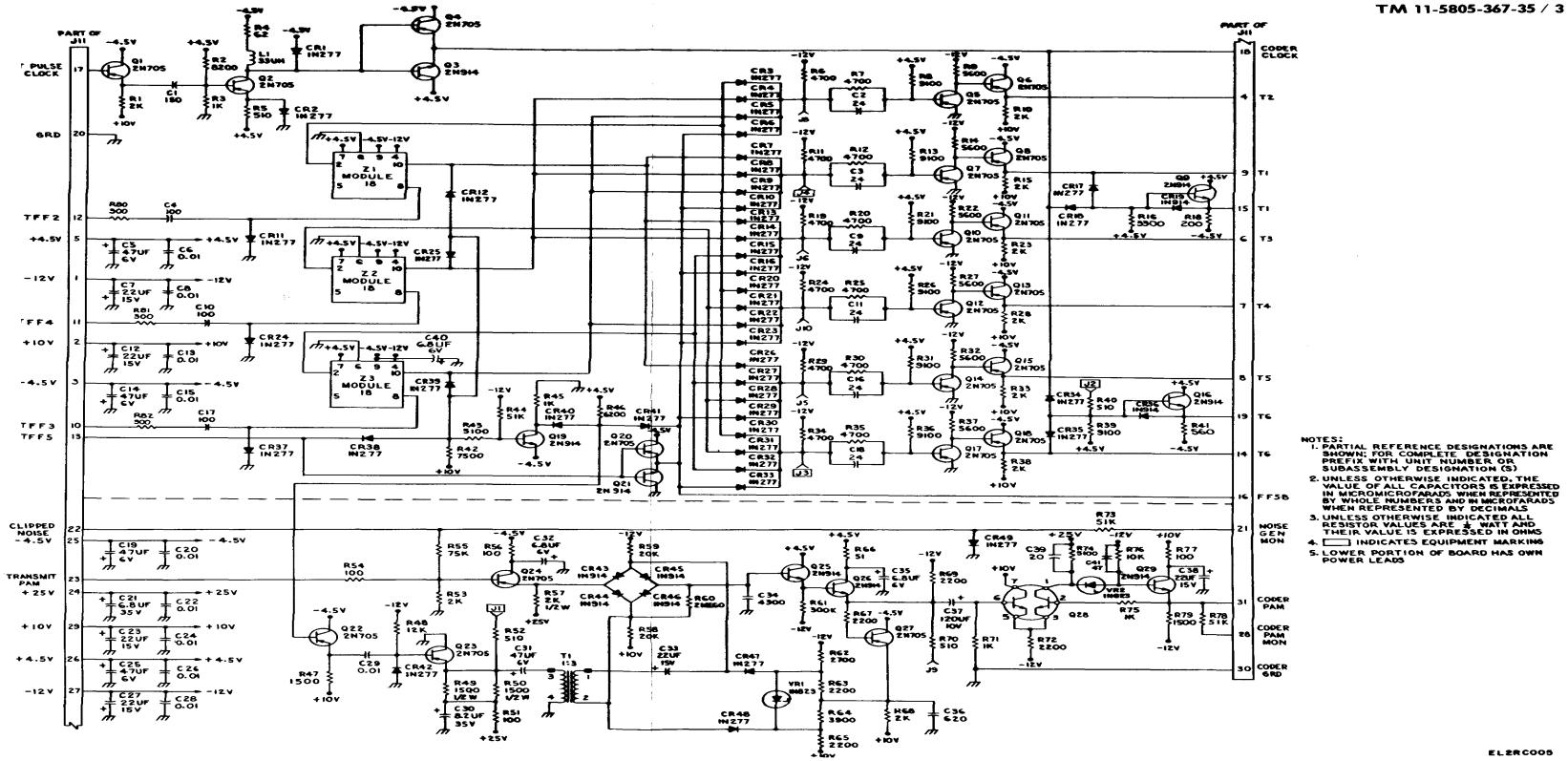

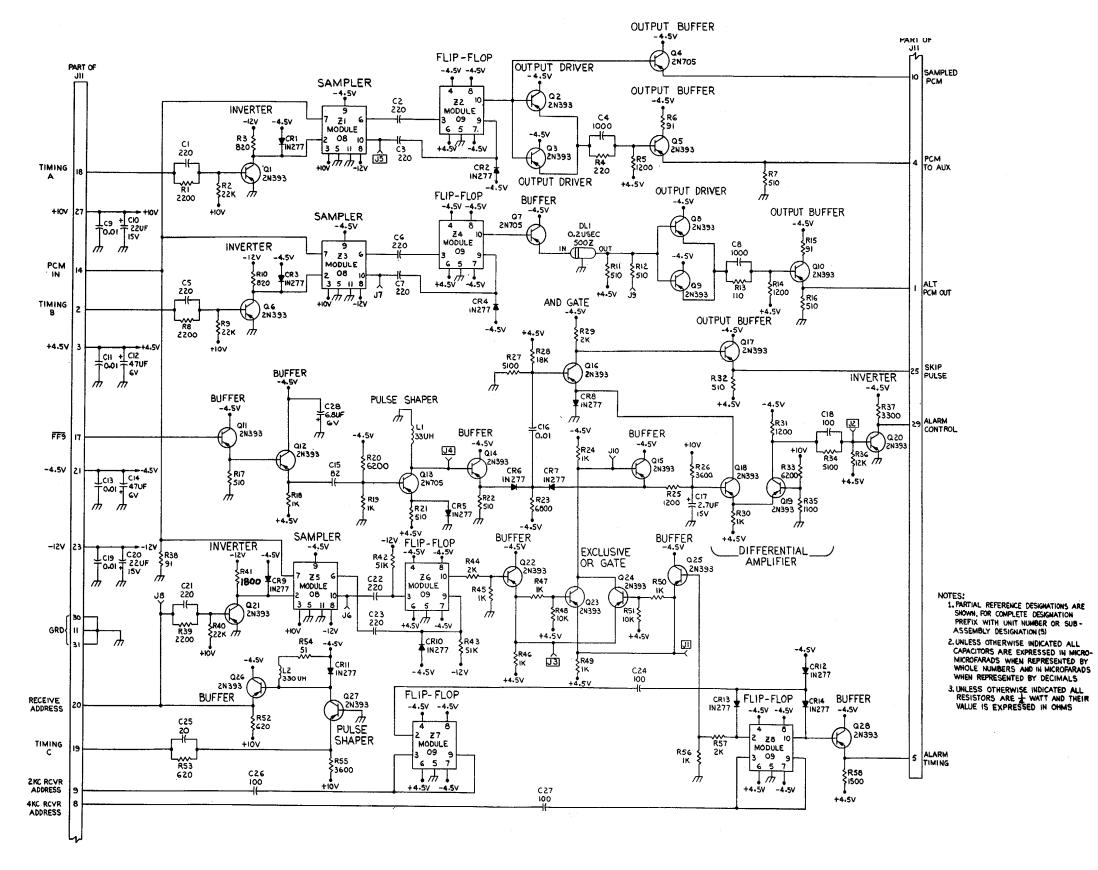

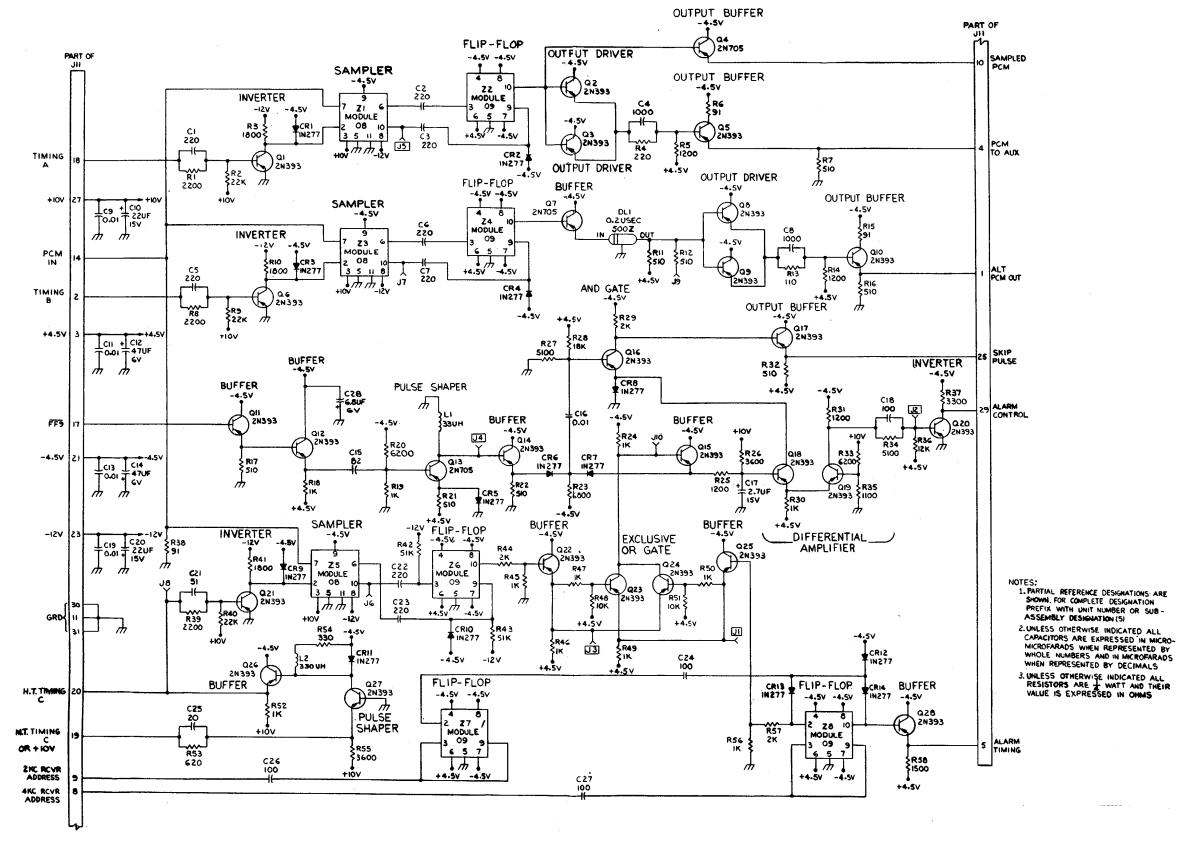

|                    |          | Coder circuits, panel 1A6/2A6                                           |           | 2-43 |

|                    |          | Pam reshaper (hits, panel 1A7                                           |           | 2-46 |

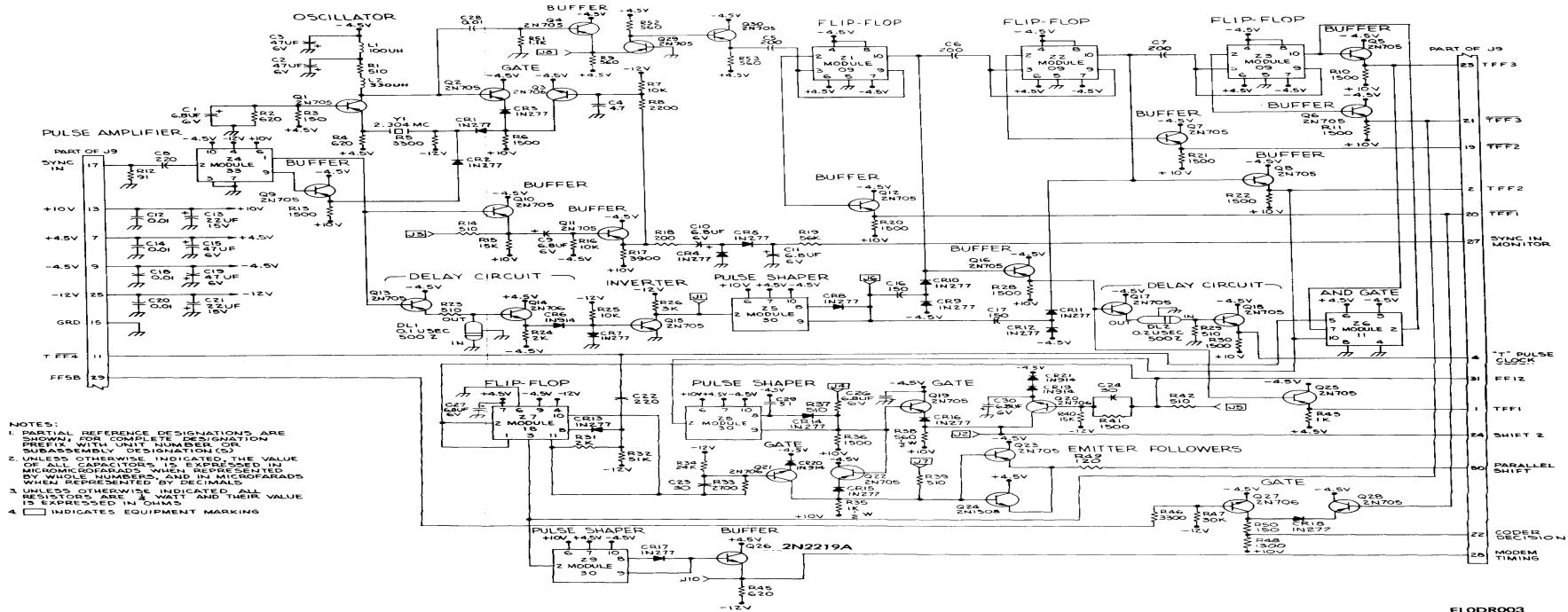

|                    |          | Coder timing and Pam reshaper circuits, panel 2A7                       |           | 2-50 |

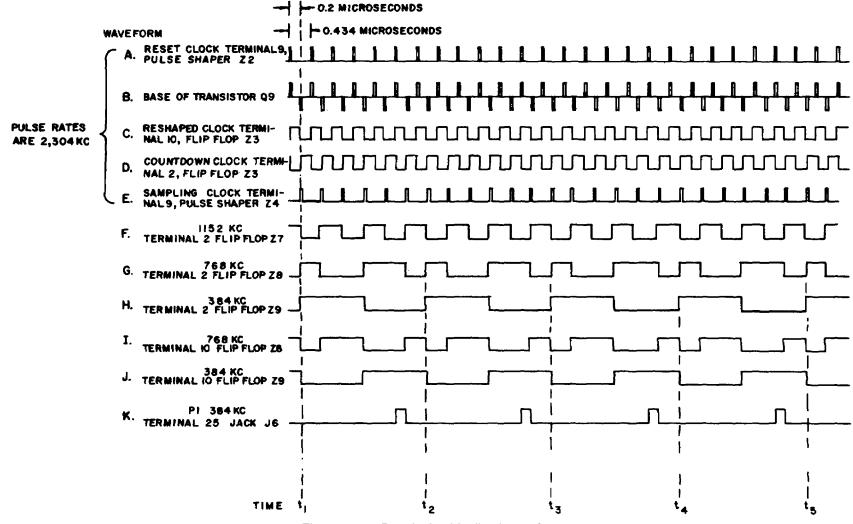

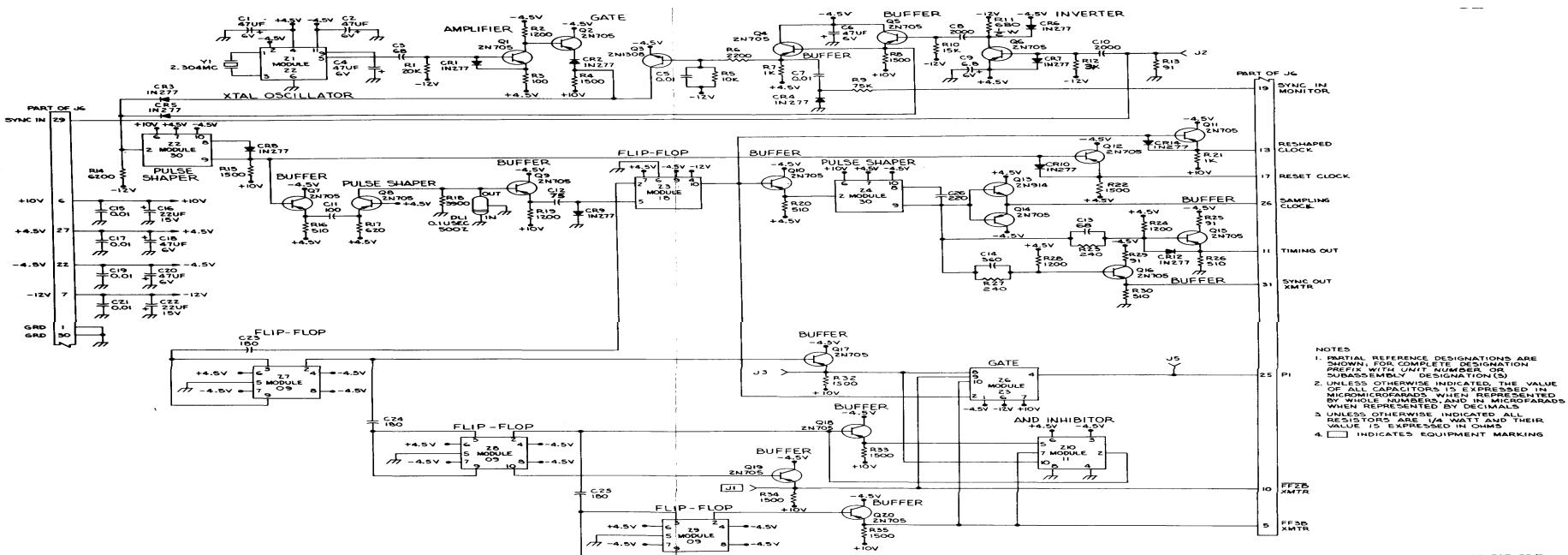

|                    |          | Transmit timing No.1, panel 1A8                                         |           | 2-52 |

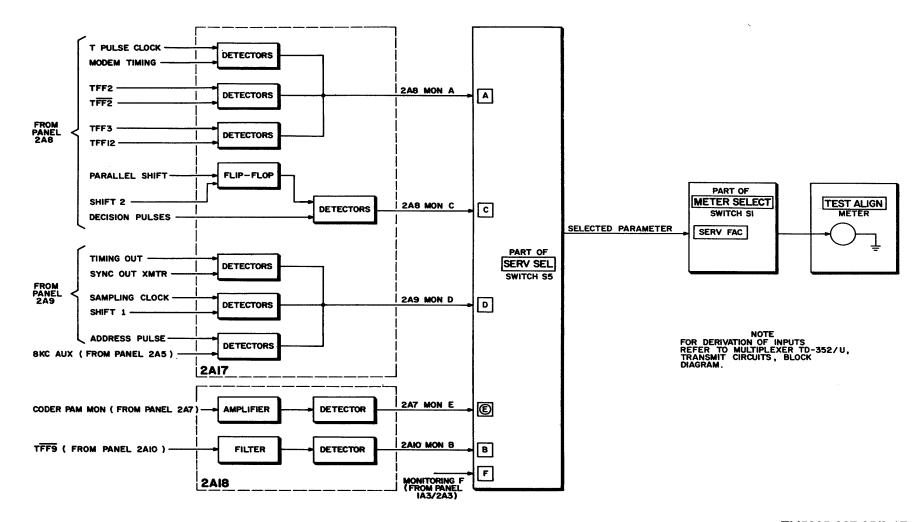

|                    |          | Transmit timing No.1, panel 2A8                                         |           | 2-56 |

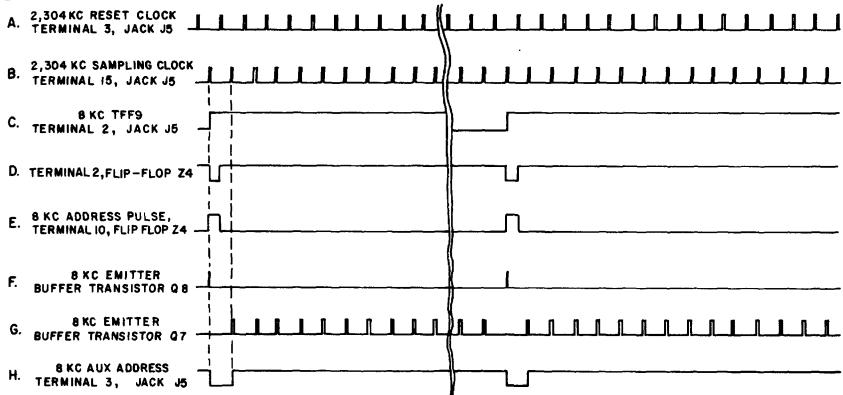

|                    |          | Transmit timing No.2, panel 1A9                                         |           | 2-61 |

|                    |          | Transmit timing No.2, panel 2A9                                         |           | 2-63 |

|                    |          | Transmit timing No.3/receive timing No.2, panel 1A10                    |           | 2-64 |

|                    |          | Transmit timing No.3/receive timing No.2, panel 2A10                    |           | 2-67 |

|                    |          | Noise generator, panel 1A11/2A11                                        |           | 2-67 |

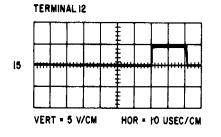

|                    |          | Receive input and framing, panel 1A12/2A12                              |           | 2-68 |

|                    |          | Receive timing No.1, panel 1A13                                         |           | 2-00 |

|                    |          |                                                                         |           | 2-71 |

|                    |          | Receive timing No.1, panel 2A13                                         |           | 2-74 |

|                    |          | Decoder No.1, panel 1A14/2A14                                           |           |      |

|                    |          | Decoder No.2, panel 1A15                                                |           | 2-80 |

|                    |          | Decomder No.2, panel 2A15                                               |           | 2-82 |

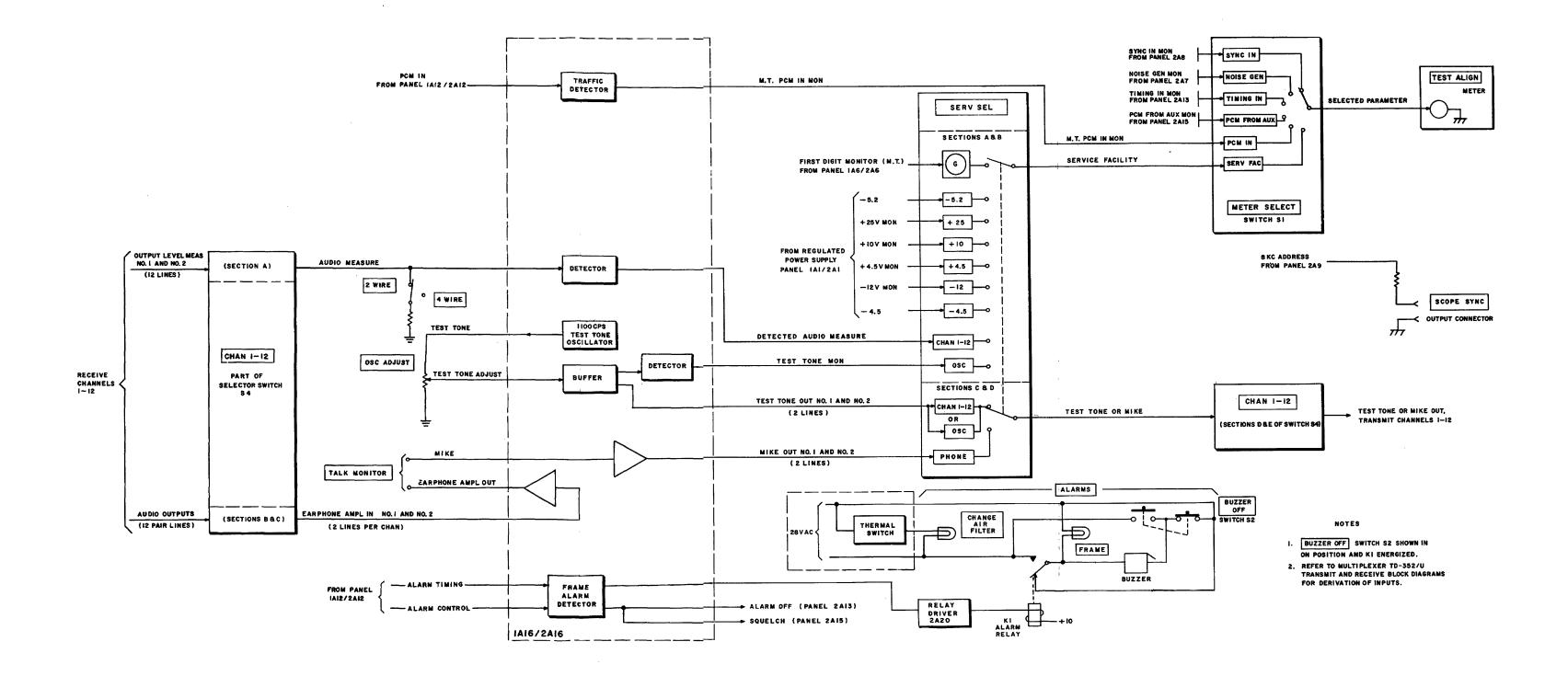

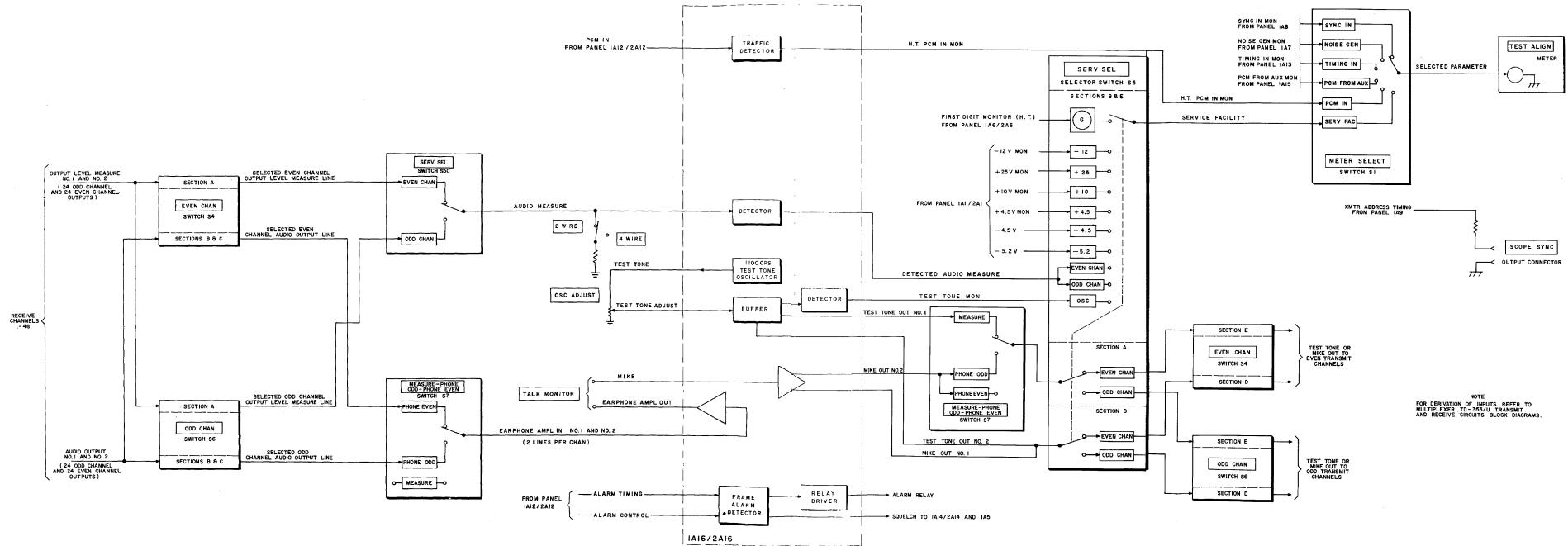

|                    |          | Monitoring and alarm, panel 1A16/2A16                                   |           | 2-84 |

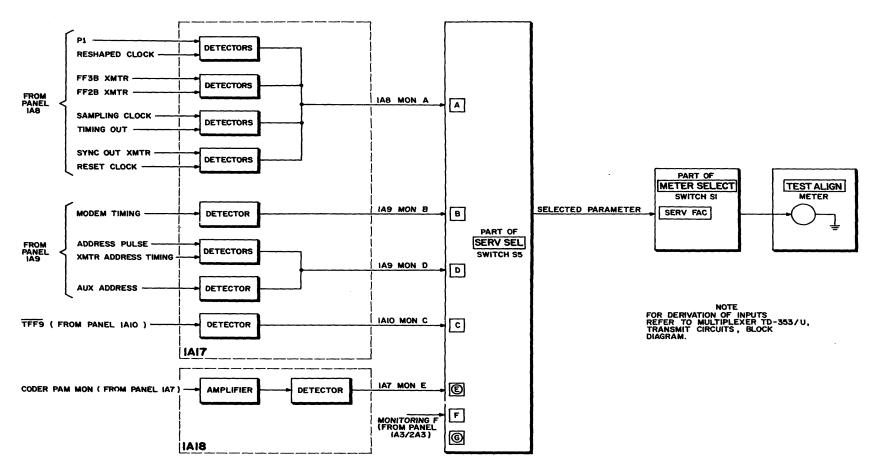

|                    |          | Transmit fault locator, panel 1A17                                      |           | 2-86 |

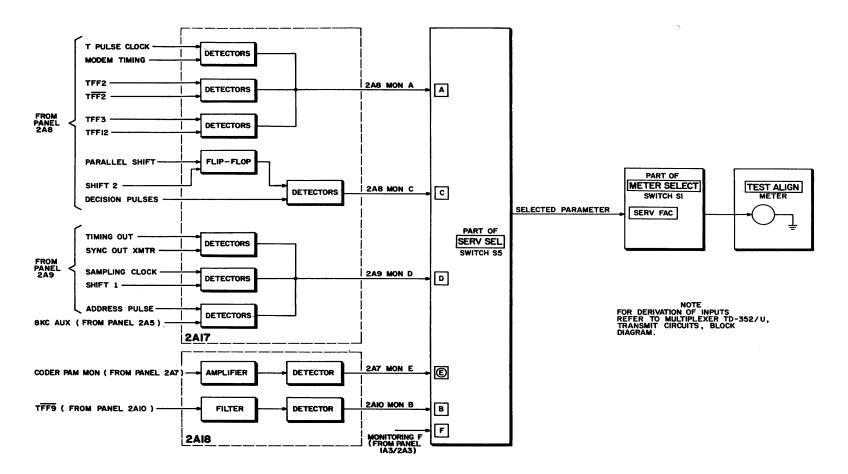

|                    |          | Transmit fault locator, panel 2A17                                      |           | 2-87 |

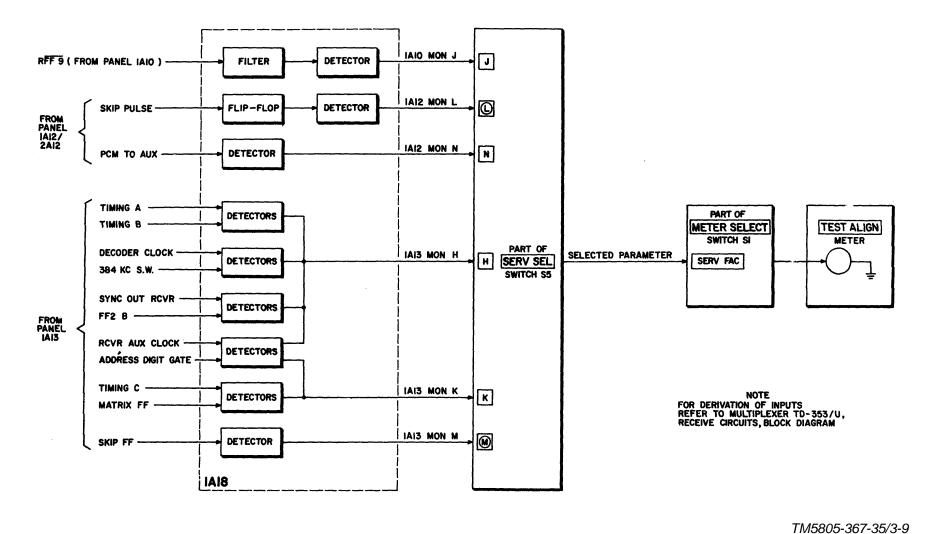

|                    |          | Receive fault locator, panel 1A18                                       |           | 2-88 |

|                    |          | Receive fault locator, panel 2A18                                       |           | 2-89 |

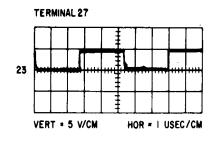

|                    |          | Unregulated power supply, panel 1A19/2A19                               | 2-59      | 2-90 |

| Chapter<br>Section | 3.<br>I. | DIRECT SUPPORT MAINTENANCE<br>Troubleshooting at Direct Support         |           |      |

|                    |          | General                                                                 | 3-1       | 3-1  |

|                    |          | Use of troubleshooting charts                                           | 3-2       | 3-1  |

|                    |          | Continuity checks                                                       |           | 3-1  |

|                    |          | Mechanical maintenance                                                  |           | 3-2  |

|                    |          | Test equipment, tools, and materials required                           |           | 3-2  |

|                    |          | Multiplexer TD-352/U troubleshooting procedure                          |           | 3-2  |

|                    |          | Multiplexer TD-353/U troubleshooting procedure                          |           | 3-6  |

|                    | II.      | Alignment                                                               |           |      |

|                    |          | General                                                                 |           | 3-10 |

|                    |          | Switch settings and preliminary procedures                              |           | 3-11 |

|                    |          | Preliminary coder adjustment (panel IA6/2A6)                            | 3-10      | 3-11 |

|                    |          | Decoder alignment (panel IA 15 or 2A 15)                                | 3-11      | 3-11 |

|                    |          | Multiplexer TD-352/U pam level adjustment (panels 1A2/2A2 and 1A6/2A6). |           | 3-12 |

|                    |          | Multiplexer TD-353/U pam level adjustment(panels 1A1/2A1,1A6/2A6,and 1/ |           | 3-12 |

|                    |          | Final decoder alignment (panel 1A15 or 2A15}                            | 3-14      | 3-13 |

| Chapter<br>Section | 4.<br>I. | GENERAL SUPPORT MAINTENANCE Introduction                                |           |      |

| Conton             | 1.       | Scope of general support maintenance procedures                         | 4-1       | 4-1  |

|                    |          |                                                                         |           |      |

|                                            | Paragraph | Page |

|--------------------------------------------|-----------|------|

| Organization of troubleshooting procedures | 4-2       | 4-1  |

| Use of troubleshooting charts              |           | 4-1  |

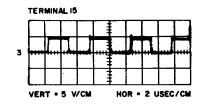

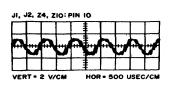

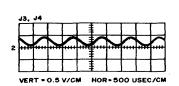

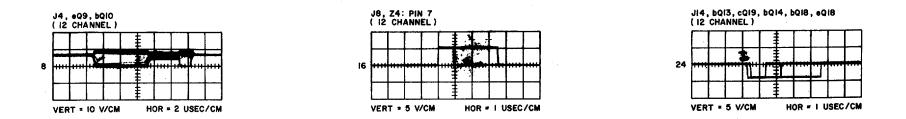

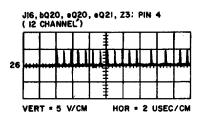

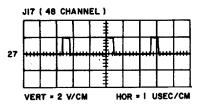

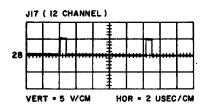

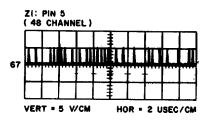

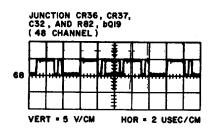

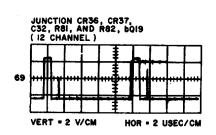

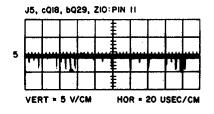

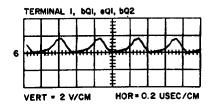

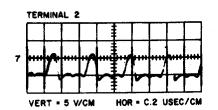

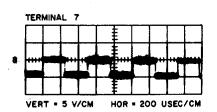

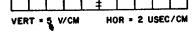

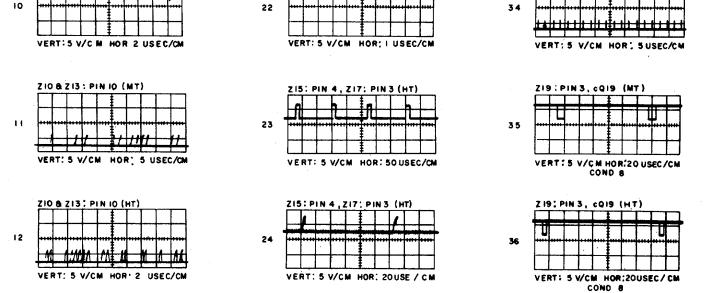

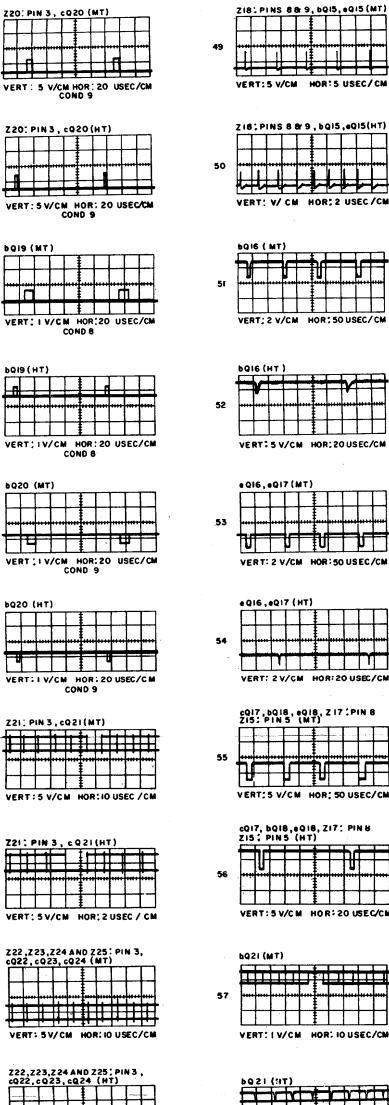

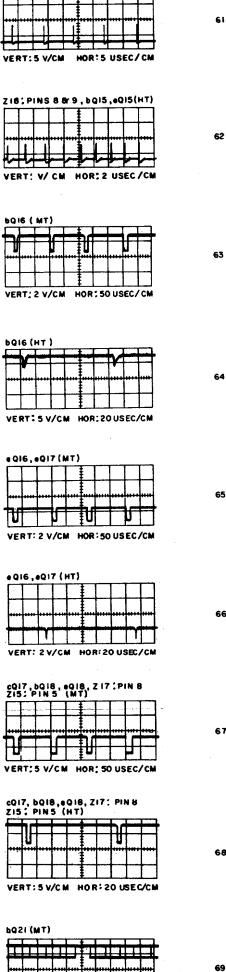

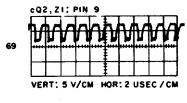

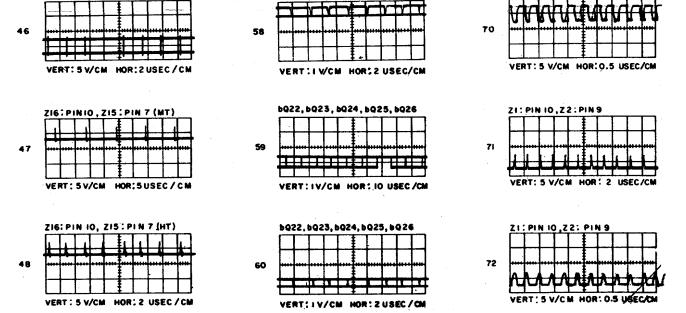

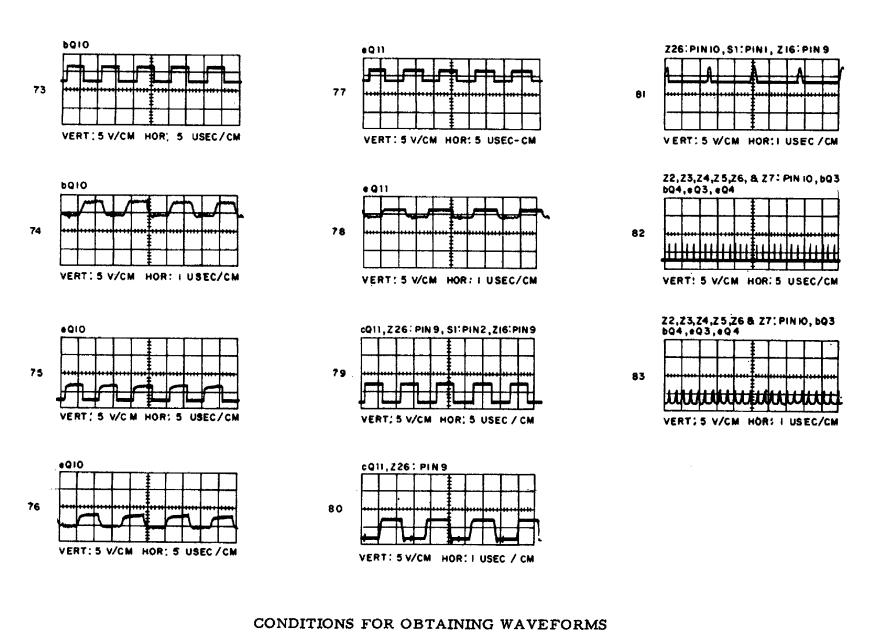

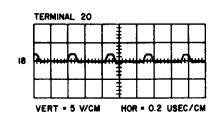

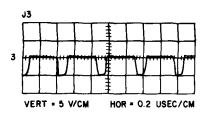

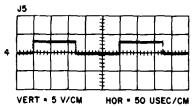

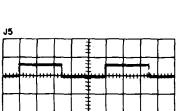

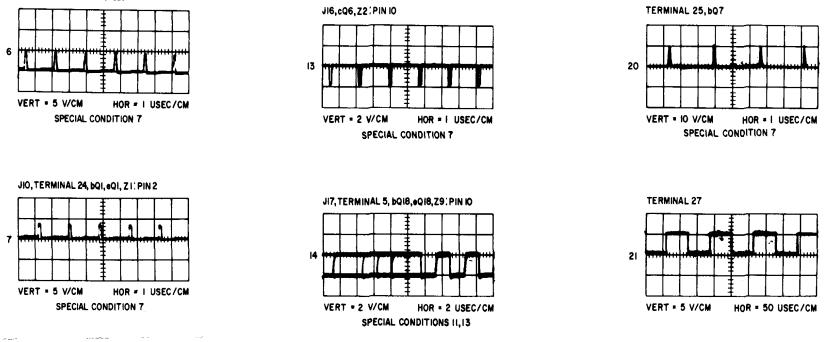

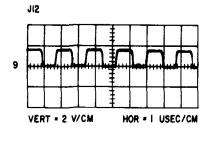

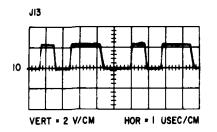

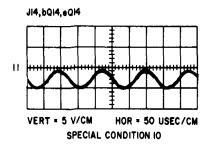

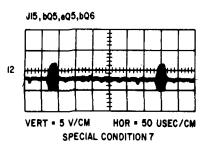

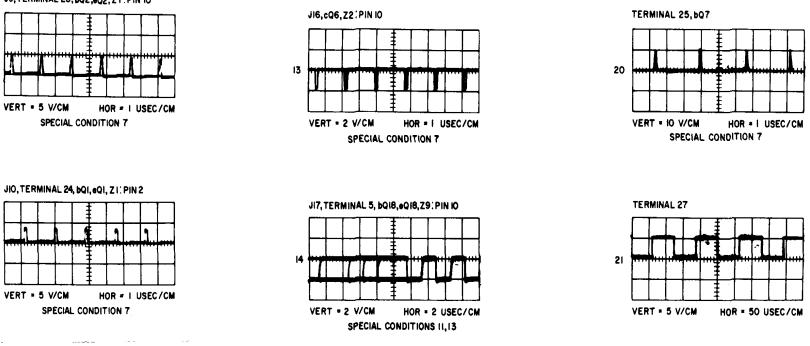

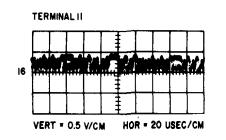

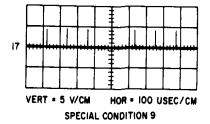

| Use of waveforms                           |           | 4-2  |

| Test equipment and tools required          |           | 4-2  |

| II. Troubleshooting at General Support     |           |      |

| Panel 1A1/2A1, troubleshooting             |           | 4-2  |

| Panel 1A2/2A2, troubleshooting             |           | 4-8  |

| Panel 1A3/2A2, troubleshooting             |           | 4-11 |

| Panel 1A5, troubleshooting                 |           | 4-13 |

| Panel 2A5, troubleshooting                 |           | 4-16 |

| Panel 1A6/2A6. troubleshooting             |           | 4-18 |

| Panel 1A7, troubleshooting                 | 4-12      | 4-24 |

| Panel 2AT, troubleshooting                 |           | 4-26 |

| Panel 1A8, troubleshooting                 |           | 4-30 |

| Panel 2A8, troubleshooting                 |           | 4-33 |

| Panel 1A9, troubleshooting                 |           | 4-38 |

| Panel 2A9, troubleshooting                 | 4-17      | 4-40 |

TM 11-5805-367-35/3

|            |                                                                                                                           | TM 11-5805-3 | 67-35/3    |

|------------|---------------------------------------------------------------------------------------------------------------------------|--------------|------------|

|            |                                                                                                                           | Paragraph    | Page       |

|            | Panel 1A10, troubleshooting                                                                                               |              | 4-42       |

|            | Panel 2A10, troubleshooting                                                                                               |              | 4-48       |

|            | Panel 1A11/2A11 troubleshooting                                                                                           | 4-20         | 4-53       |

|            | Panel 1A12/2A12, troubleshooting                                                                                          |              | 4-54       |

|            | Panel 1A13, troubleshooting                                                                                               |              | 4-57       |

|            | Panel 2A13, troubleshooting                                                                                               |              | 4-65       |

|            | Panel 1A14/2A14, troubleshooting                                                                                          |              | 4-70       |

|            | Panel 1A15, troubleshooting                                                                                               |              | 4-75       |

|            | Panel 2A15, troubleshooting                                                                                               |              | 4-77       |

|            | Panel 1A16/2A16, troubleshooting                                                                                          |              | 4-78       |

|            | Panel 1A17, troubleshooting                                                                                               |              | 4-80       |

|            | Panel 2A17, troubleshooting                                                                                               |              | 4-84       |

|            | Panel 1A18, troubleshooting                                                                                               |              | 4-88       |

|            | Panel 2A18, troubleshooting                                                                                               |              | 4-92       |

|            | Panel 1A19/2A19, troubleshooting                                                                                          |              | 4-96       |

| III.       | Alignment                                                                                                                 |              | + 50       |

|            | General                                                                                                                   | 1-33         | 4-98       |

|            | Panel 1A1/2A1, - 5.2 volt regulated output voltage adjustment                                                             |              | 4-98       |

|            | Panel 1A6/2A6, capacitor C1 adjustment                                                                                    |              | 4-98       |

| Chapter 5. | GENERAL SUPPORT TESTING PROCEDURES                                                                                        |              | 4-90       |

| Chapter 5. |                                                                                                                           | <b>5</b> 1   | 5-1        |

|            | General                                                                                                                   |              | 5-1        |

|            | Test equipment, materials, and other equipment                                                                            |              |            |

|            | Modification work orders                                                                                                  |              | 5-1<br>5-2 |

|            | Physical tests and inspection                                                                                             |              |            |

|            | Performance tests (TD-352/U)                                                                                              |              | 5-5        |

|            | Summary of performance standard (TD-352/U)                                                                                |              | 5-13       |

|            | Performance tests (TD-353/U)                                                                                              |              | 5-17       |

| 6.         | Summary of performance standard (TD-353/U)<br>DEPOT OVERHAUL STANDARDS                                                    |              | 5-25       |

|            | Applicability of depot overhaul standards                                                                                 |              | 6-1        |

|            | Deleted                                                                                                                   | 6-2          | 6-1        |

|            | Deleted                                                                                                                   | 6-3          | 6-1        |

| APPENDIX A | REFERENCES                                                                                                                |              | A-1        |

|            | LIST OF ILLUSTRATIONS                                                                                                     |              | _          |

| Fig.#      | Title                                                                                                                     |              | Page       |

| 2-1 M      | ultiplexer TD.352/U transmit fault locator circuits, block diagram                                                        |              | 2-5        |

|            | ultiplexer TD-352/U receive fault locator circuits, block diagram                                                         |              |            |

|            | ultiplexers TD.352/U and TD.353/U power supply circuits, block dia                                                        |              |            |

|            | ultiplexer TD-353/U transmit fault locator circuits, block diagram                                                        |              |            |

|            | ultiplexer TD-353/U receive fault locator circuits, block diagram                                                         |              |            |

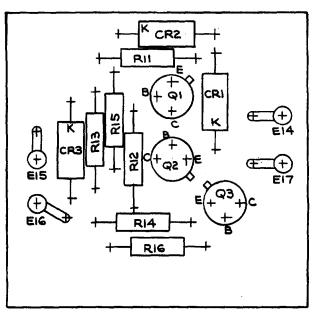

|            | ate module 01, schematic diagram                                                                                          |              |            |

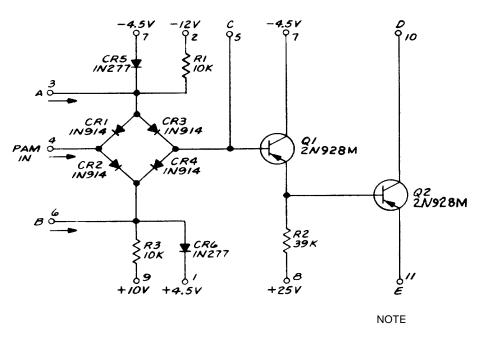

|            | ampler module 08, schematic diagram                                                                                       |              |            |

|            | ip-flop module 09, schematic diagram                                                                                      |              |            |

|            | AND gate module 11, schematic diagram                                                                                     |              |            |

|            | nitter-follower module 15, schematic diagram                                                                              |              |            |

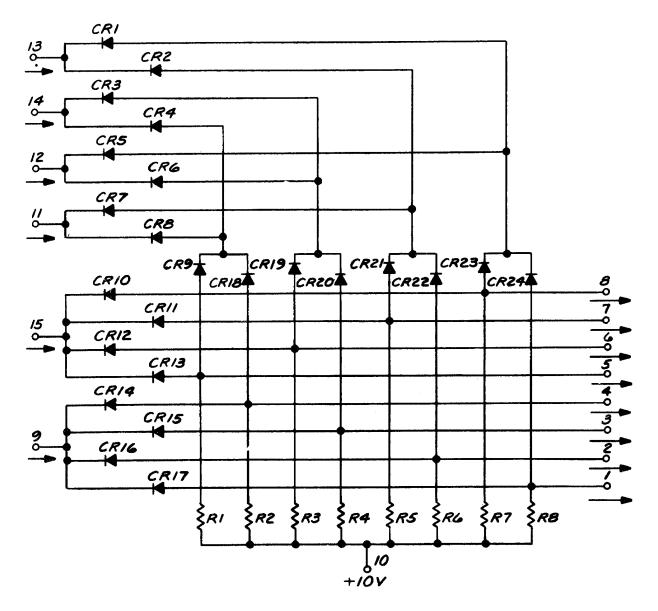

| -          | atrix module 16, schematic diagram                                                                                        |              |            |

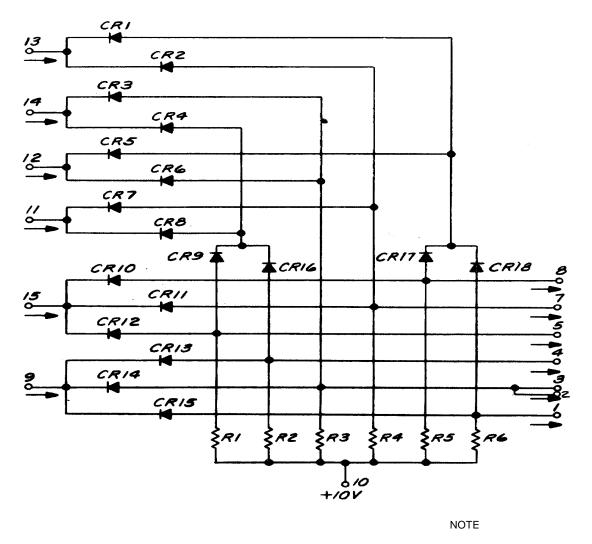

|            | atrix module 17, schematic diagram                                                                                        |              |            |

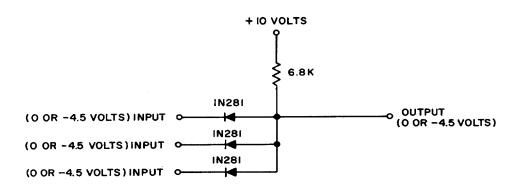

|            | atrix modules 16 and 17, AND gate form                                                                                    |              |            |

|            | ip-flop module 18, schematic diagram                                                                                      |              |            |

|            | scillator module 22, schematic diagram                                                                                    |              |            |

|            | ate module 23, schematic diagram                                                                                          |              |            |

|            | amping flip-flop module 25 or 125, schematic diagram                                                                      |              |            |

|            | amping flip-flop module 25 of 125, schematic diagramamping flip-flop module 25, external circuitry for one-and two-termir |              |            |

| ∠-10 U     | מחקוווש חוף חסטטופ בס, פאנפוזומו טוכעונוץ וטו טוופ-מווע נשט-נפוזווו                                                       |              |            |

#### LIST OF ILLUSTRATIONS-Continued

|         | LIST OF ILLUSTRATIONS-Continued                                             |      |

|---------|-----------------------------------------------------------------------------|------|

| Fig.#   | Title                                                                       | Page |

| 2-19    | Pulse shaper module 30, schematic diagram                                   |      |

| 2-20    | Audio preamplifler module 31, schematic diagram                             |      |

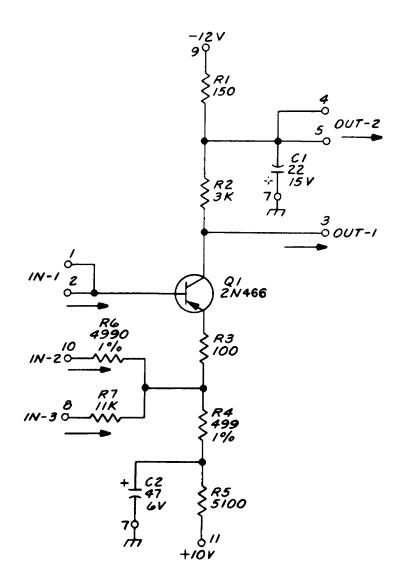

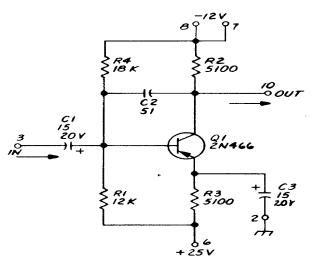

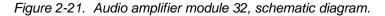

| 2-21    | Audio amplifier module 32, schematic diagram                                |      |

| 2-22    | Pulse amplifier module 33, schematic dia gram                               |      |

| 2-23    | Dual AND gate module 35, schematic diagram                                  |      |

| 2-24    | Detector module 36, schematic diagram                                       |      |

| 2-25    | Receiver sampler module 37, schematic diagram                               |      |

| 2-26    | Transmit sampler module 38, schematic diagram                               |      |

| 2-27    | Decision circuit module 42, schematic diagram                               |      |

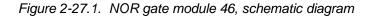

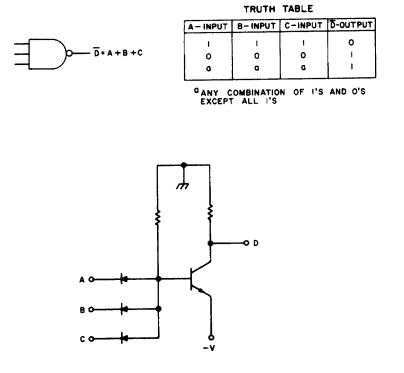

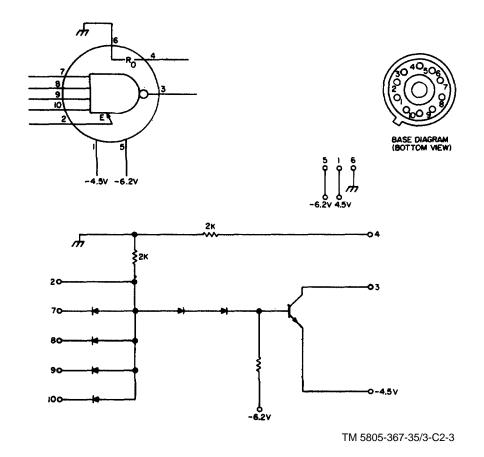

| 2-27.1  | NOR gate module 46, schematic diagram                                       |      |

| 2-27.2  | Basic NAND gate                                                             |      |

| 2-27.3  | NAND gate SE101K, basic application and schematic diagram                   |      |

| 2-27.4  | High fan out dual NAND gate SE113K, basic application and schematic diagram |      |

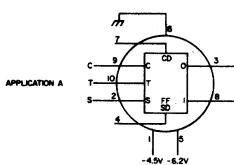

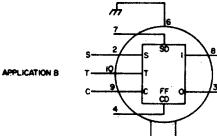

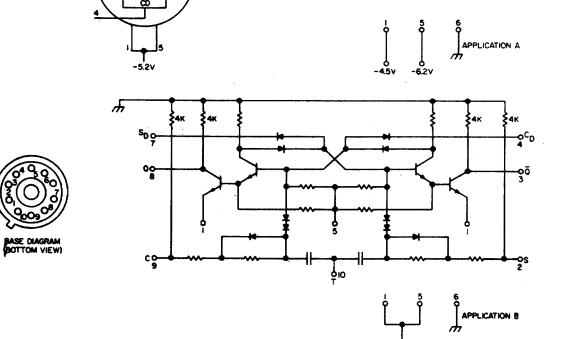

| 2-27.5  | Flip-flop SE124K. basic application and schematic diagram                   |      |

| 2-27.6  | Line driver SE150K, basic application and schematic diagram                 |      |

| 2-27.7  | NAND gate module SE157K, basic application and schematic diagram            |      |

| 2-27.8  | Monostable multivabrator SE160K, basic application and schematic diagram    |      |

| 2-27.9  | NAND gates SE181K, basic application and schematic diagram                  |      |

| 2-27.10 | Flip-flop CS704K, basic application and schematic diagram                   |      |

| 2-28    | Automatic short circuit protection circuit, simplified schematic diagram    |      |

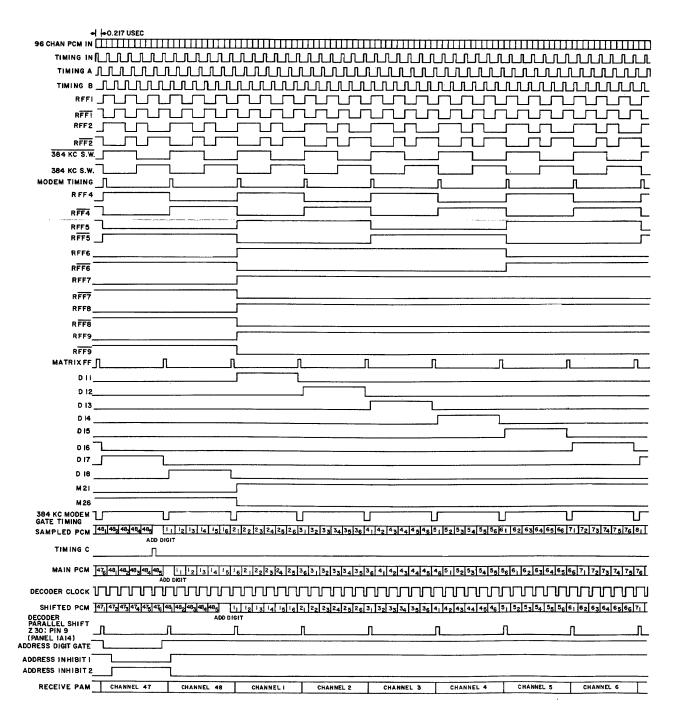

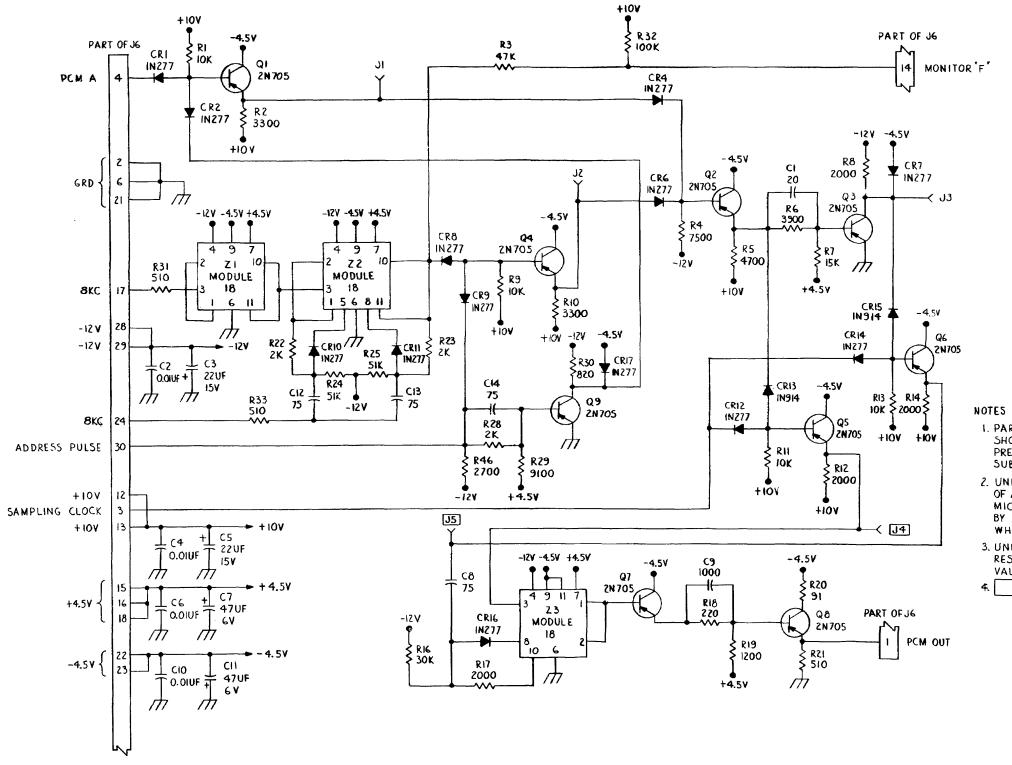

| 2-291   | Panel 1A6/2A6, idealized waveforms (part 1 of 2)                            |      |

| 2-29©   | Panel 1A6/2A6, idealized waveforms (part 2 of 2)                            |      |

| 2-30    | Panel 1A8. idealized waveforms                                              |      |

| 2-31    | Panel 1A9, address pulse and aux address circuit, idealized waveforms       |      |

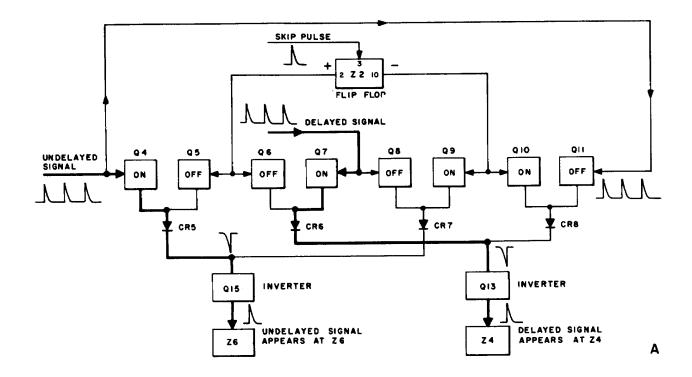

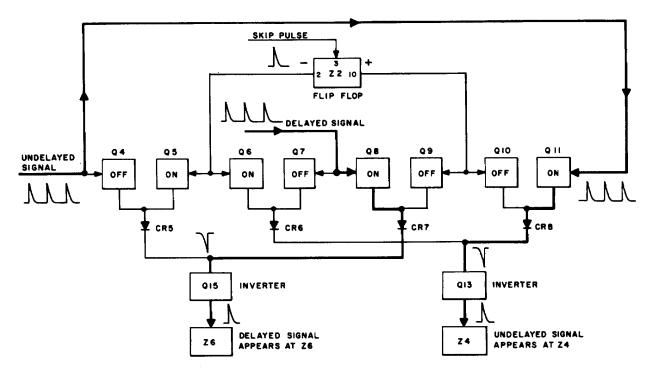

| 2-32    | Delayed/undelayed timing signal gate circuit                                |      |

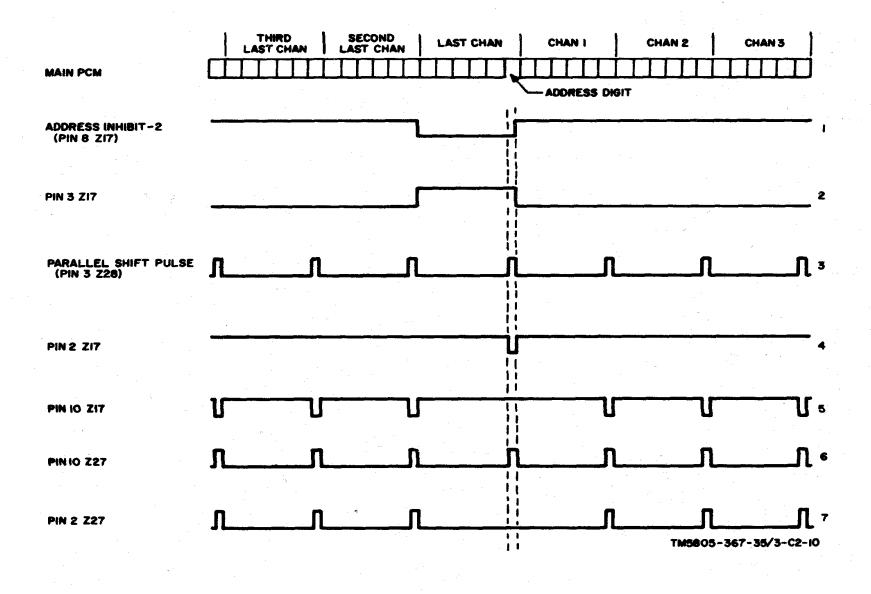

| 2-32.1  | Address inhibit circuit, idealized waveforms                                |      |

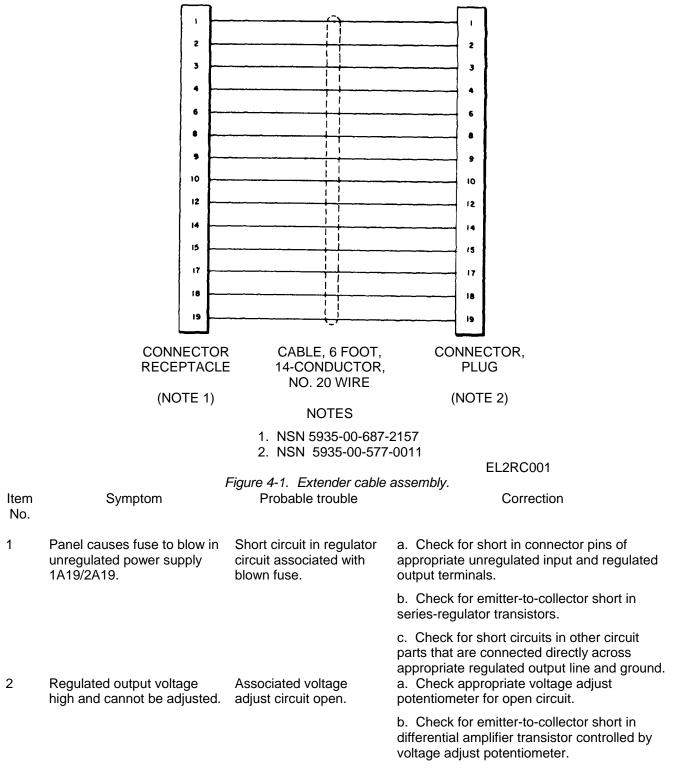

| 4-1     | Extender cable assembly                                                     | 4-3  |

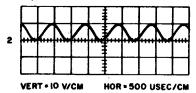

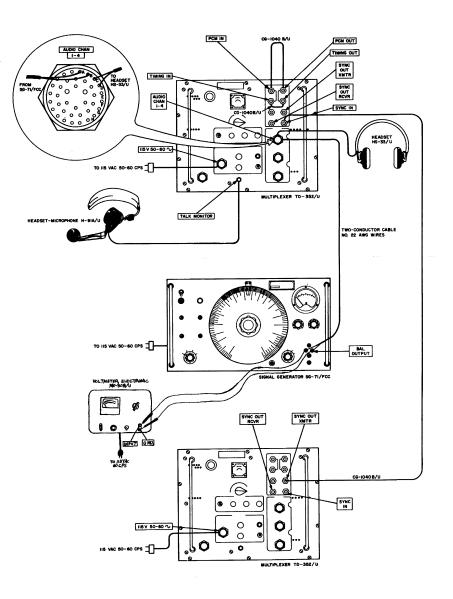

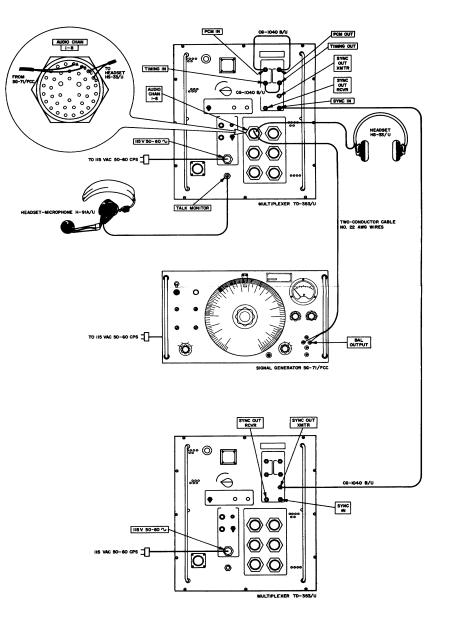

| 5-1     | Multiplexer TD-352/U, performance test setup                                |      |

| 5-2     | Multiplexer TD-353/U, performance test setup                                |      |

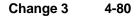

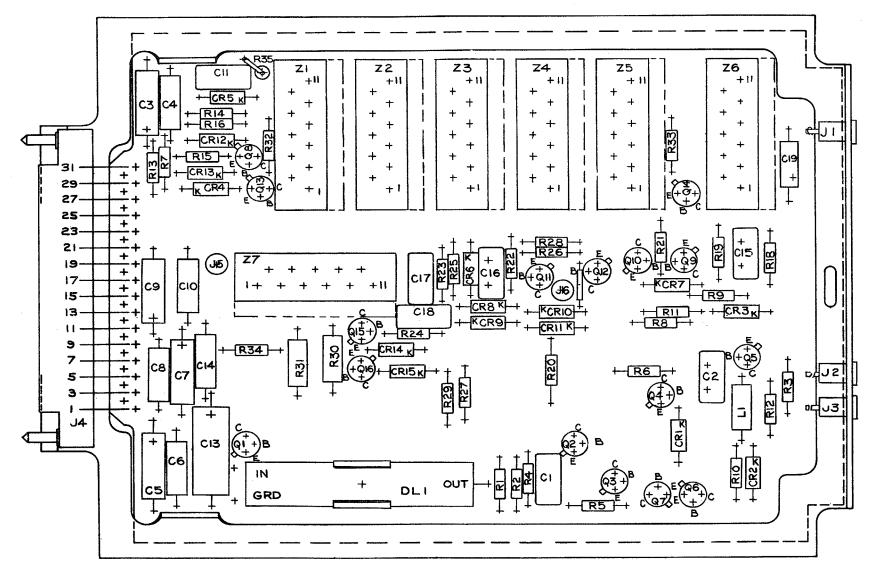

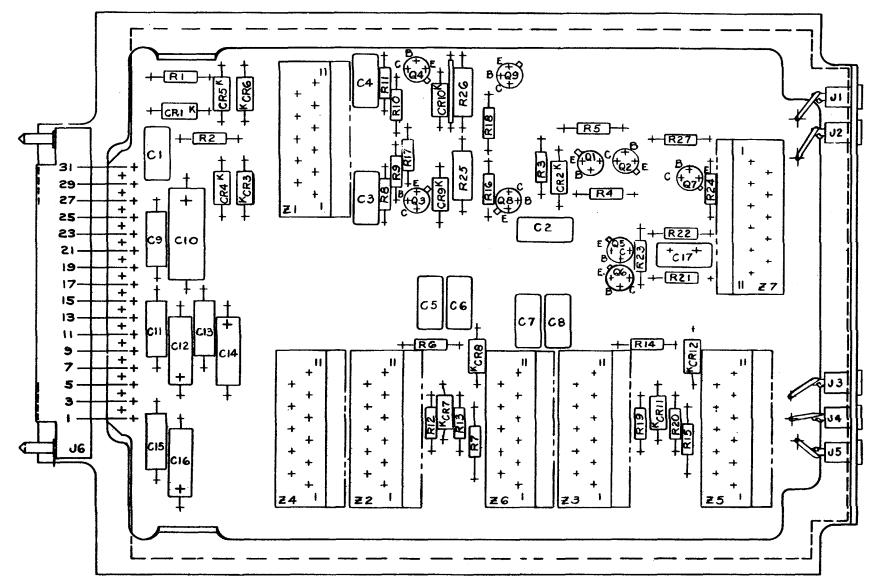

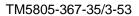

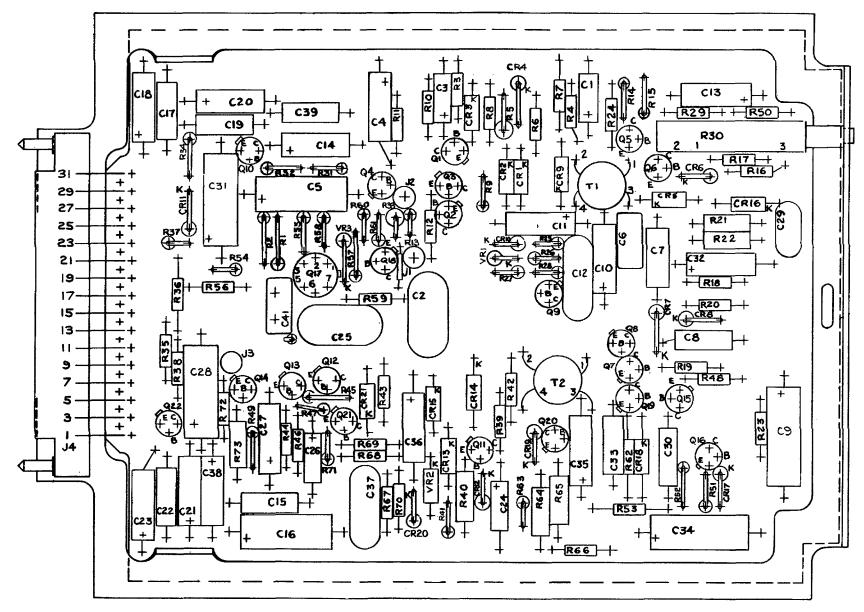

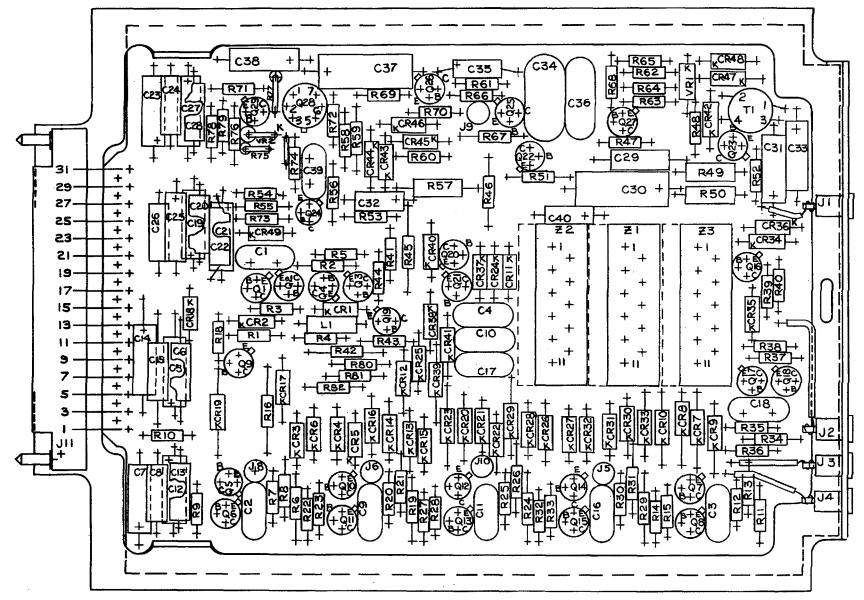

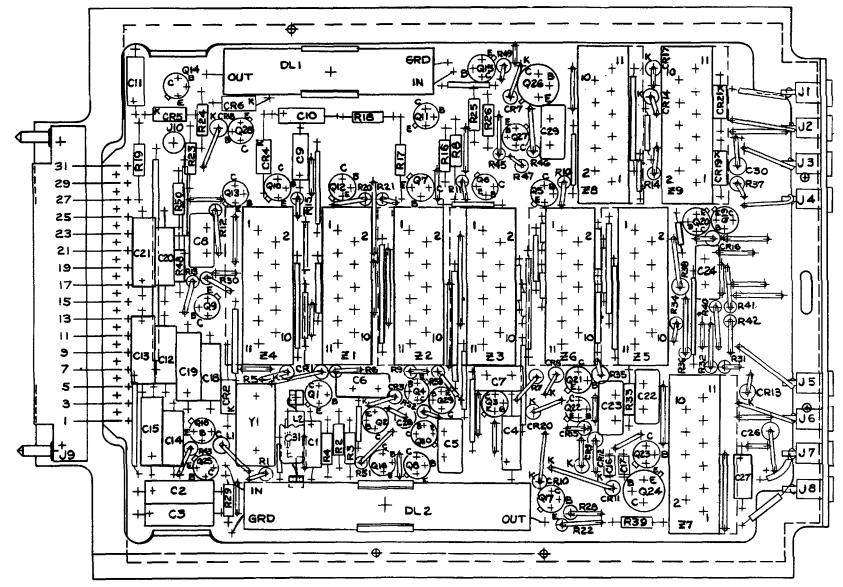

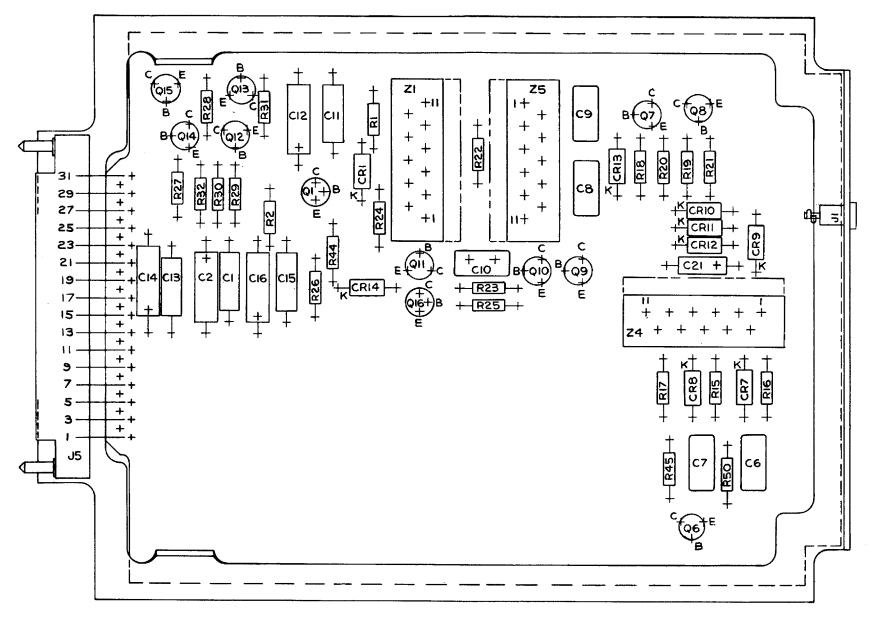

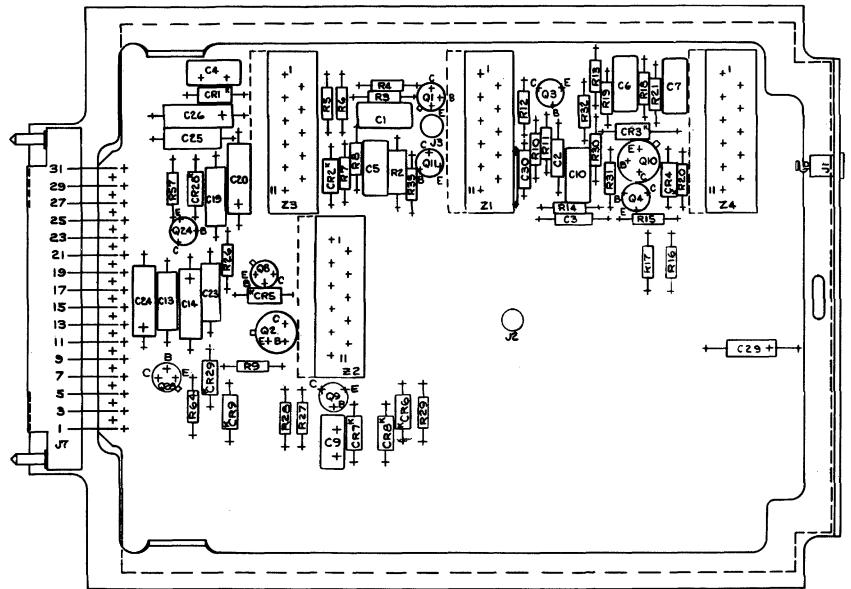

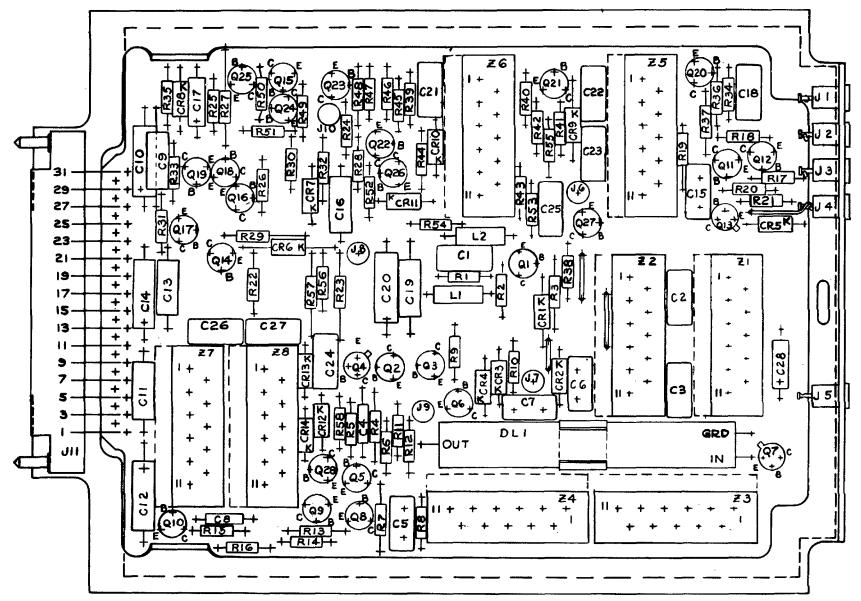

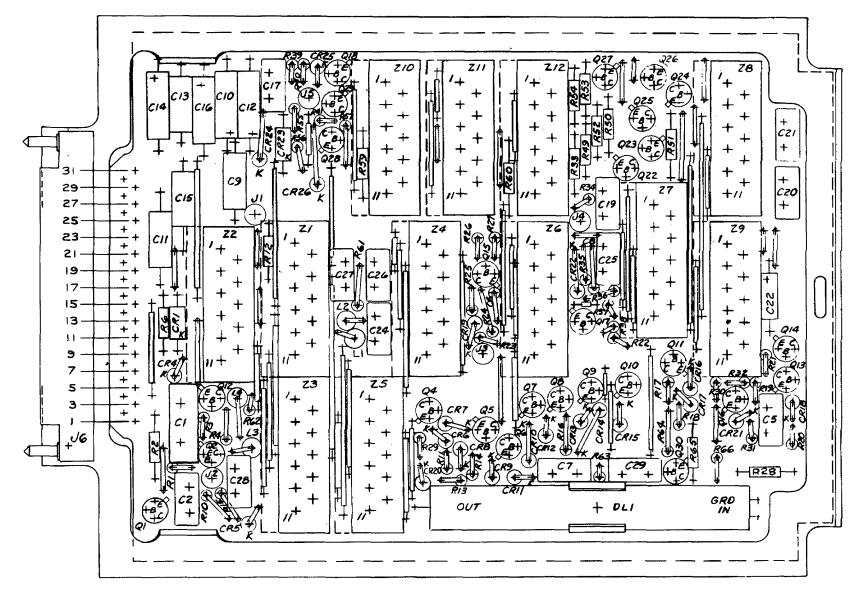

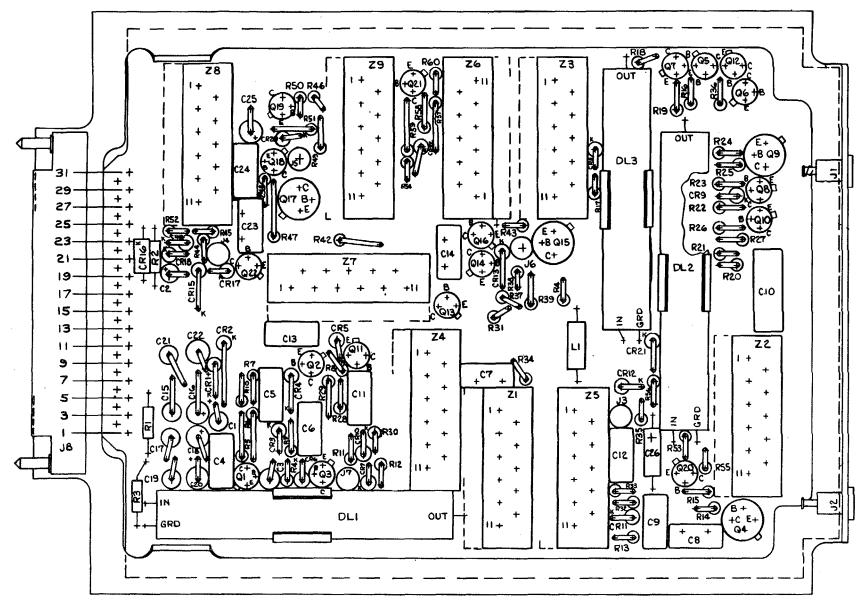

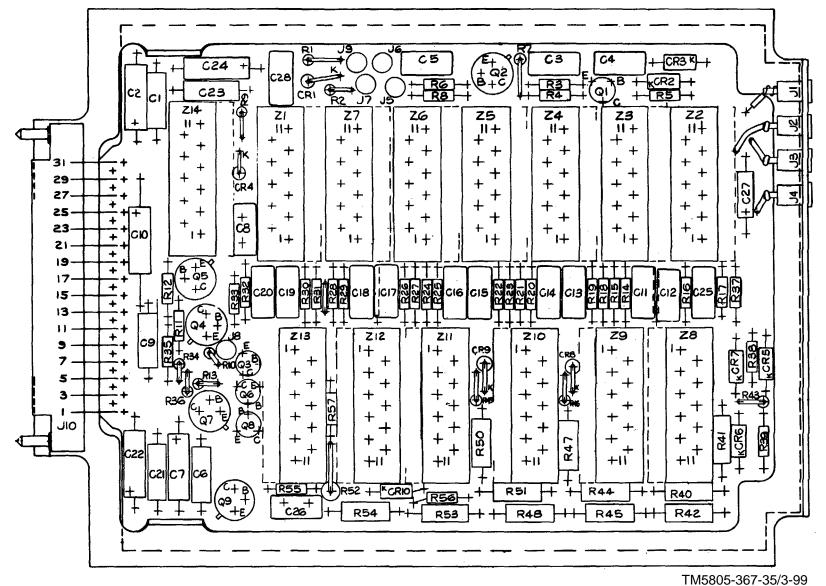

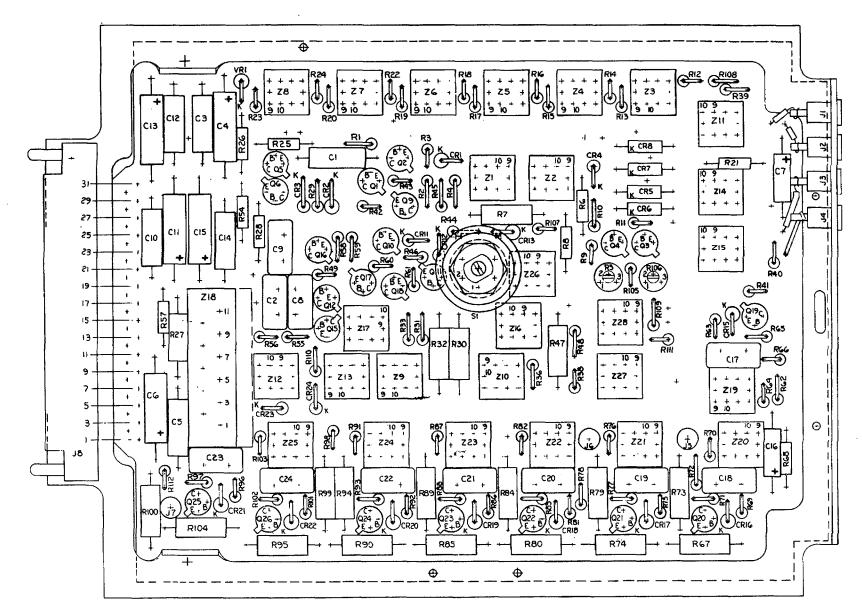

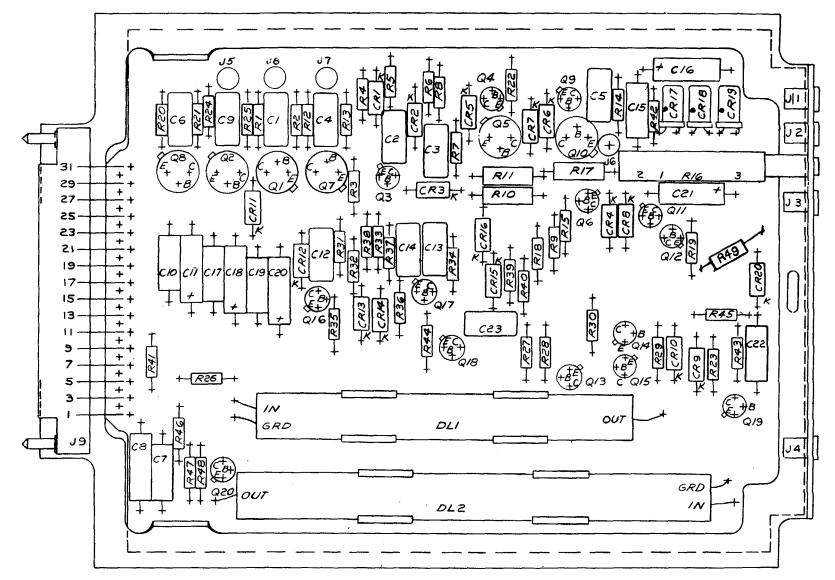

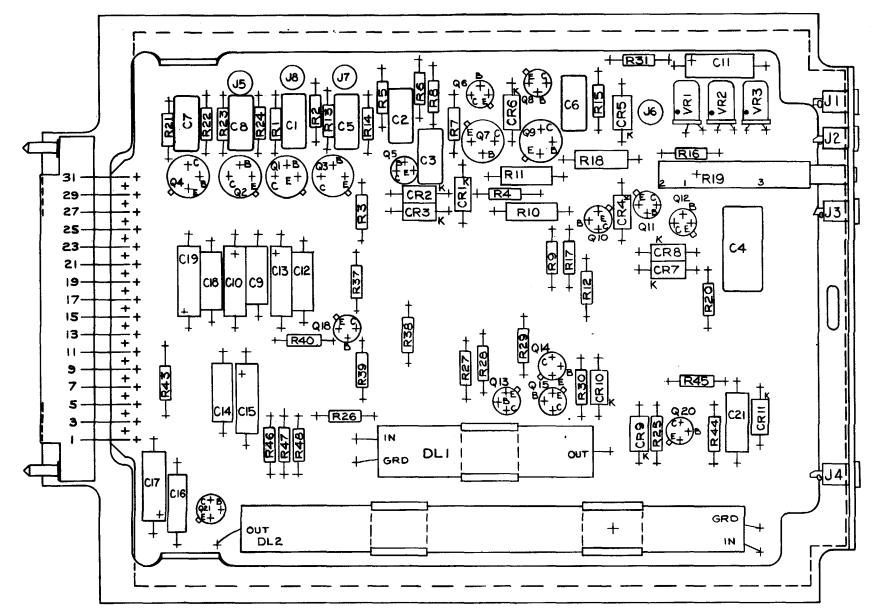

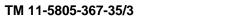

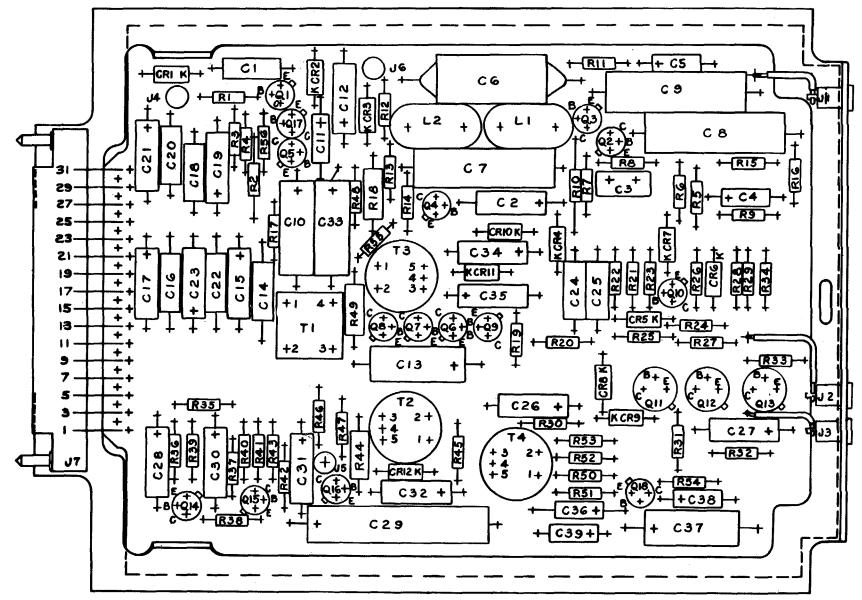

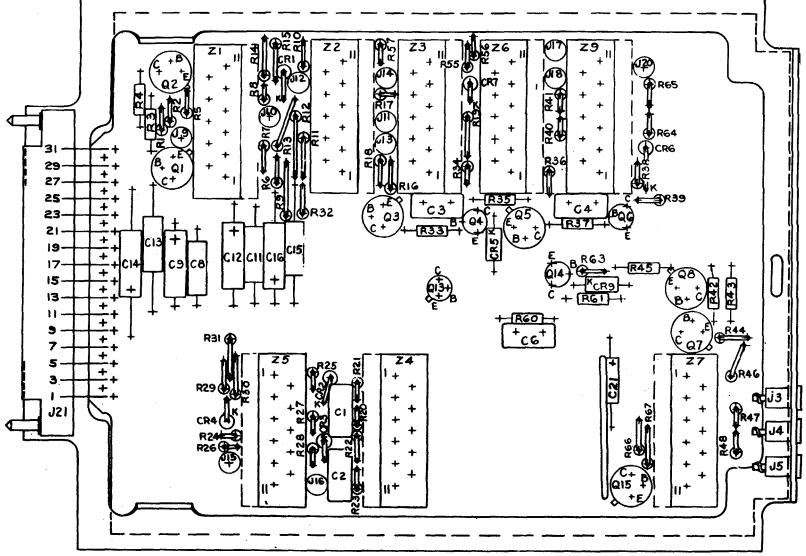

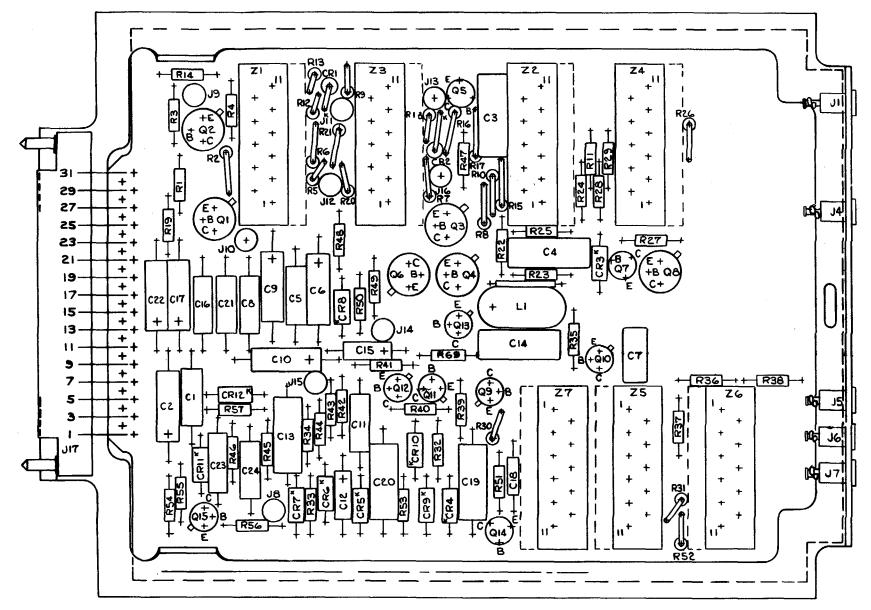

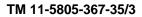

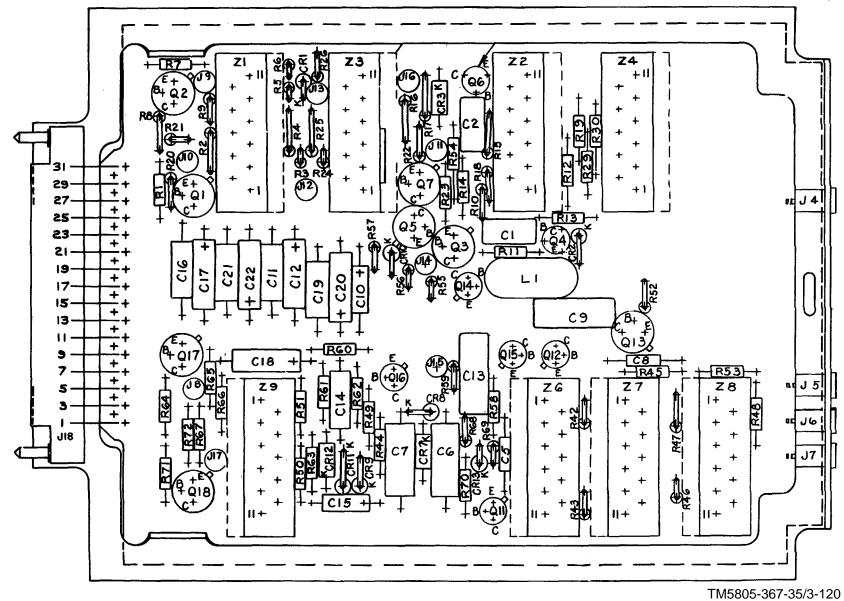

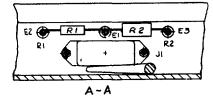

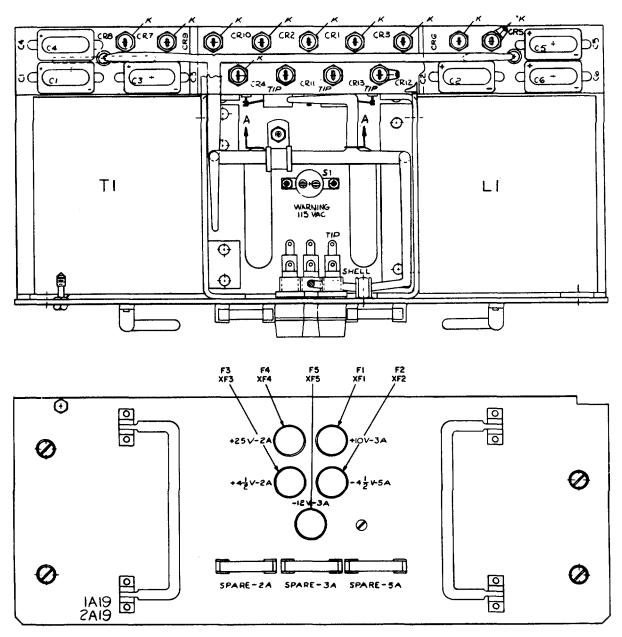

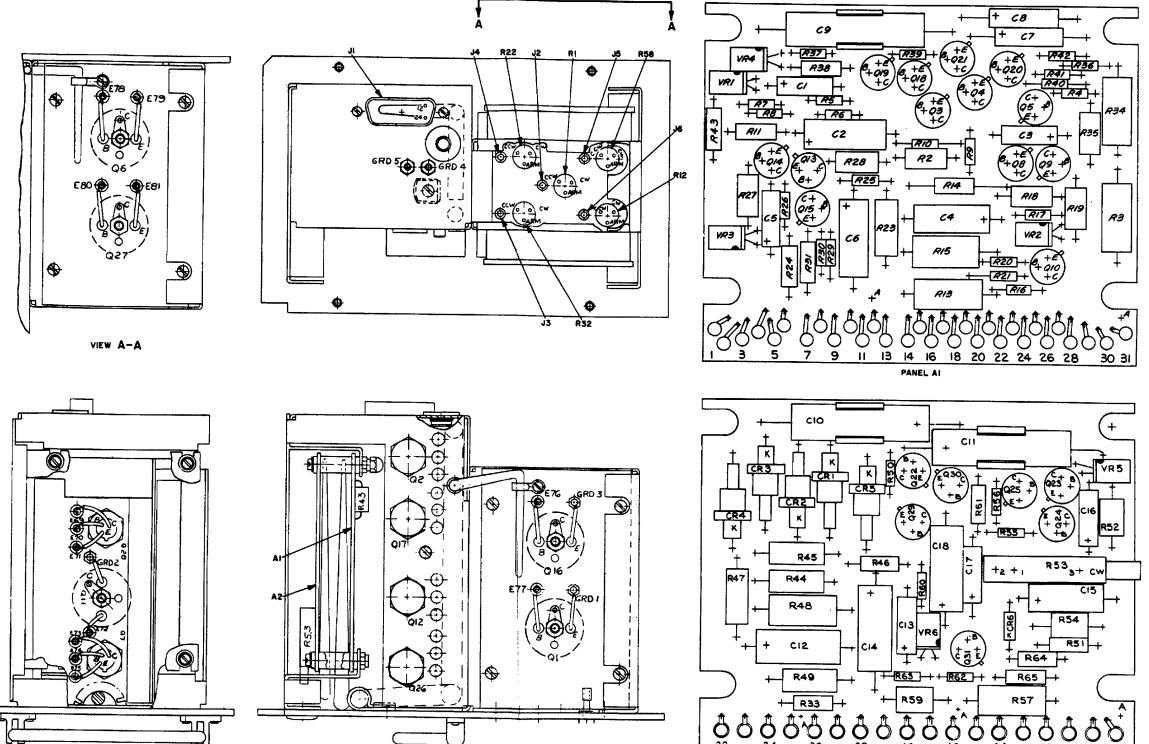

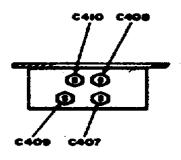

| 5-1     | Panel 1A2/2A2, top view                                                     |      |

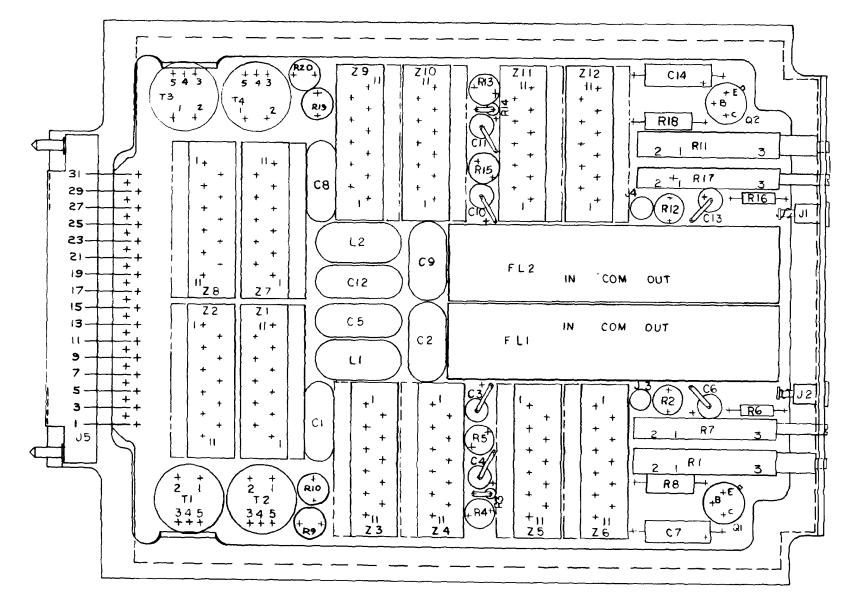

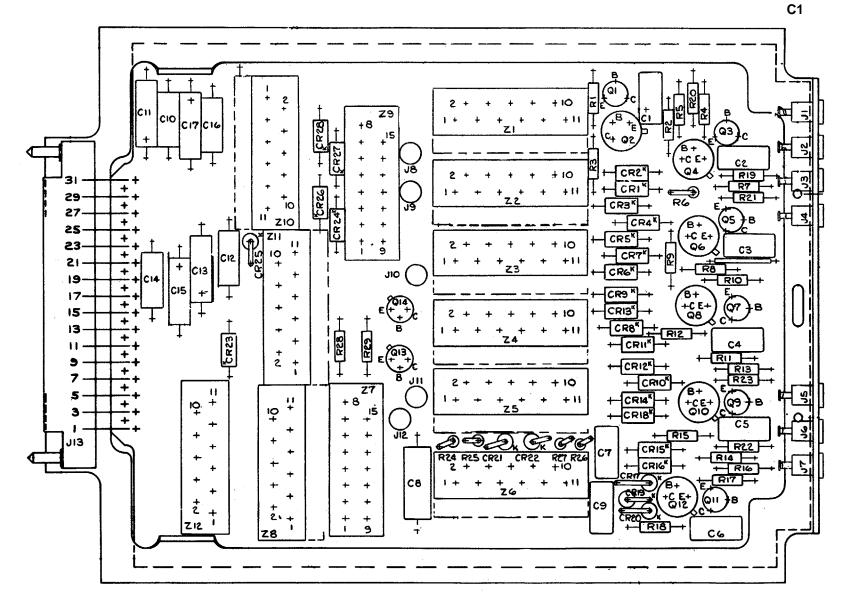

| 6-2     | Panel 1A8/2A2, top view                                                     |      |

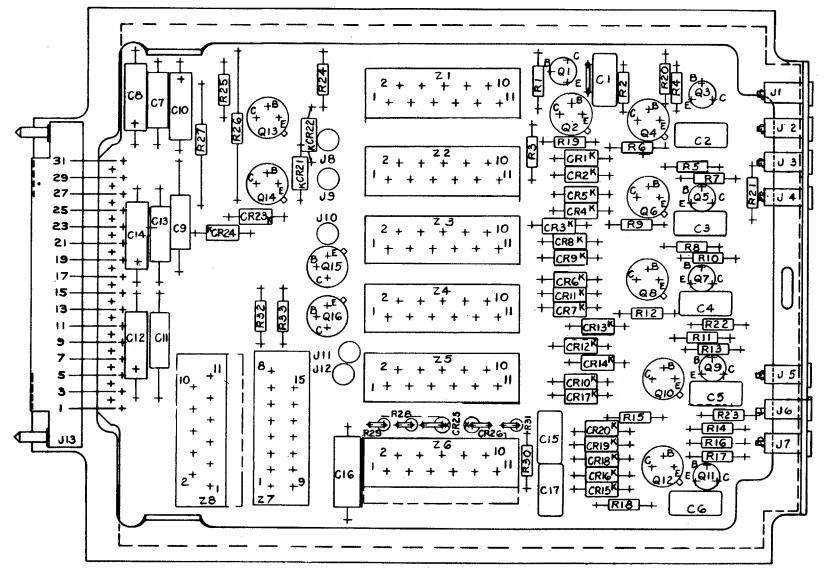

| 6-3     | Panel 1A6, top view                                                         |      |

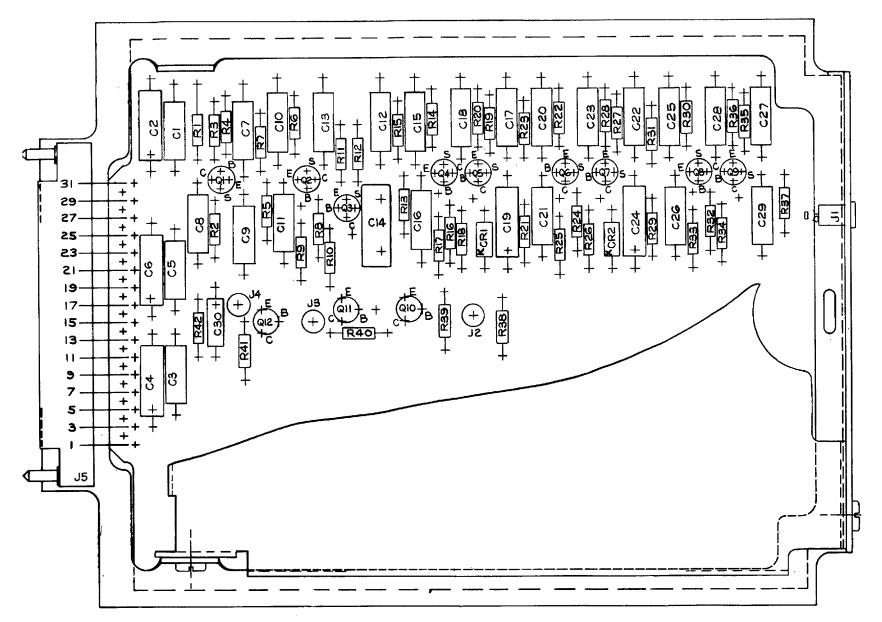

| 6-4     | Panel 2A6, top view.                                                        |      |

| 6-5     | Panel 1A6/2A6, top view                                                     |      |

| 6-6     | Panel 1A7, top view                                                         |      |

| 6-7     | Panel 2A7, top view                                                         |      |

| 6-8     | Panel 1-8, top view                                                         |      |

| 6-9     | Panel 2A8, top view                                                         |      |

| 6-10    | Panel 1A9, top view                                                         |      |

| 6-11    | Panel 2A9, top view                                                         |      |

| 6-12    | Panel 1A10, top view                                                        |      |

| 6-13    | Pa Panel 2A10, top view                                                     |      |

| 6-14    | Panel 1A11/2A11, top view                                                   |      |

| 6-16    | Panel 1A12/2412, top view                                                   |      |

| 6-16    | Panel 1A13, top view                                                        |      |

| 6-17    | Panel 2A13, top view                                                        |      |

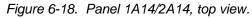

| 6-18.1  | Panel 1A14A/2A14A, top view                                                 |      |

| 6-18    | Panel 1-14/2A14, top view                                                   |      |

| 6-19    | Panel 1A16, top view                                                        |      |

| 6-20    | Panel 2A16, top view                                                        |      |

| 6-21    | Panel 1A16/2A16, top view.                                                  |      |

| 6-22    | Panel 1A17, top view                                                        |      |

| ·       | Change 2 iv                                                                 |      |

Change 3 iv

#### LIST OF ILLUSTRATIONS-Continued

| Fig.#         | Title                                                                 | Page    |

|---------------|-----------------------------------------------------------------------|---------|

| 6-23          | Panel 2A17, top view                                                  | 6-24    |

| 6-24          | Panel 1A18, top view                                                  |         |

| 6-25          | Panel 2A18, top view                                                  | 6-26    |

| 6-26          | Panel 1A29/2A19, top view                                             | 6-27    |

| 6-26.1        | Panel 1A20/2A20, top view                                             | 6-28    |

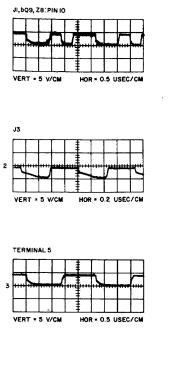

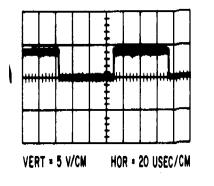

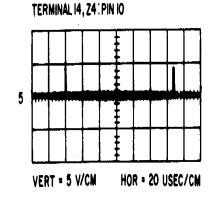

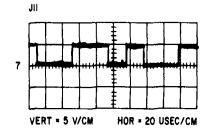

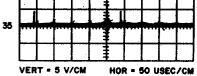

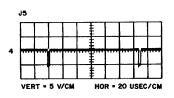

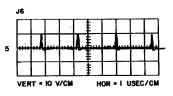

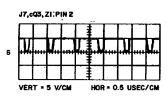

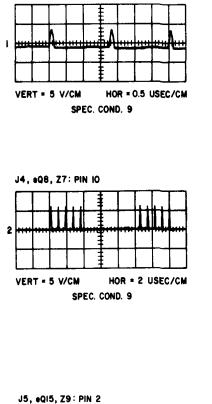

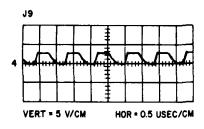

| 6-27          | Panel 1A7, troubleshooting - waveforms                                | 6-29    |

| 6-28          | Panel 1A8, troubleshooting waveforms                                  | Foldout |

| 6-29          | Panel 1A22/2A11, troubleshooting waveforms                            | 6-30    |

| 6-30          | Panel 1A16/2A16, troubleshooting waveforms                            | 6-31    |

| 6-31          | Deleted                                                               |         |

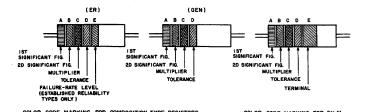

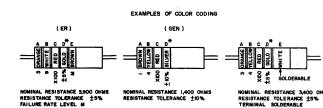

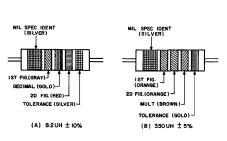

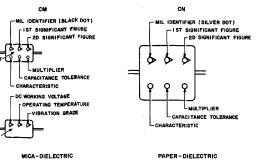

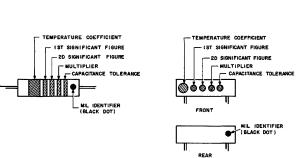

| 6-32          | Color coding markings for MIL STD resistors, inductors and capacitors |         |

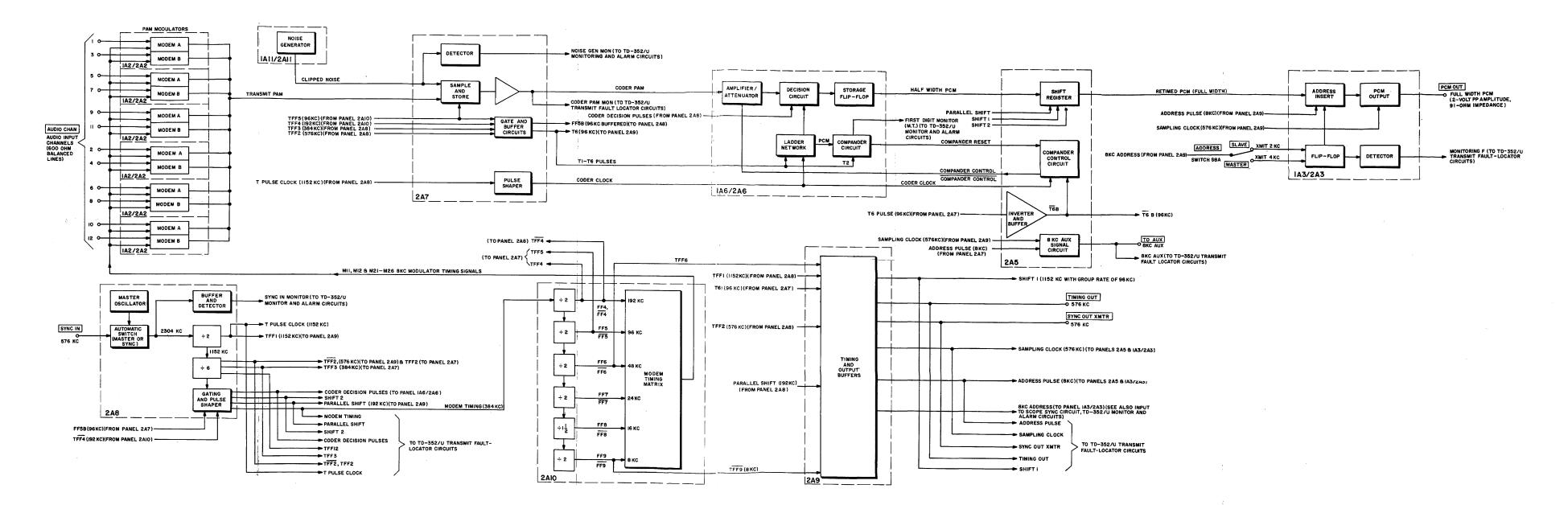

| 6-33          | Multiplexer TD-352/U transmit circuits, block diagram                 |         |

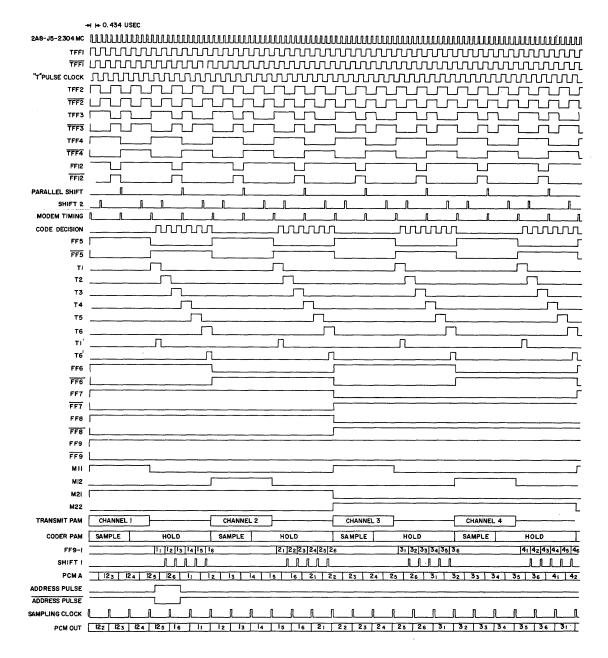

| 6-34          | Multiplexer TD-352/U transmit timing, idealized waveforms             |         |

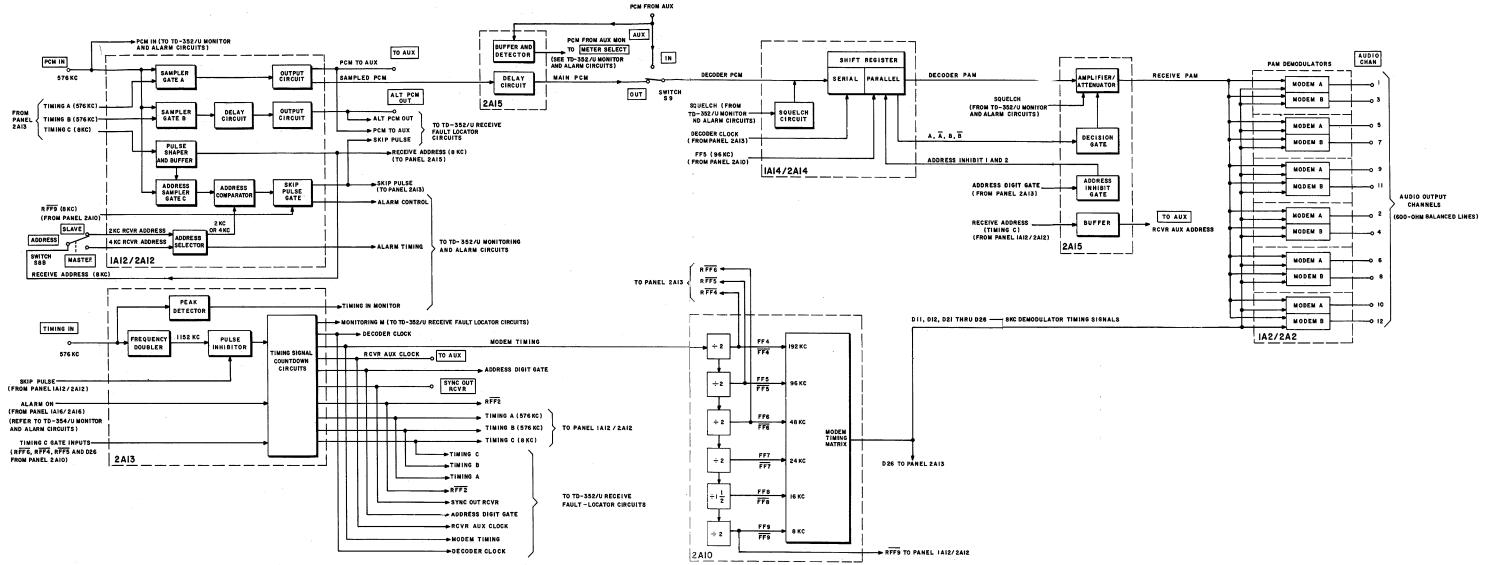

| 6-35          | Multiplexer TD-352/U receive circuits, block diagram                  |         |

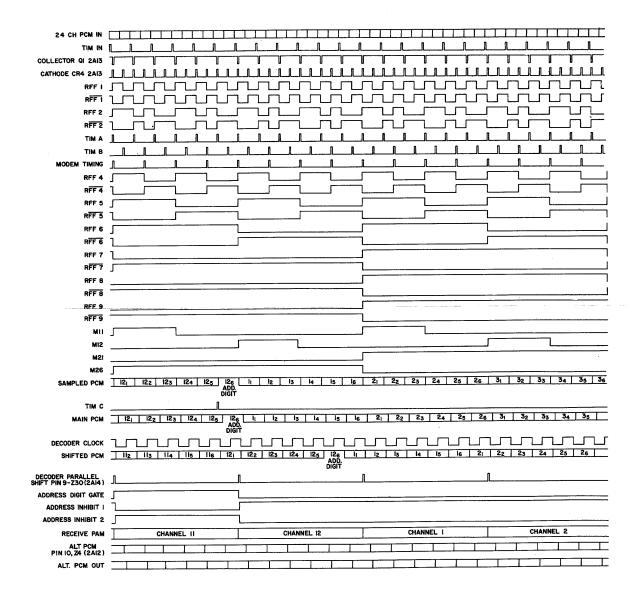

| 6-36          | Multiplexer TD-352/U receive timing, idealized waveforms              |         |

| 6-37          | Multiplexer TD-352/U monitor and alarm circuits, block diagrams       |         |

| 6-38          | Multiplexer TD-353/U transmit circuits, block diagram                 |         |

| 6-39          | Multiplexer TD-353/U transmit timing, idealized waveforms             |         |

| 6-40          | Multiplexer TD-353/U receive circuits, block diagram                  |         |

| 6-41          | Multiplexer TD-353/U receive timing, idealized wavef orms             |         |

| 6-42          | Multiplexer TD-353/U monitor and alarm circuits, block diagram        |         |

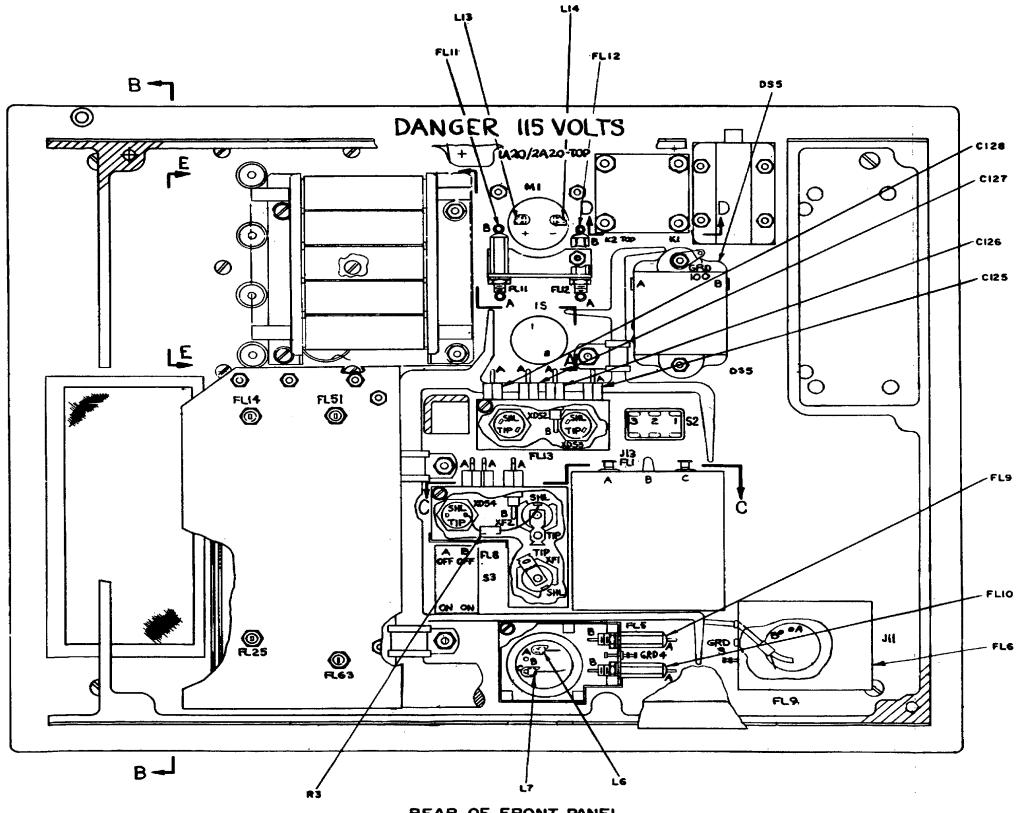

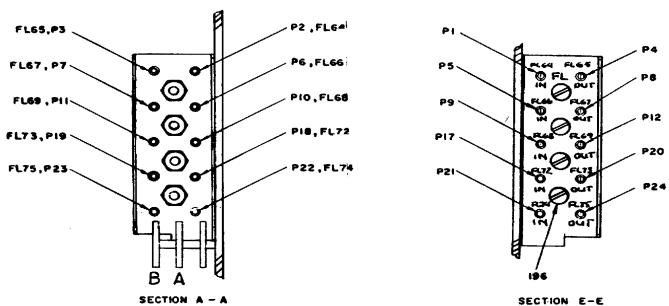

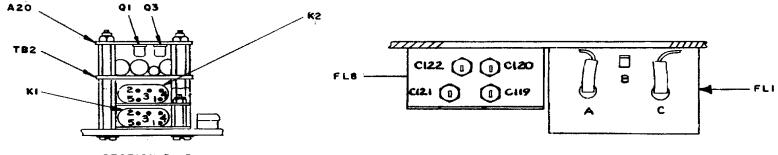

| 6-43          | Panel 1A1/2A11 top view                                               |         |

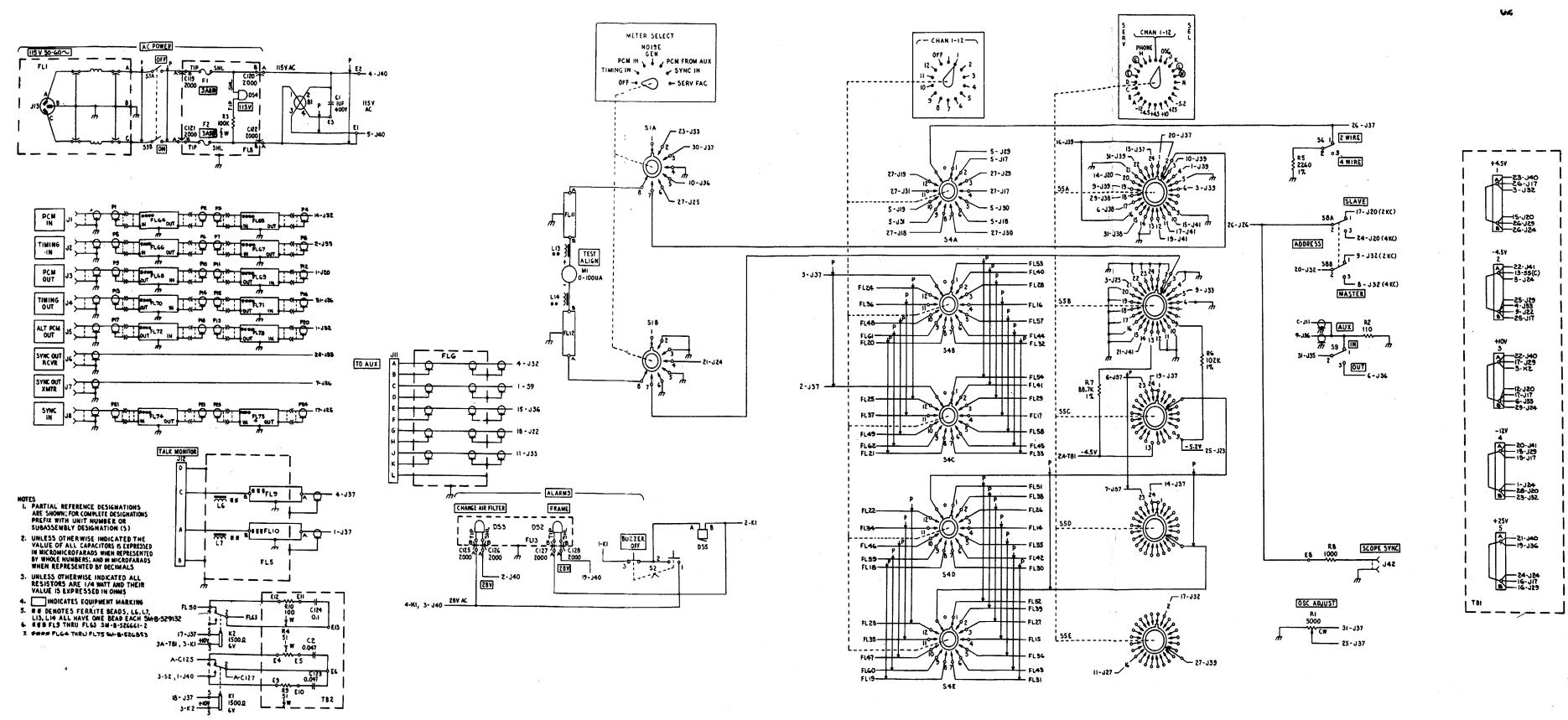

| 6-44          | Panel 1A1/2A1, schematic diagram                                      |         |

| 6-45          | Panel 1A2A/2A2A, schematic diagram                                    |         |

| 6-45.1        | Panel 1A2/2A2A, schematic diagram                                     |         |

| 6-46          | Panel 1A2/2A2 or 1A2/2A2A, troubleshooting waveforms                  |         |

| 6-47          | Panel 1A3/2A3, schematic diagram                                      |         |

| 6-48          | Panel 1A3/2A3, troubleshooting waveforms                              |         |

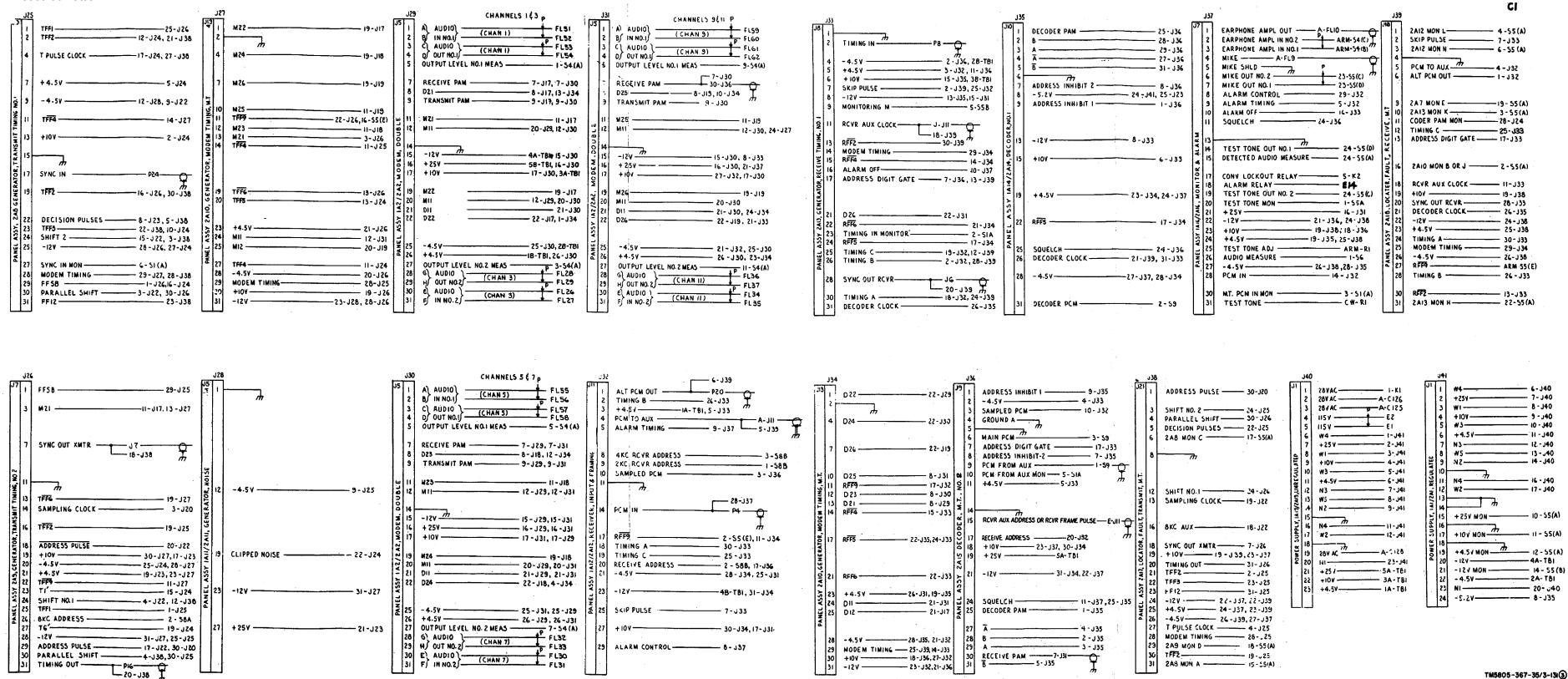

| 6-49          | Panel 1A5, schematic diagram                                          |         |

| 6-50          | Panel 1A5, troubleshooting waveforms                                  |         |

| 6-51          | Panel 2A5 schematic diagram                                           |         |

| 6-52          | Panel 2A5 troubleshooting waveforms                                   |         |

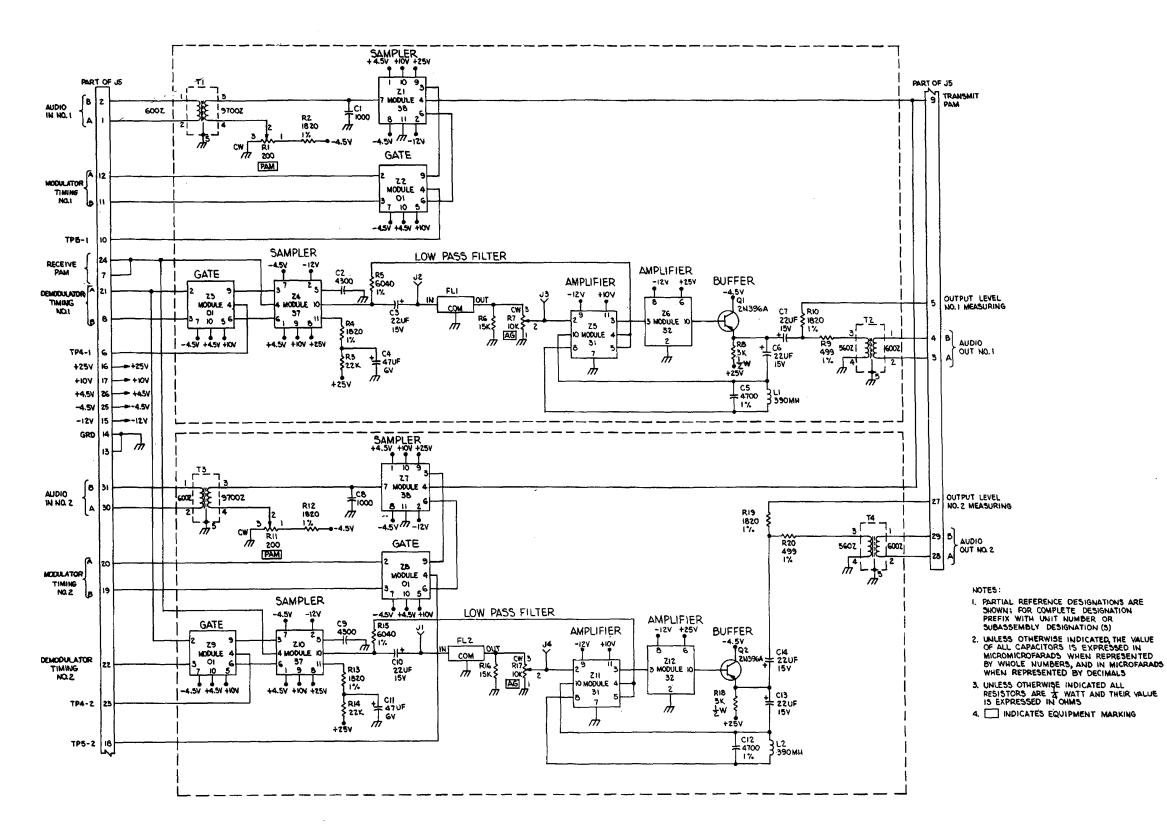

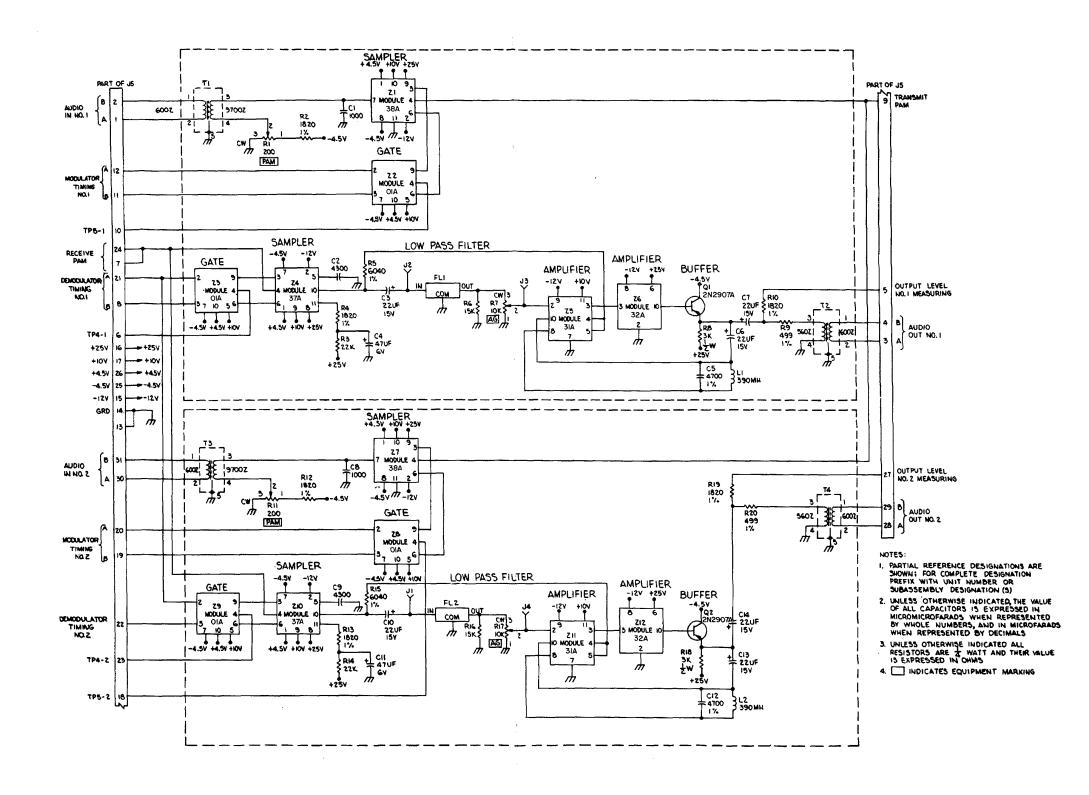

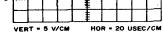

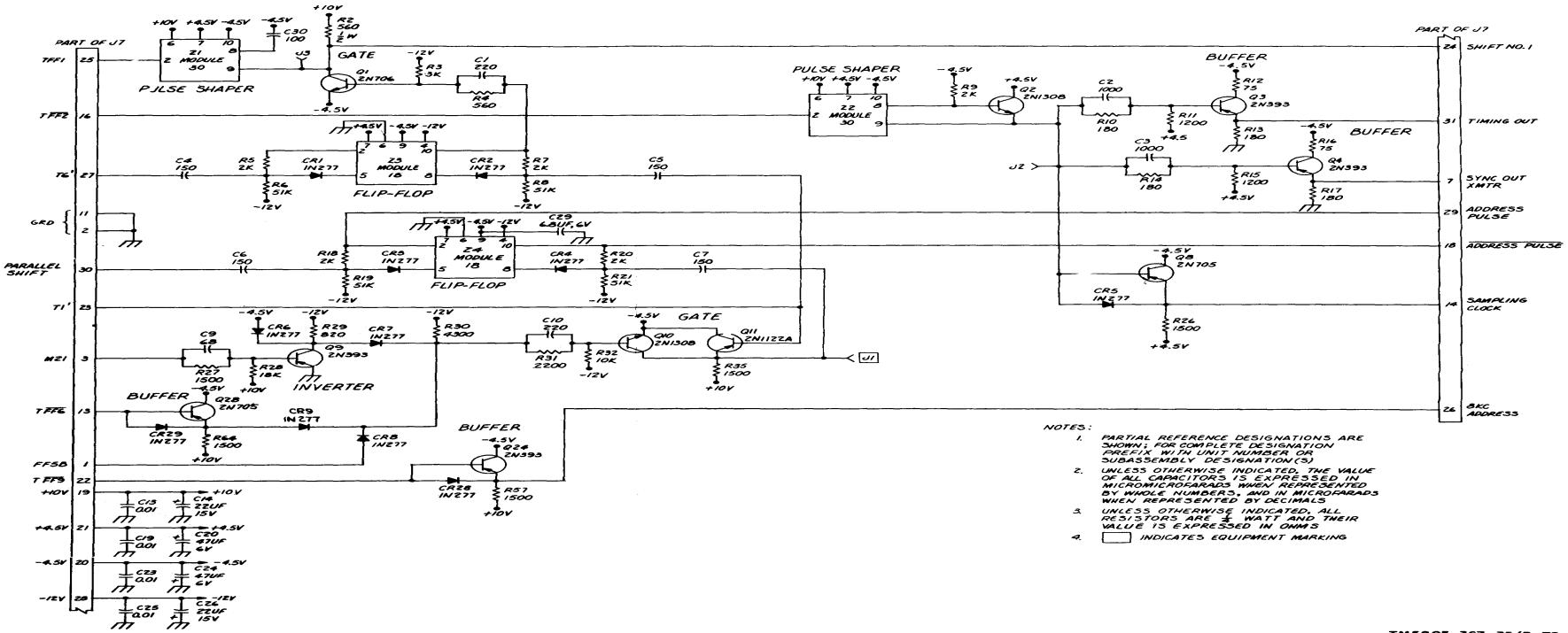

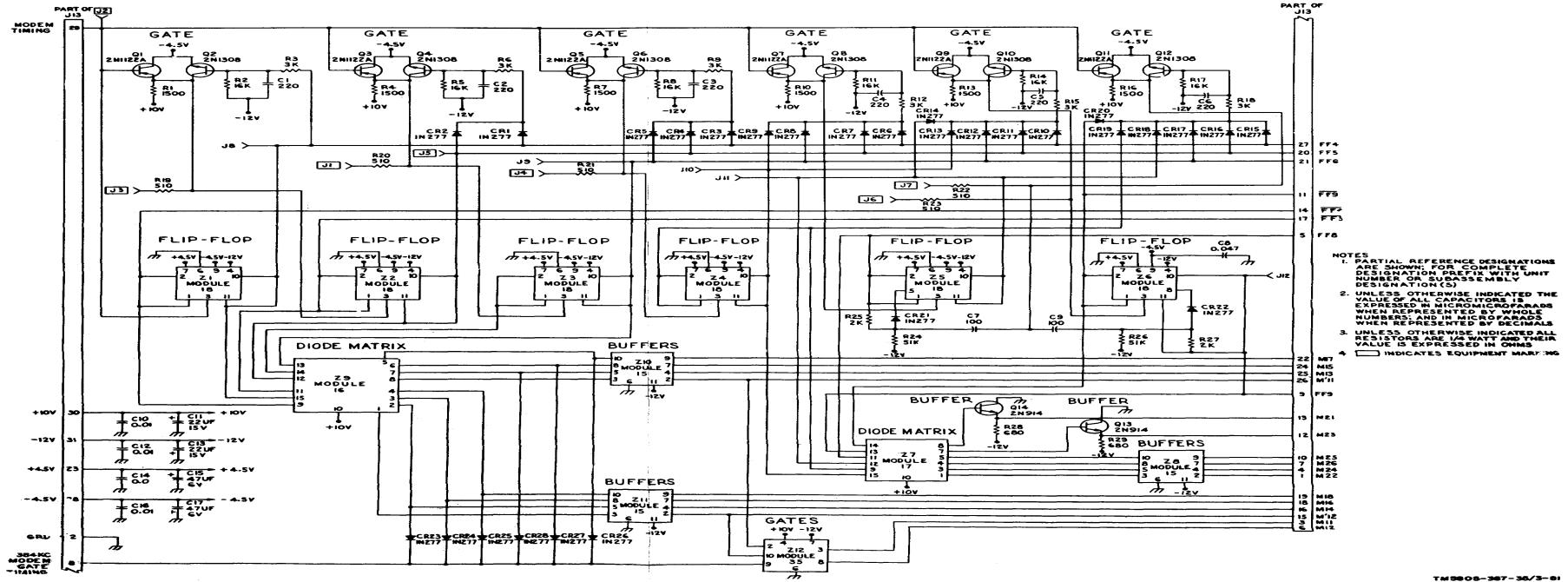

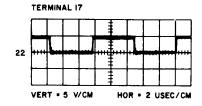

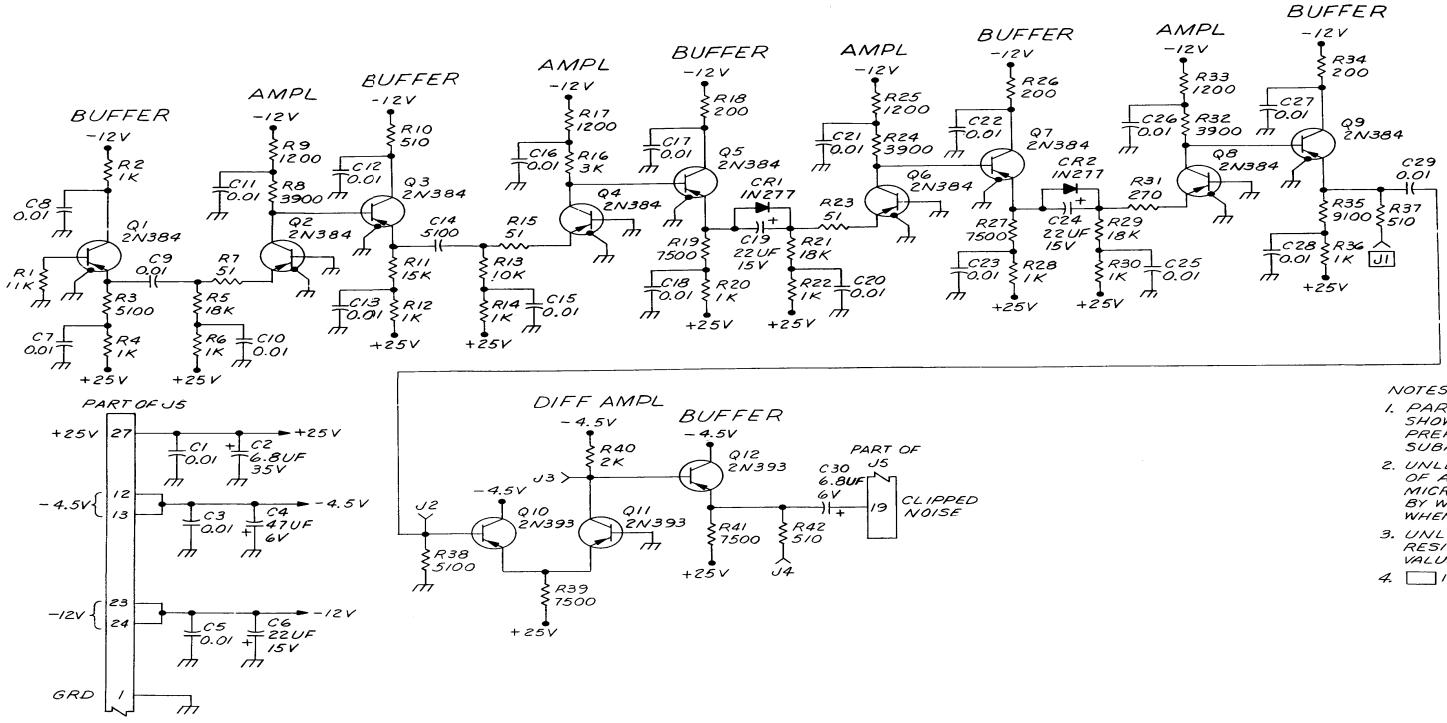

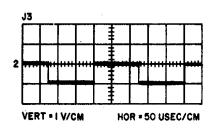

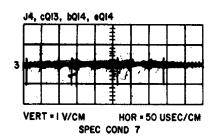

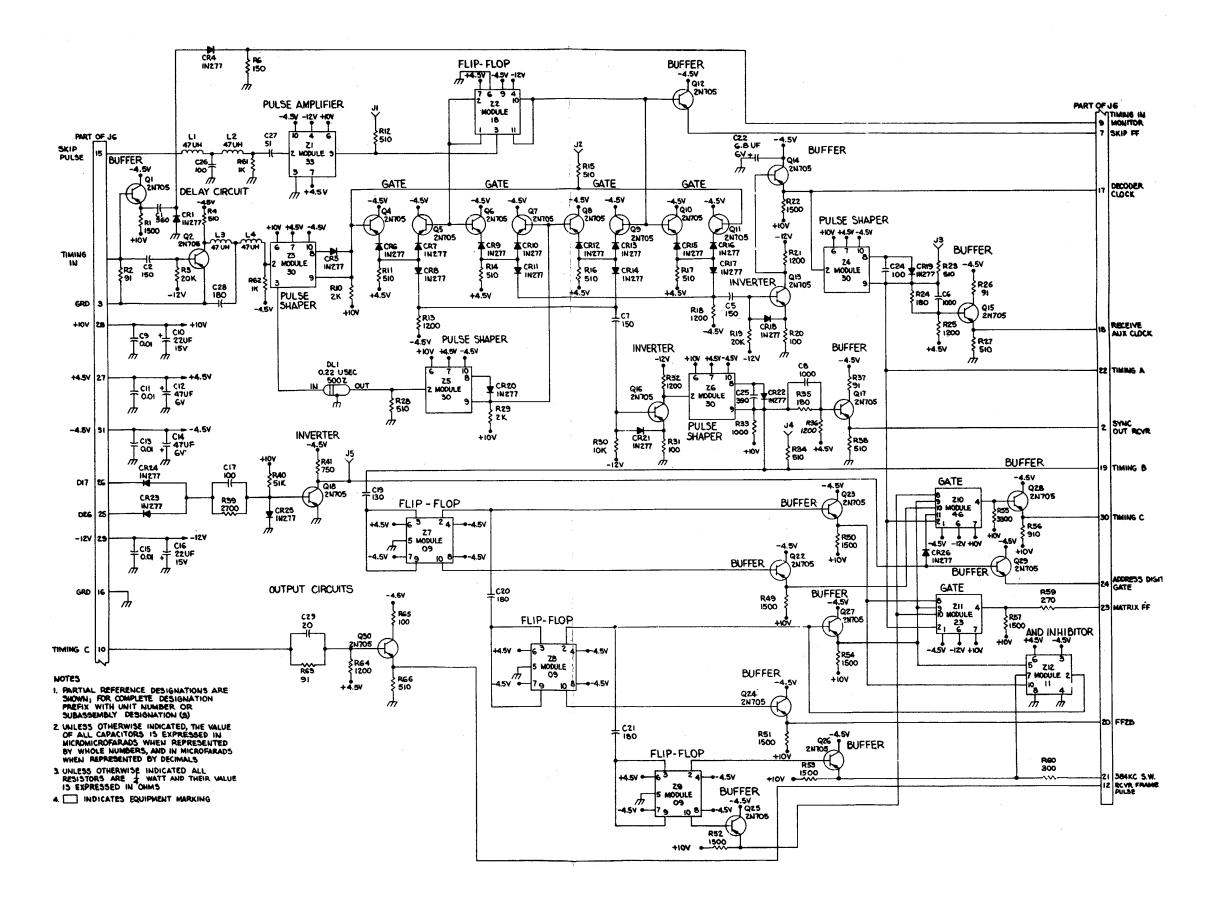

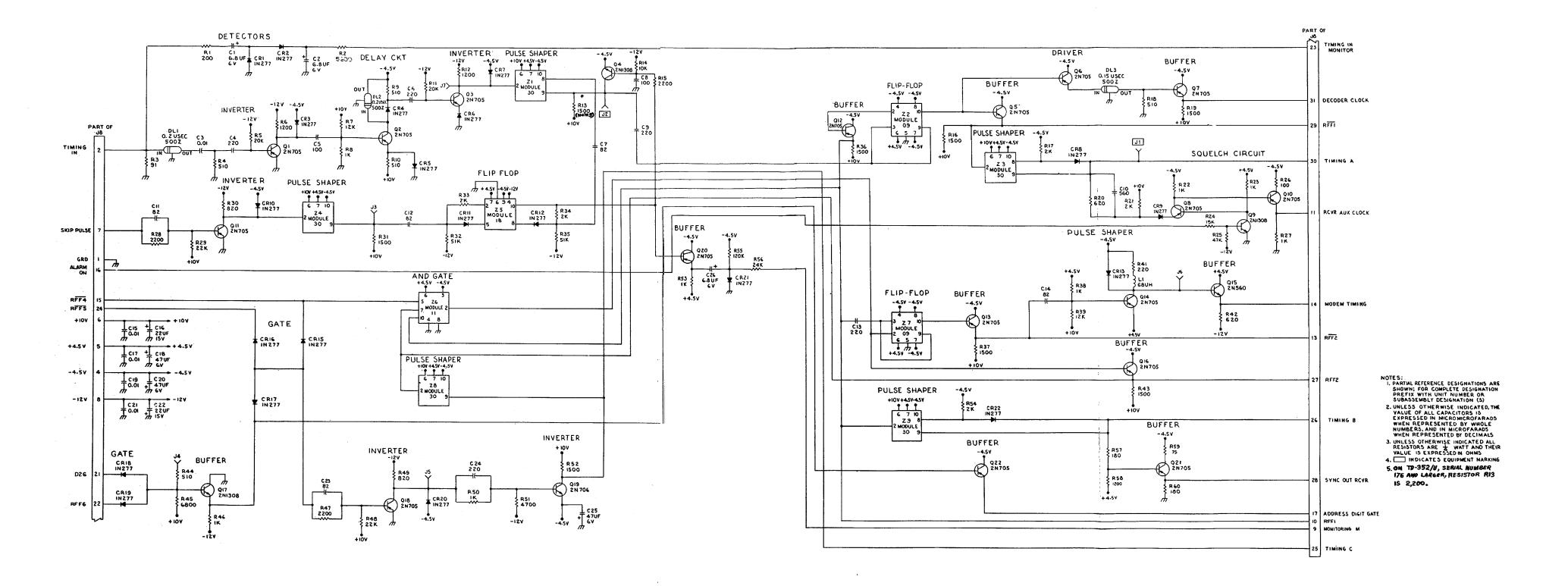

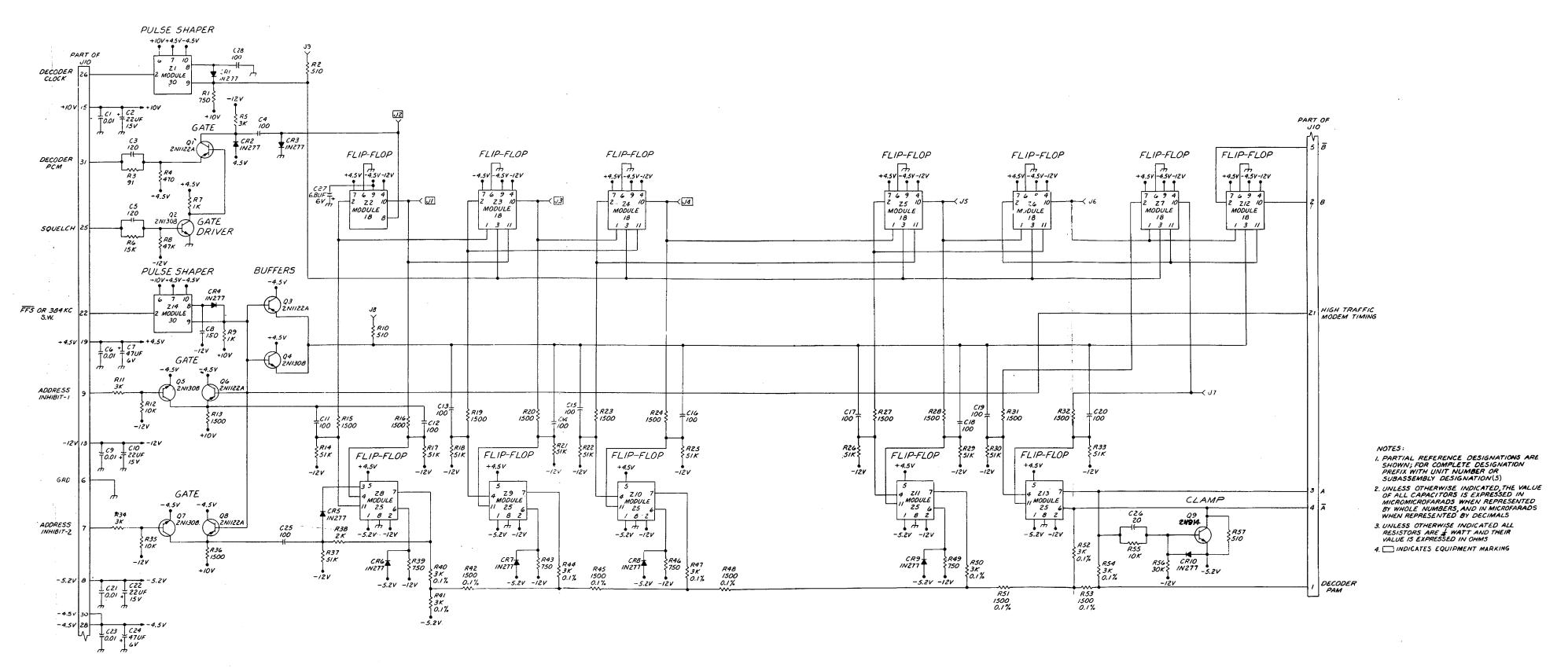

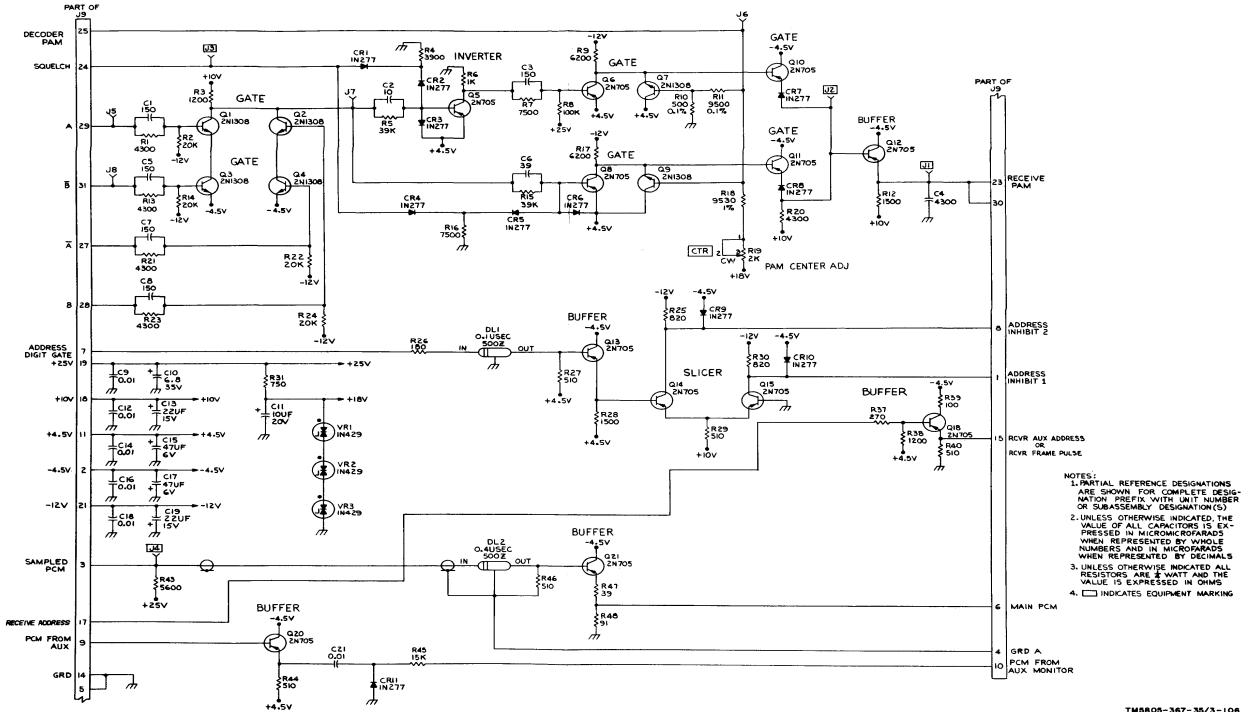

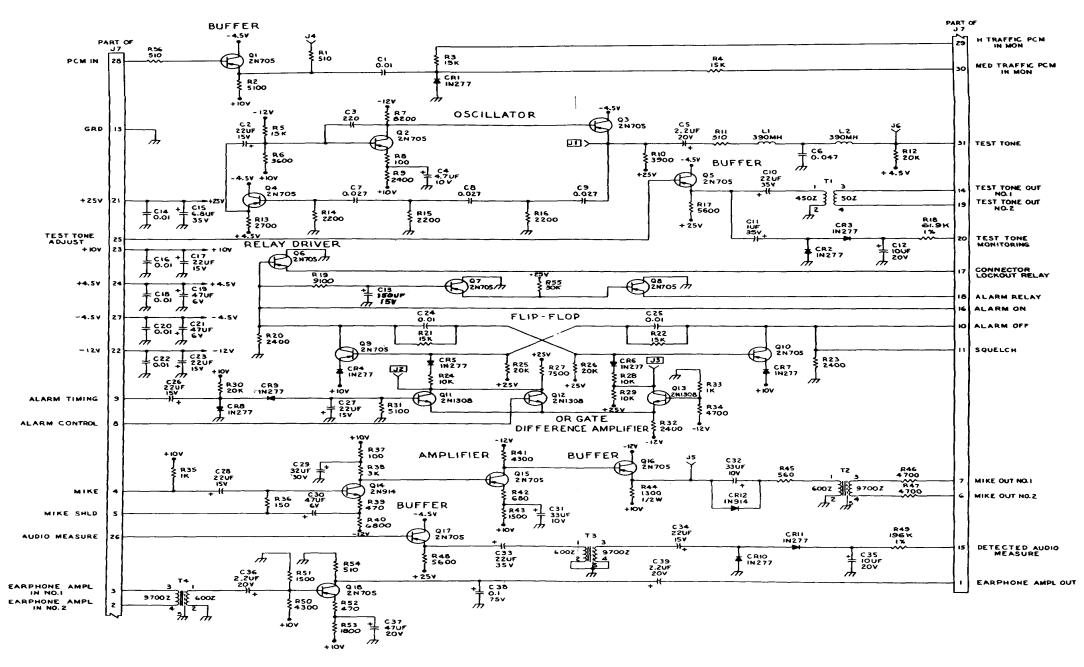

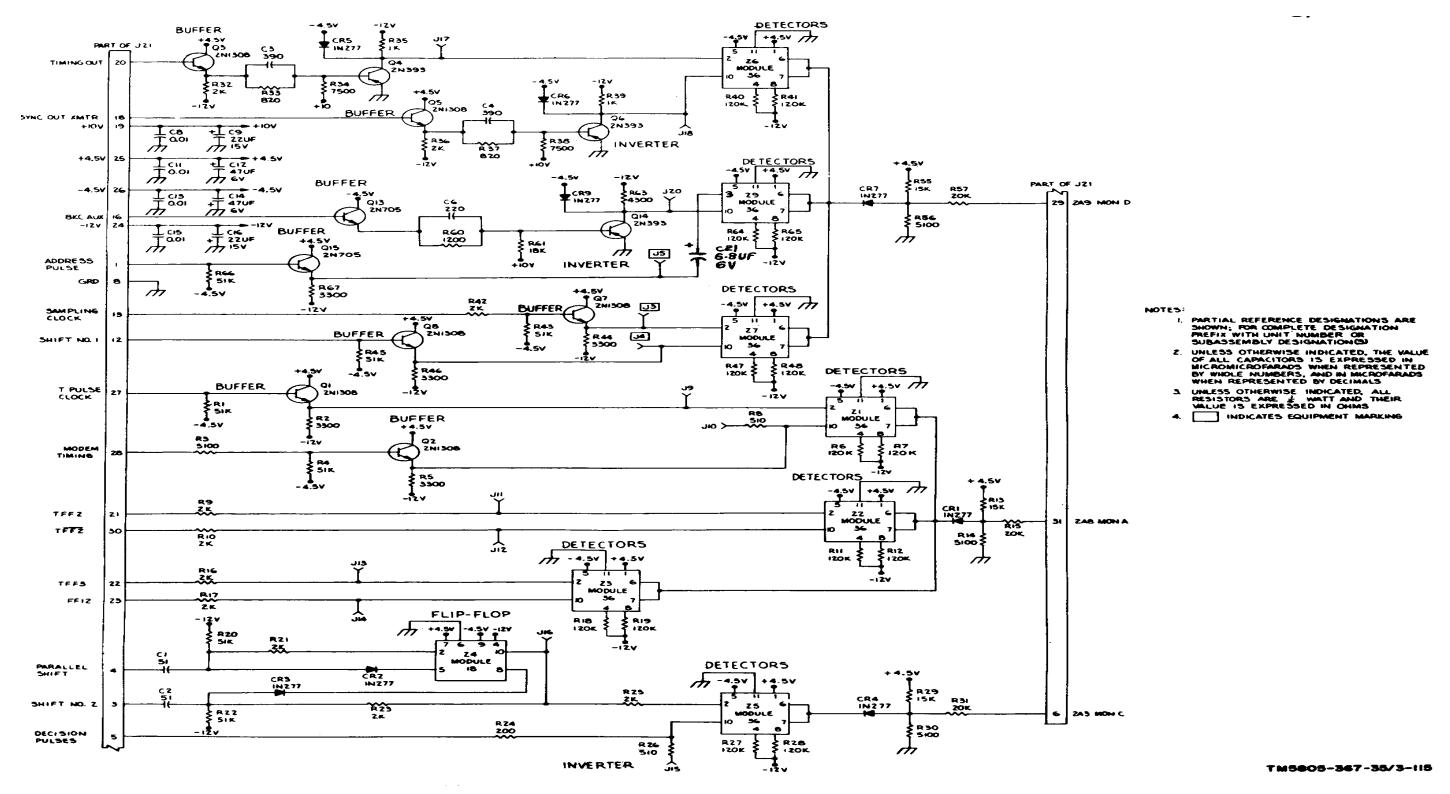

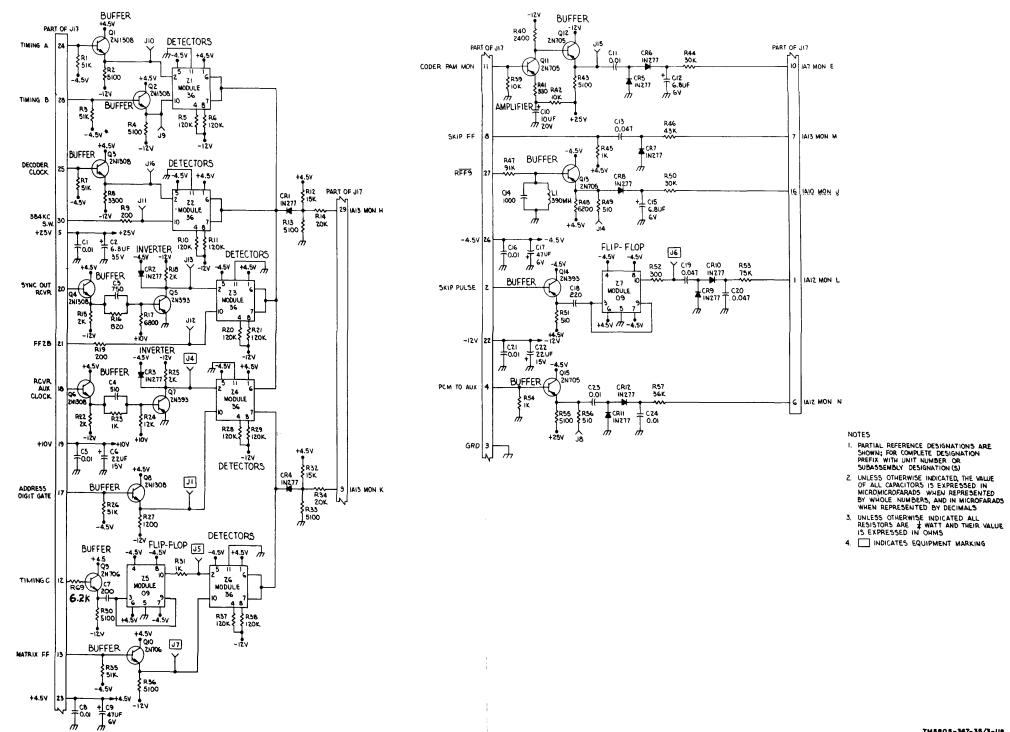

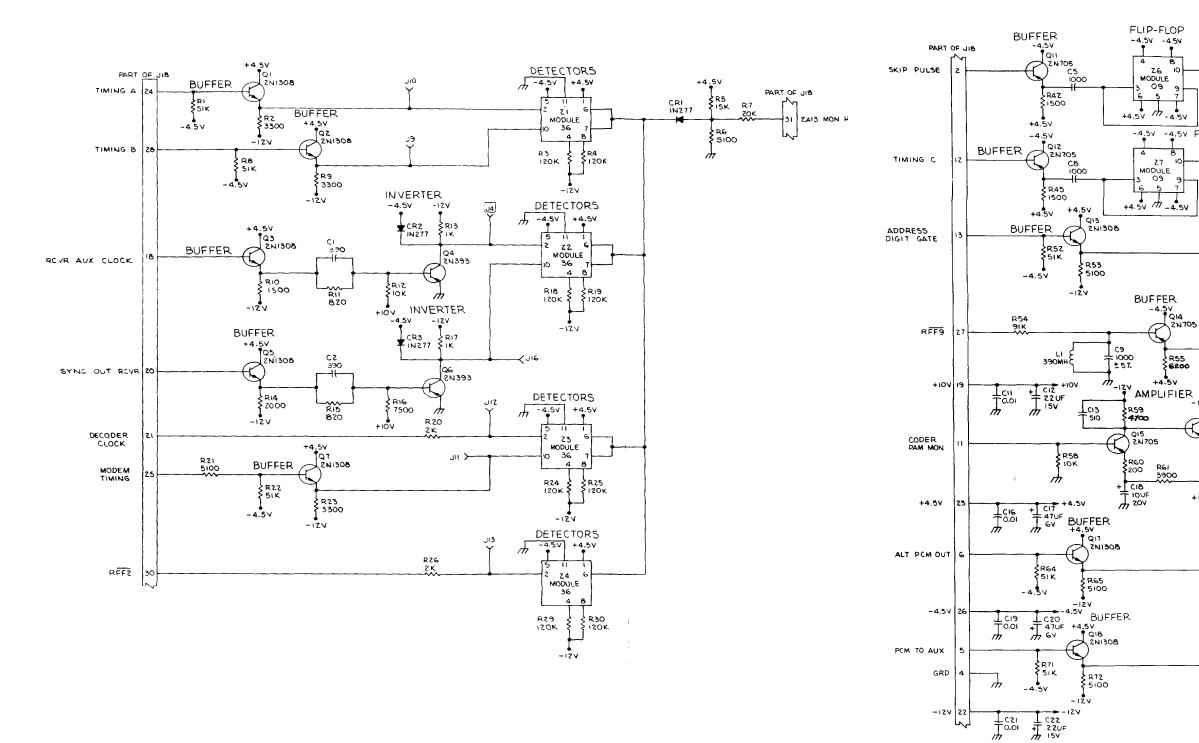

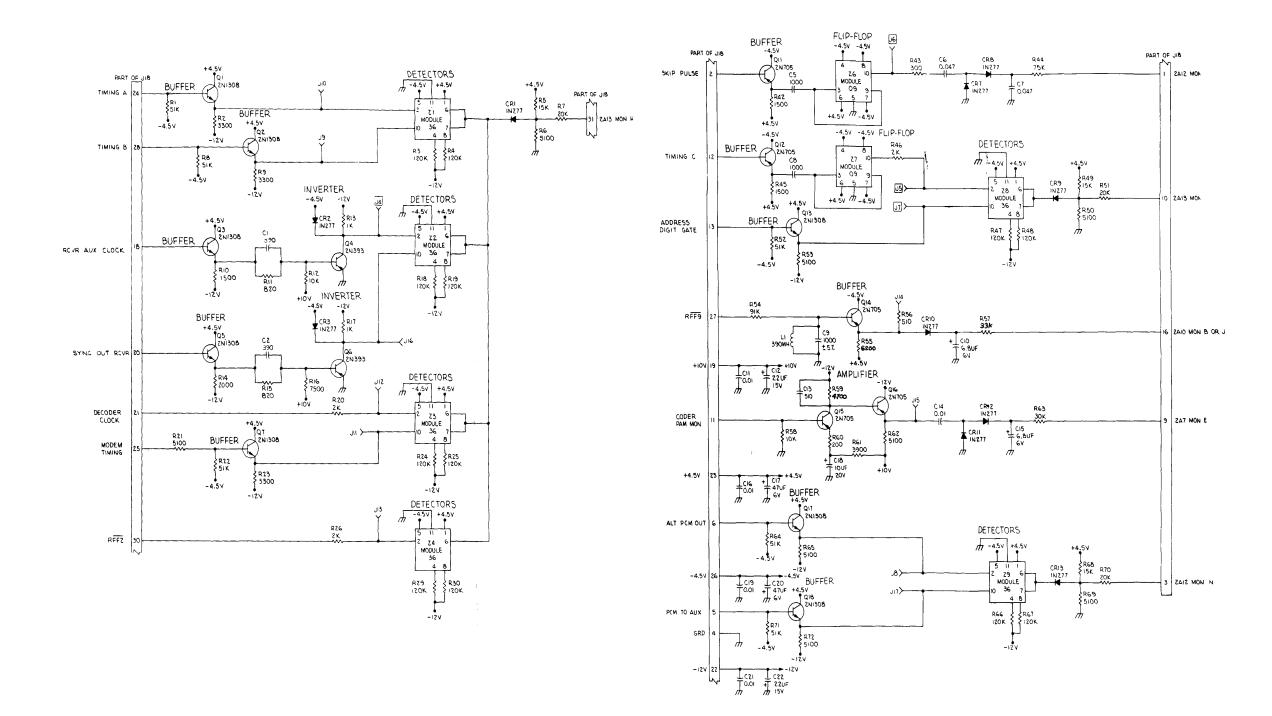

| 6-53          | Panel 1A6/2A6, schematic diagram                                      |         |

| 6-53.1        | Panel 1A6A/2A6A, schematic diagram                                    |         |

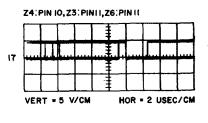

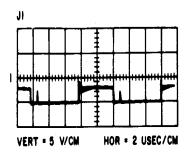

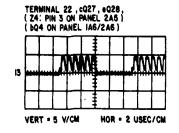

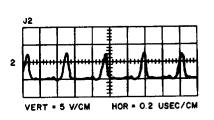

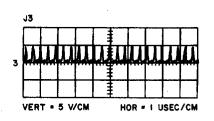

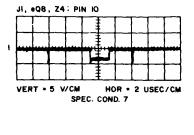

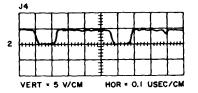

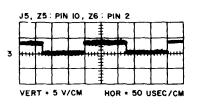

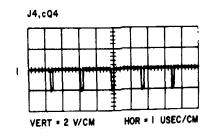

| 6-54①         | Panel 1A6/2A6, troubleshooting waveforms (part 1 of 3)                |         |

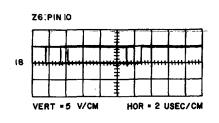

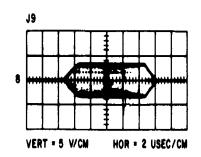

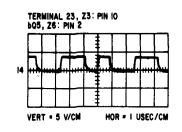

| 6-54©         | Panel 1A6/2A6, troubleshooting waveforms (part 2 of 3)                |         |

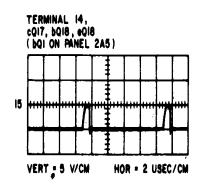

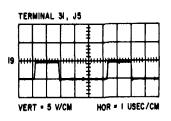

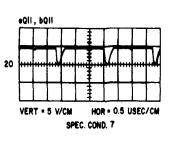

| 6-543<br>6 55 | Panel 1A6/2A6, troubleshooting waveforms (part 3 of 3)                |         |

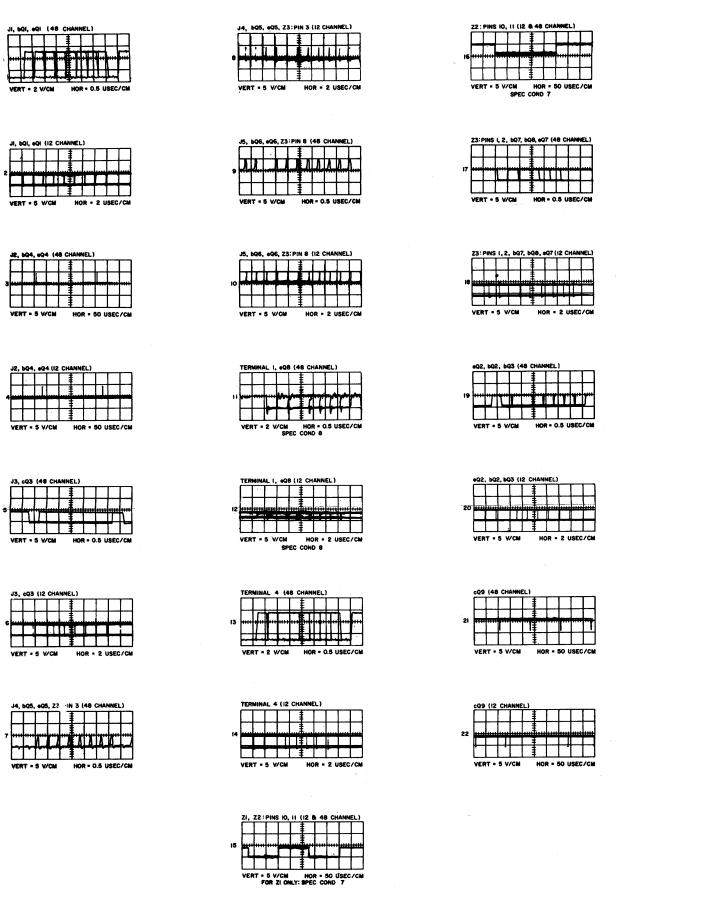

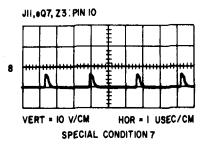

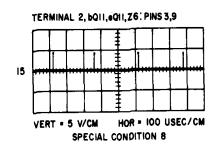

| 6-55<br>6 5 6 | Panel 1A7, schematic diagram                                          |         |

| 6-56<br>6-57  | Panel 2A7, schematic diagram                                          |         |

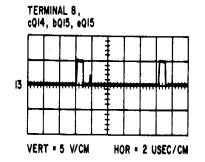

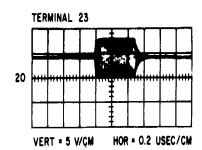

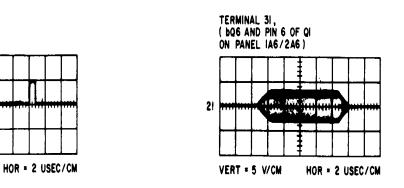

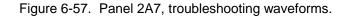

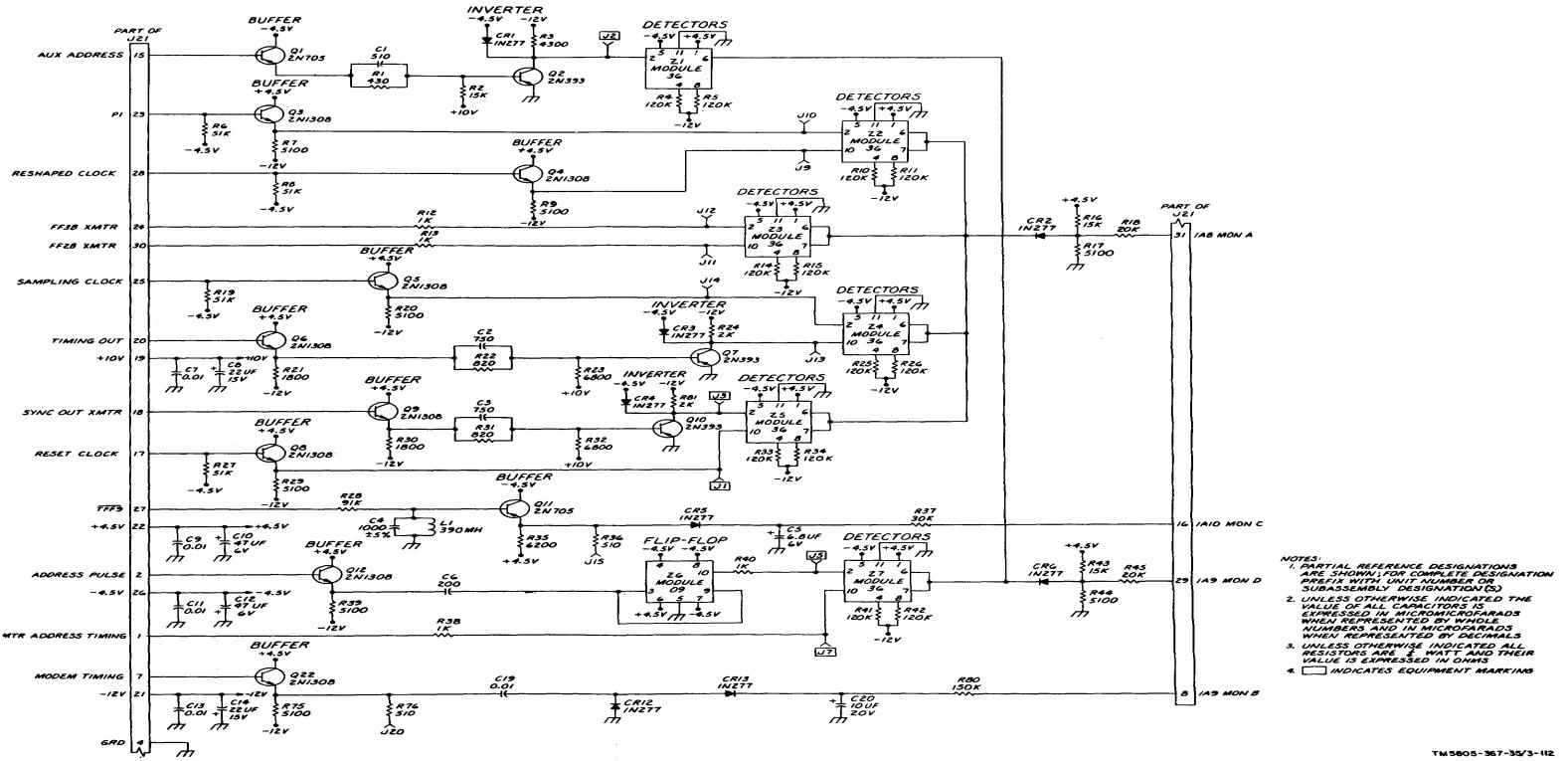

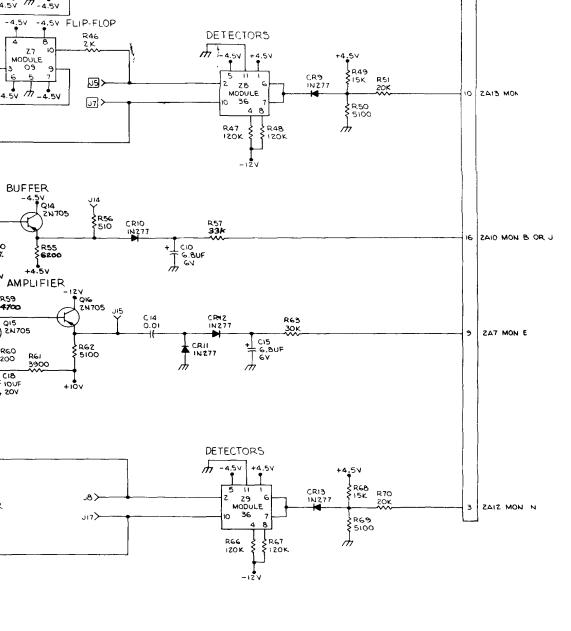

| 6-58          | Panel 2A7, troubleshooting waveforms                                  |         |

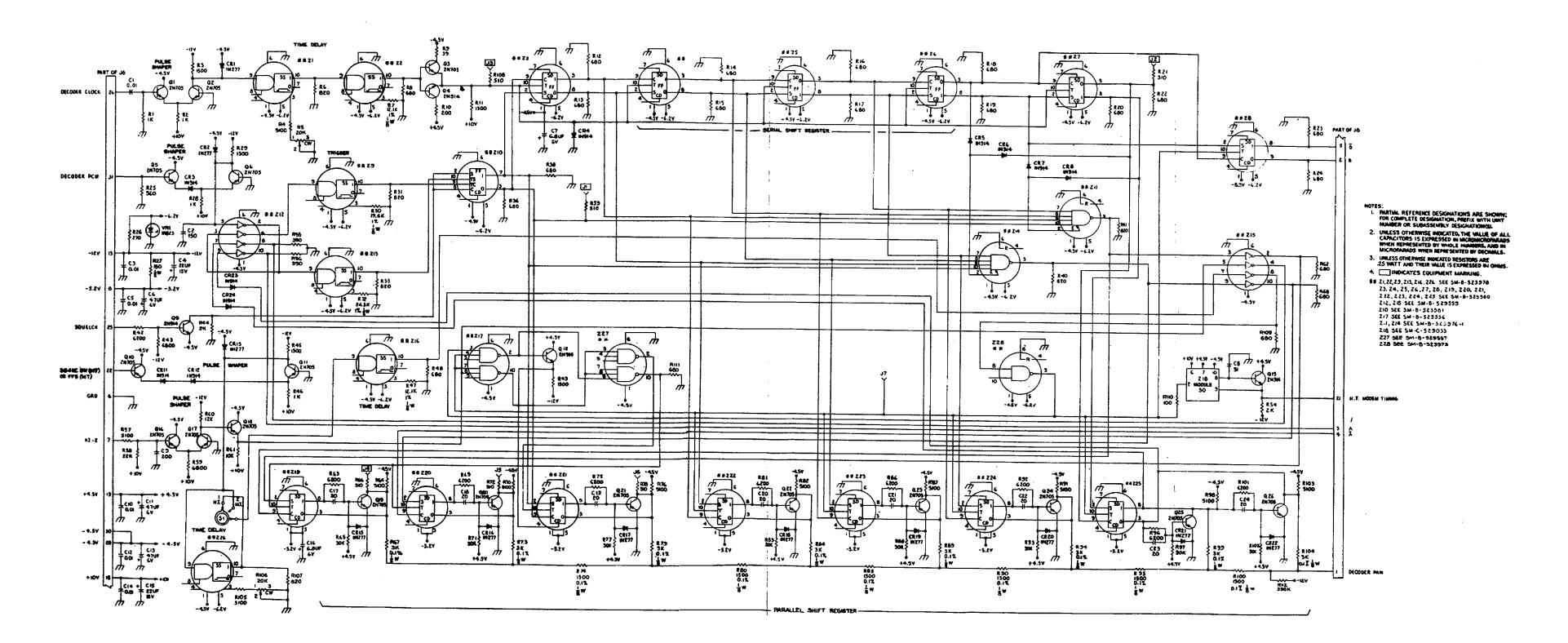

| 6-59          | Panel 1A8, schematic diagram<br>Panel 2A8 schematic diagram           |         |

| 6-60          | Panel 2A8 troubleshooting waveforms                                   |         |

| 6-61          | Panel 1A9, schematic diagram                                          |         |

| 6-62          | Panel 1A9, troubleshooting waveforms                                  |         |

| 6-63          | Panel 2A9, schematic diagram                                          |         |

| 6-64          | Panel 2A9, troubleshooting waveforms                                  |         |

| 6-65          | Panel 1A10 schematic diagram                                          |         |

| 6-66          | Panel 1A10 troubleshooting waveforms                                  |         |

| 6-67          | Panel 2A10, schematic diagram                                         |         |

| 6-68          | Panel 2A10, troubleshooting waveforms                                 |         |

| 6-69          | Panel 1A11/2A11, schematic diagram                                    |         |

|               |                                                                       |         |

# LIST OF ILLUSTRATIONS-Continued

|               | LIST OF ILLUSTRATIONS-Continued                            |         |

|---------------|------------------------------------------------------------|---------|

| Fig.#         | Title                                                      | Page    |

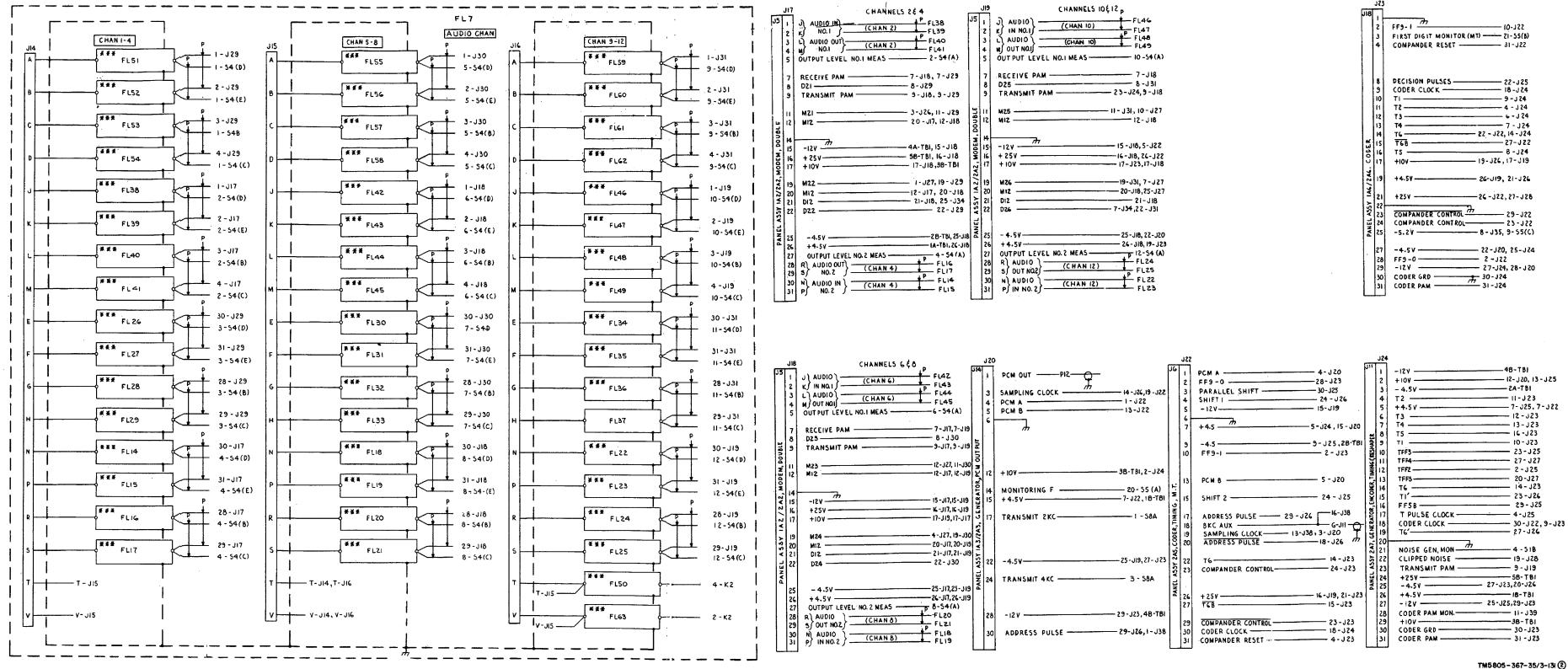

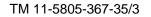

| 6-70          | Panel 1A12/2A12, schematic diagram                         | Foldout |

| 6-70.1        | Panel 1A121, schematic diagram                             |         |

| 6-71①         | Panel 1A12/2A12, troubleshooting waveforms (part 1 of 2)   |         |

| 6-712         | Panel 1A12/2A12, troubleshooting waveforms (part 2 of 2)   |         |

| 6-72          | Panel 1A13, schematic diagram                              |         |

| 6-73          | Panel 1A13, troubleshooting waveforms                      |         |

| 6-74          | Panel 2A13, schematic diagram                              |         |

| 6-75          | Panel 2A13, troubleshooting waveforms                      |         |

| 6-76          | Panel 1A14/2A14, schematic diagram                         |         |

| <b>6-77</b> ① | Panel 1A14/2A14, troubleshooting waveforms (part 1 of 2)   |         |

| <b>6-77</b> ② | Panel 1A14/2A14, troubleshooting waveforms (part 2 of 2)   |         |

| 6-77.1①       | Panel 1A14A/2A14A, schematic diagram.                      |         |

| 6-77.22       | Panel 1A14A/2A14A, troubleshooting waveforms (part 1 of 3) | Foldout |

| 6-77.2        | Panel 1A14A/2A14A, troubleshooting waveforms (part 2 of 3) |         |

| 6-77.2        | Panel 1A14A/2A14A, troubleshooting waveforms (part 3 of 3) |         |

| 6-78          | Panel 1A15, schematic diagram                              |         |

| 6-79          | Panel 1A15, troubleshooting waveforms                      |         |

| 6-80          | Panel 2A15, schematic diagram                              |         |

| 6-81          | Panel 2A15, troubleshooting waveforms                      |         |

| 6-82          | Panel 1A16/2A16, schematic diagram                         |         |

| 6-83          | Panel 1A17, schematic diagram                              |         |

| 6-84          | Panel 1A17, troubleshooting waveforms                      |         |

| 6-85          | Panel 2A17, schematic diagram                              |         |

| 6-86          | Panel 2A17, troubleshooting waveforms                      |         |

| 6-87          | Panel 1A18, schematic diagram                              |         |

| 6-88          | Panel 1A18, troubleshooting waveforms                      |         |

| 6-89          | Panel 2A18, schematic diagram                              |         |

| 6-90          | Panel 2A18, troubleshooting waveforms                      |         |

| 6-91          | Panel 1A19/2A19, schematic diagram                         |         |

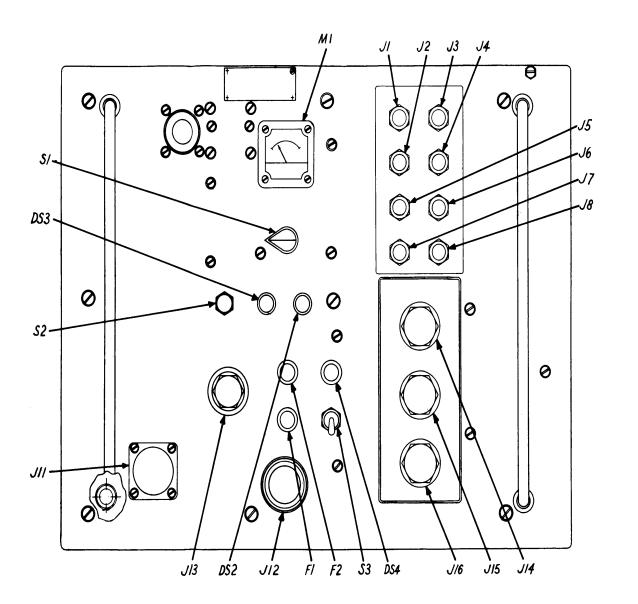

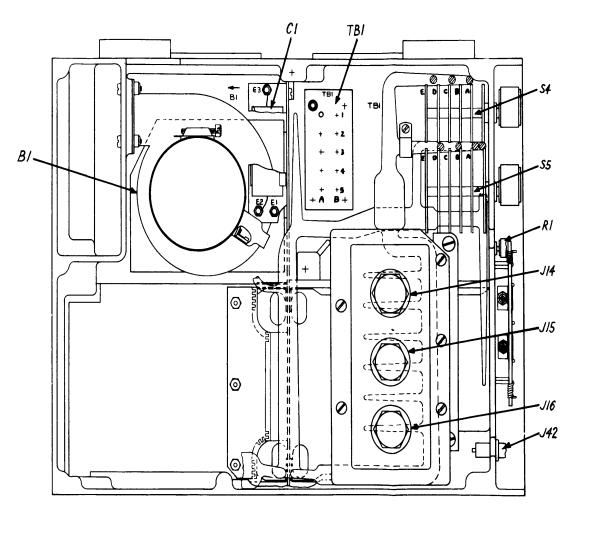

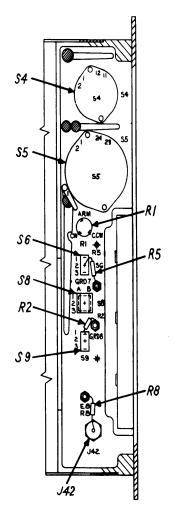

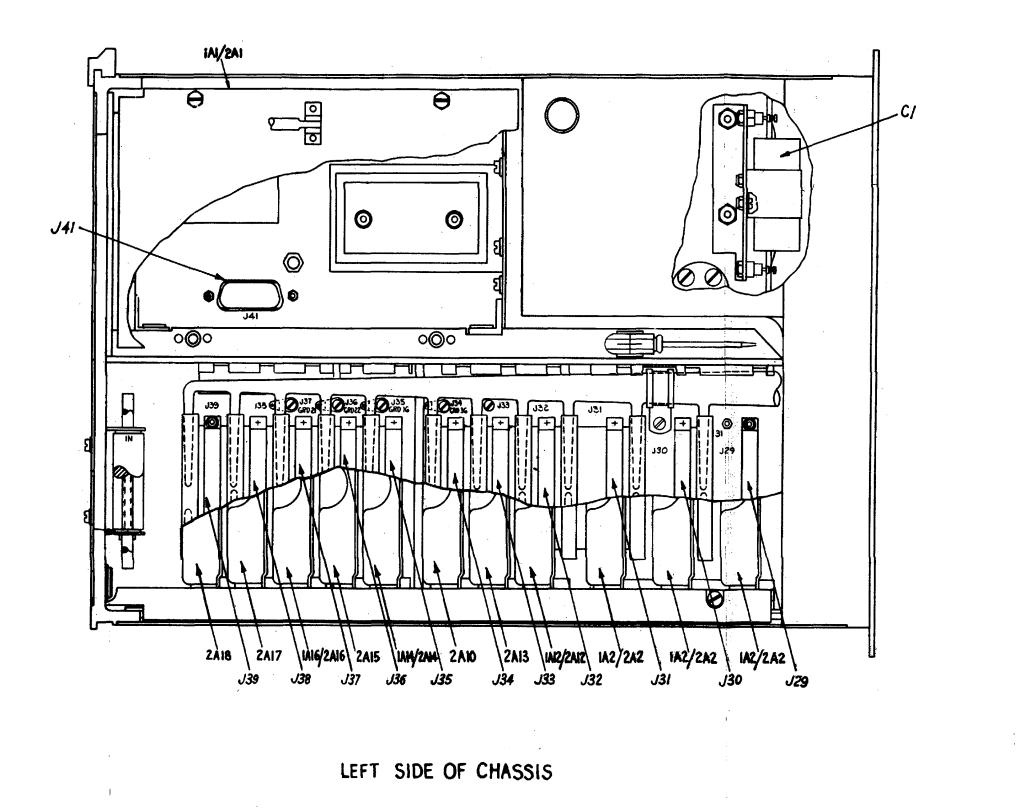

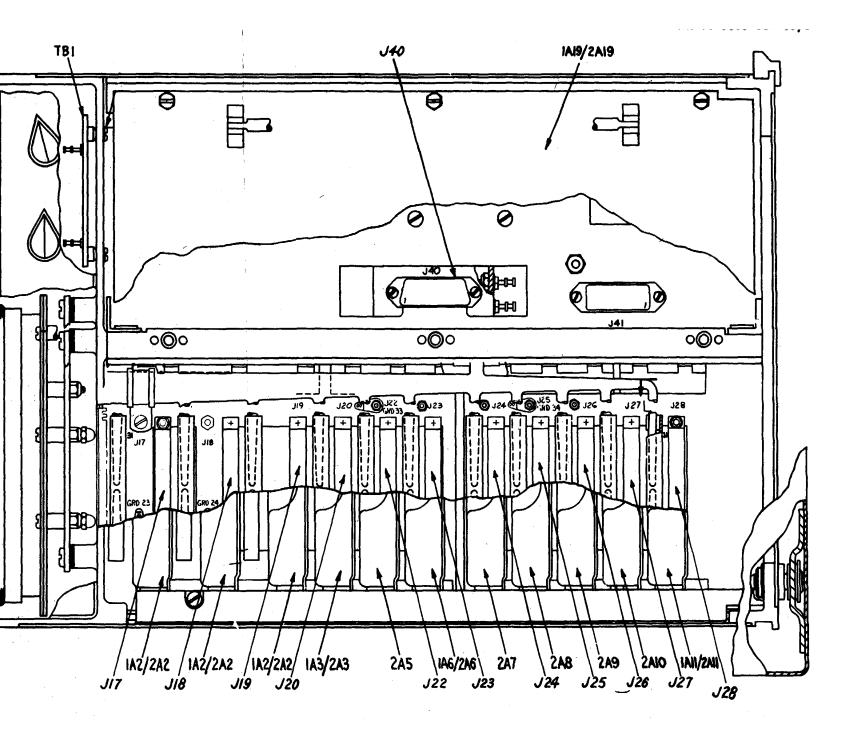

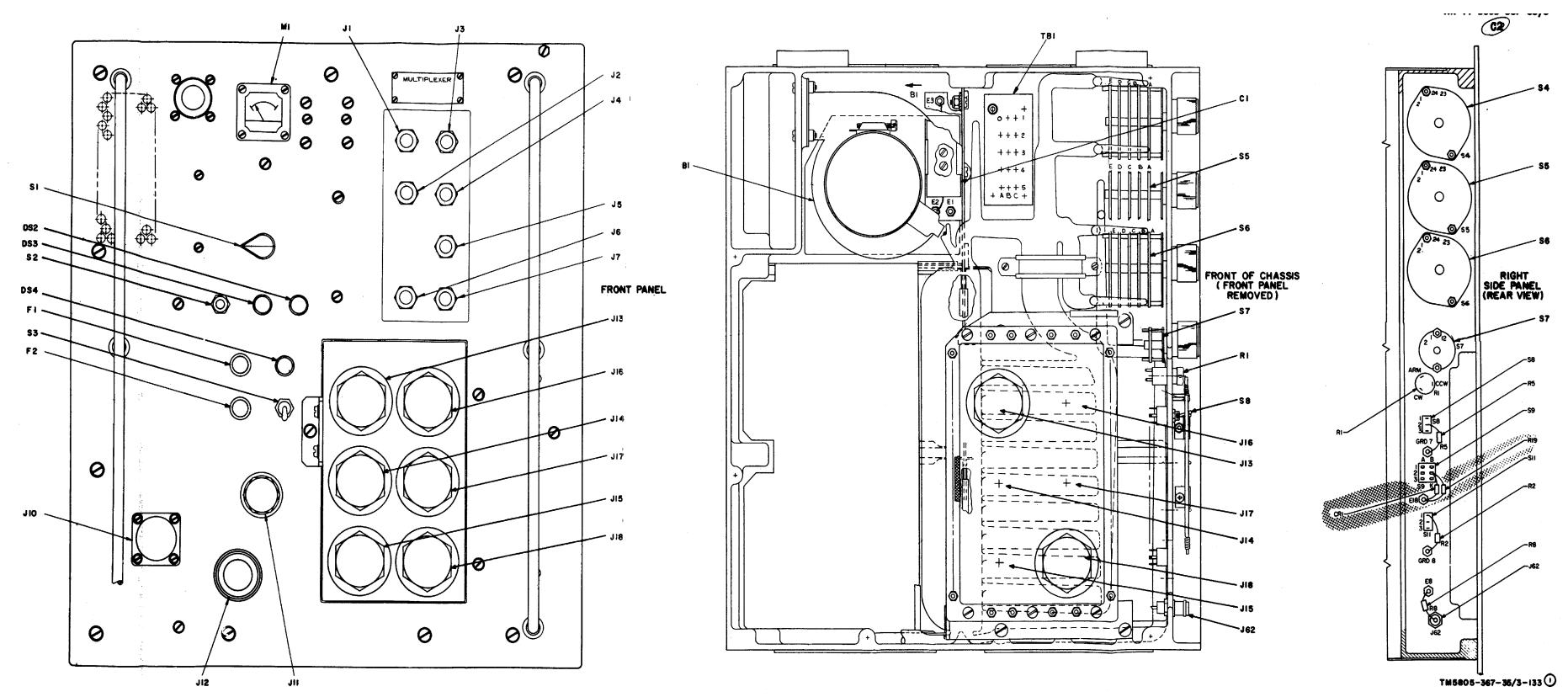

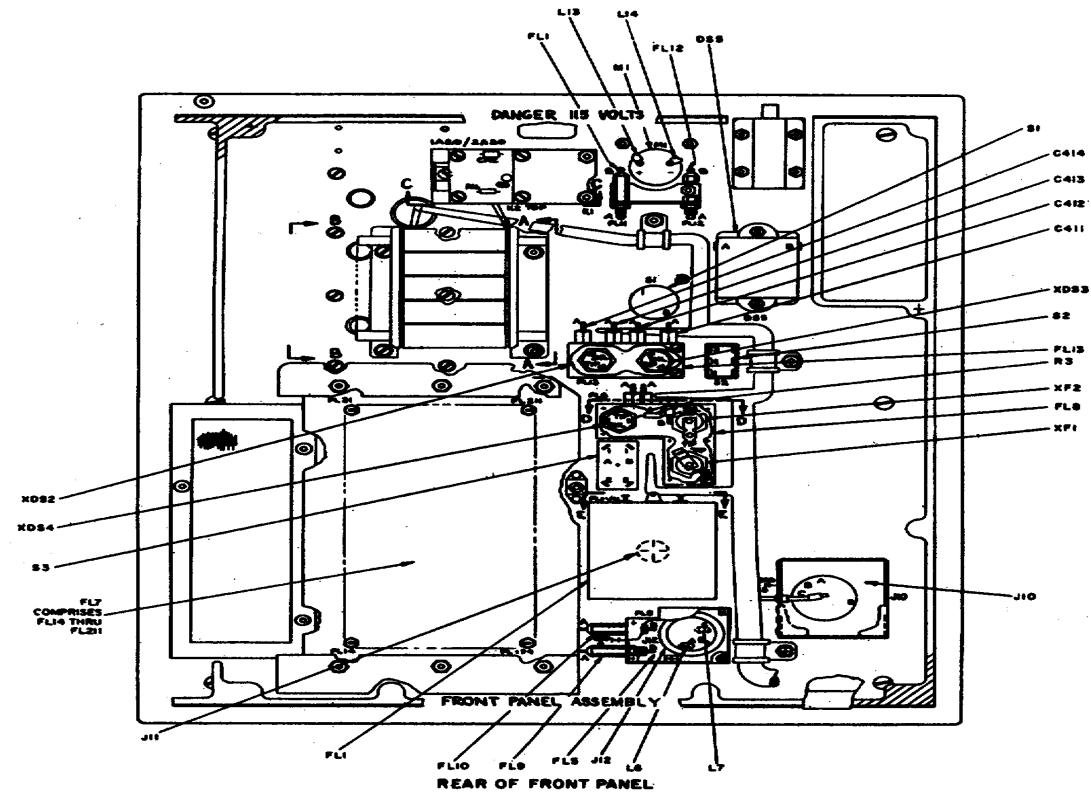

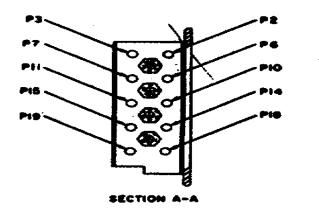

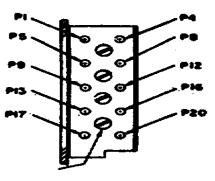

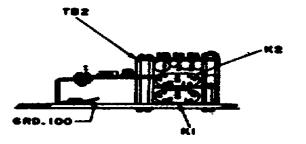

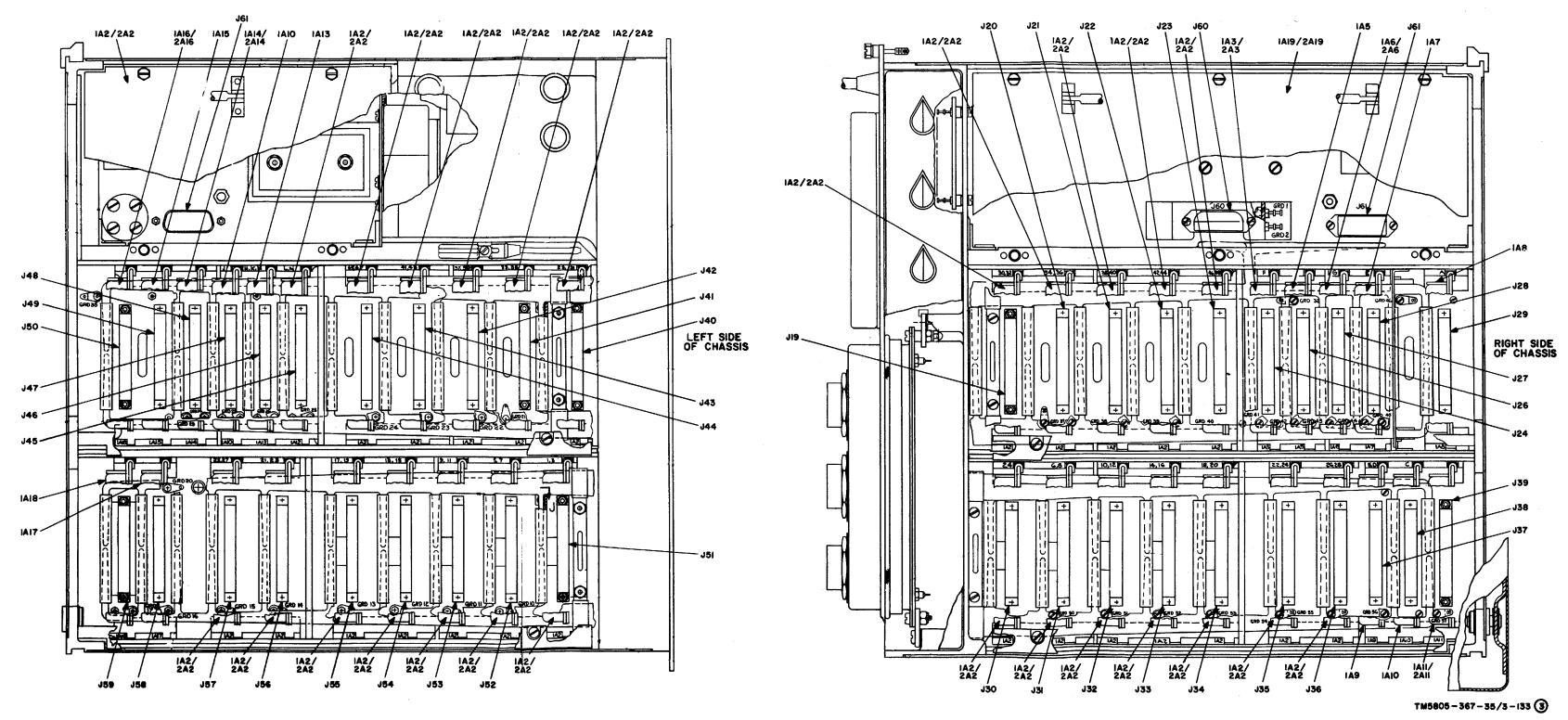

| <b>6-92</b> ① | Multiplexer TD-352/U, location of parts (part 1 of 3)      |         |

| <b>6-92</b> ② | Multiplexer TD-352/U, location of parts (part 2 of3)       |         |

| 6-923         | Multiplexer TD-352/U, location of parts (part 3 of 3)      |         |

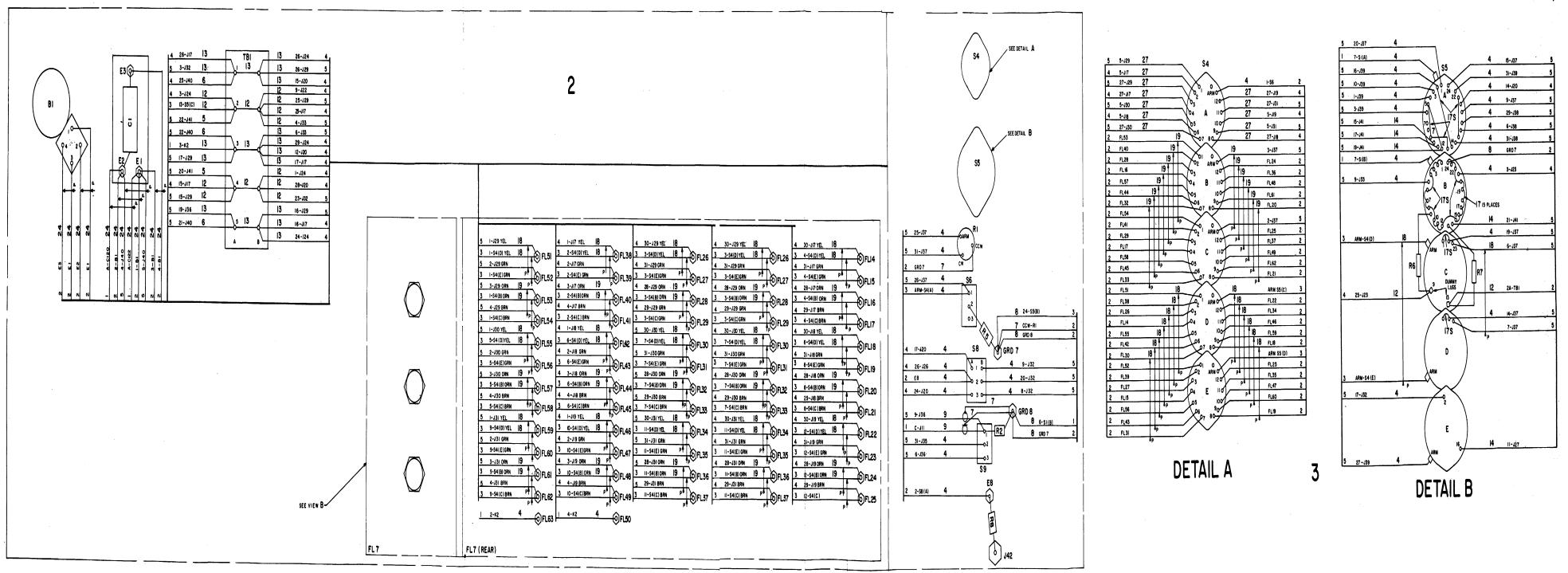

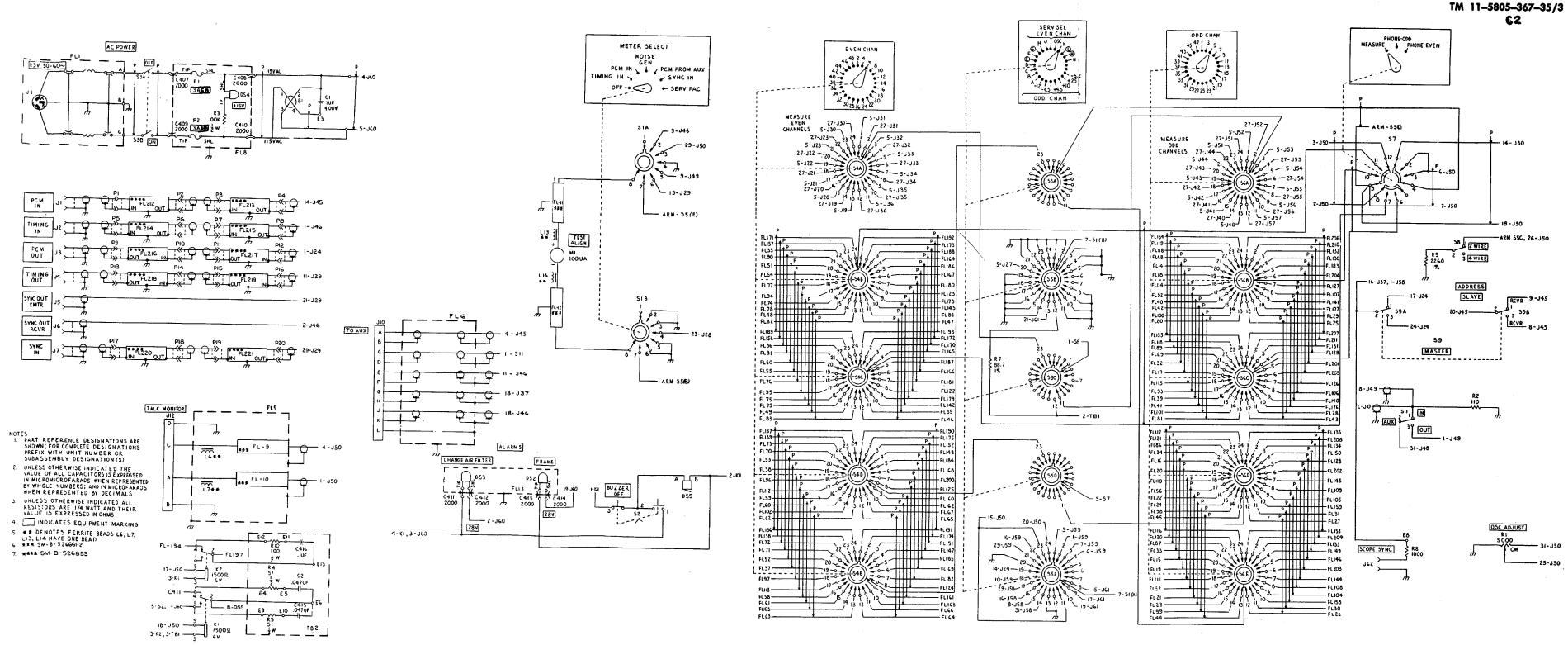

| <b>6-93</b> ① | Multiplexer TD-3S2/U, schematic diagram (part 1 of3)       |         |

| <b>6-93</b> ② | Multiplexer TD-352/U, schematic diagram (part 2 of3)       |         |

| 6-933         | Multiplexer TD-352/U, schematic diagram (part 3 of 3)      | Foldout |

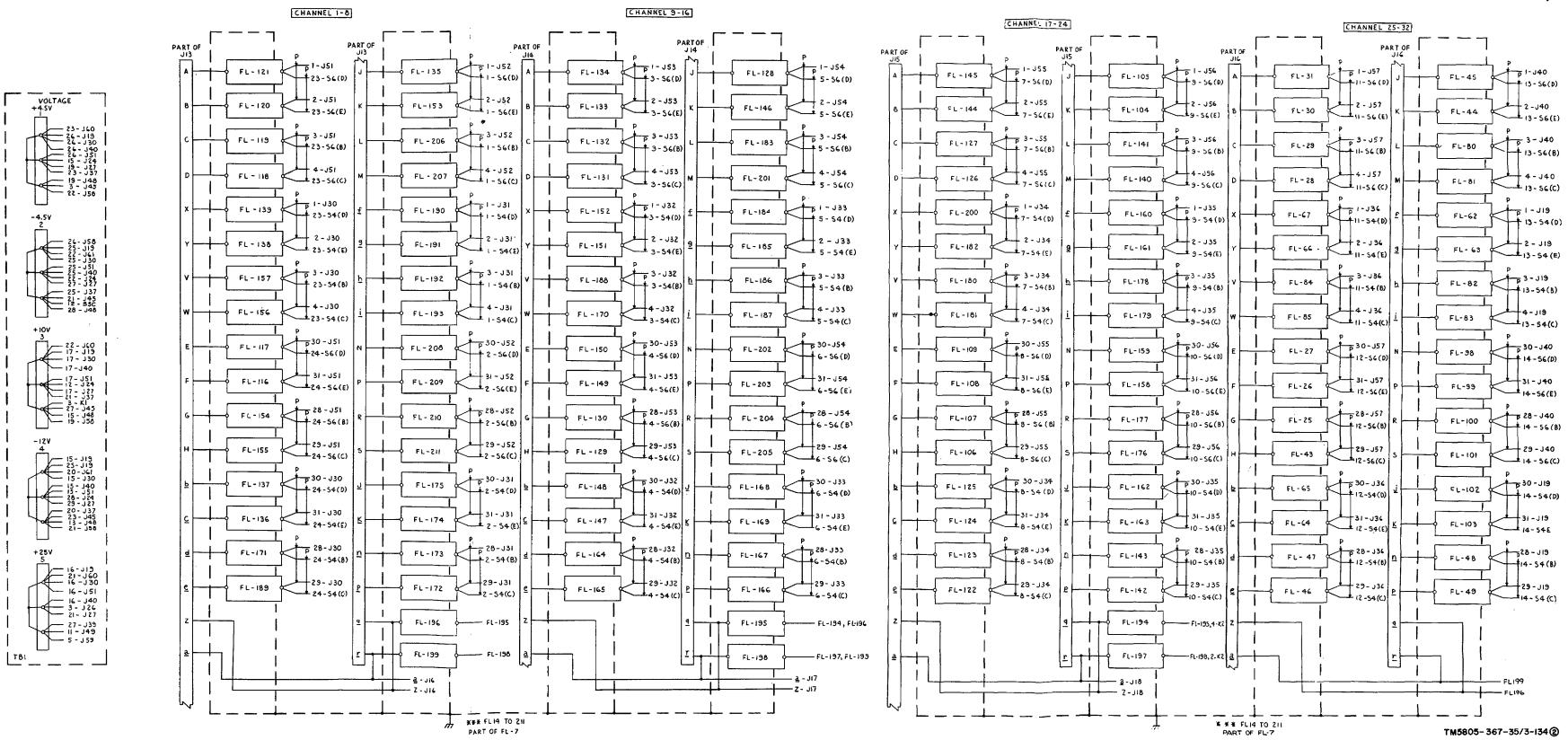

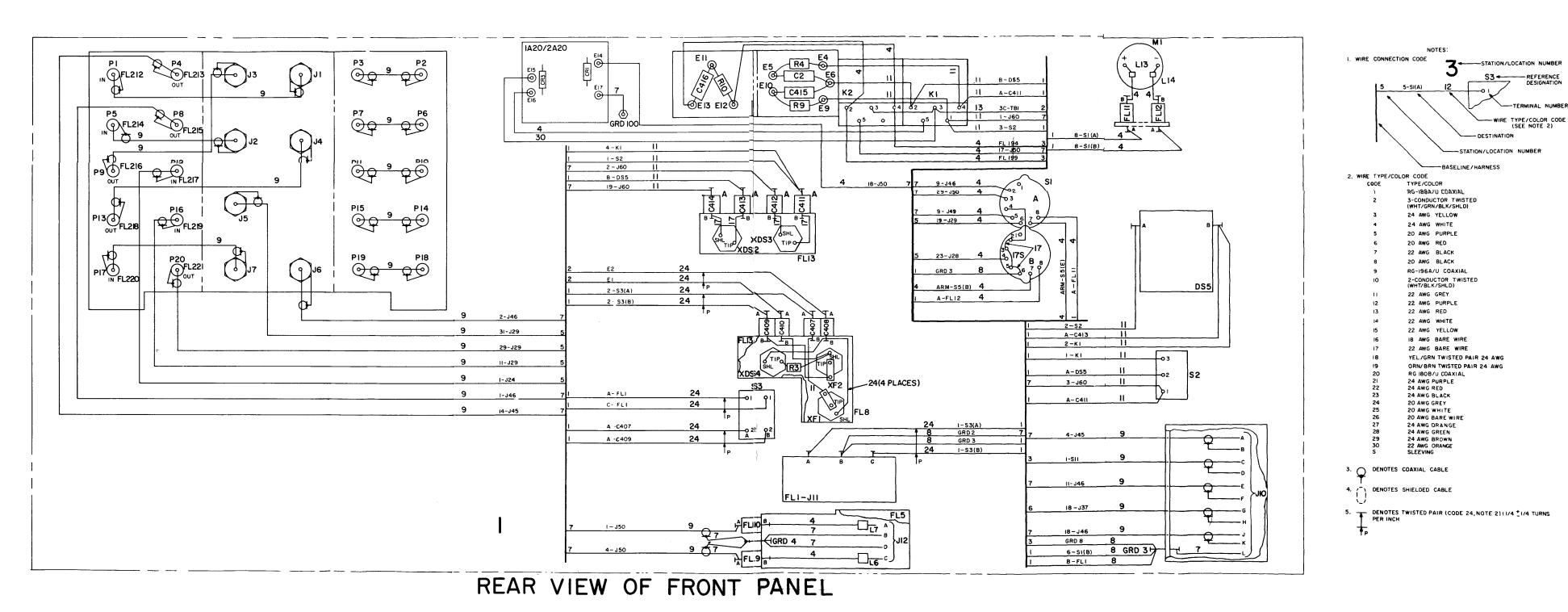

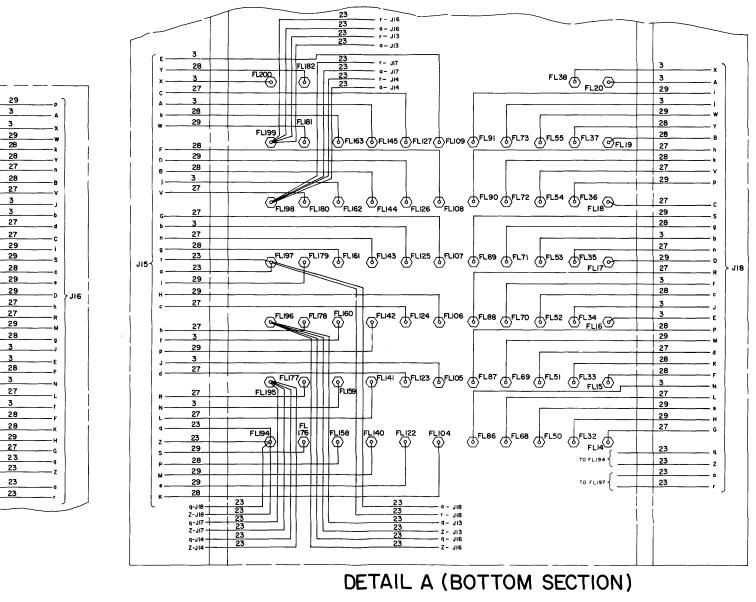

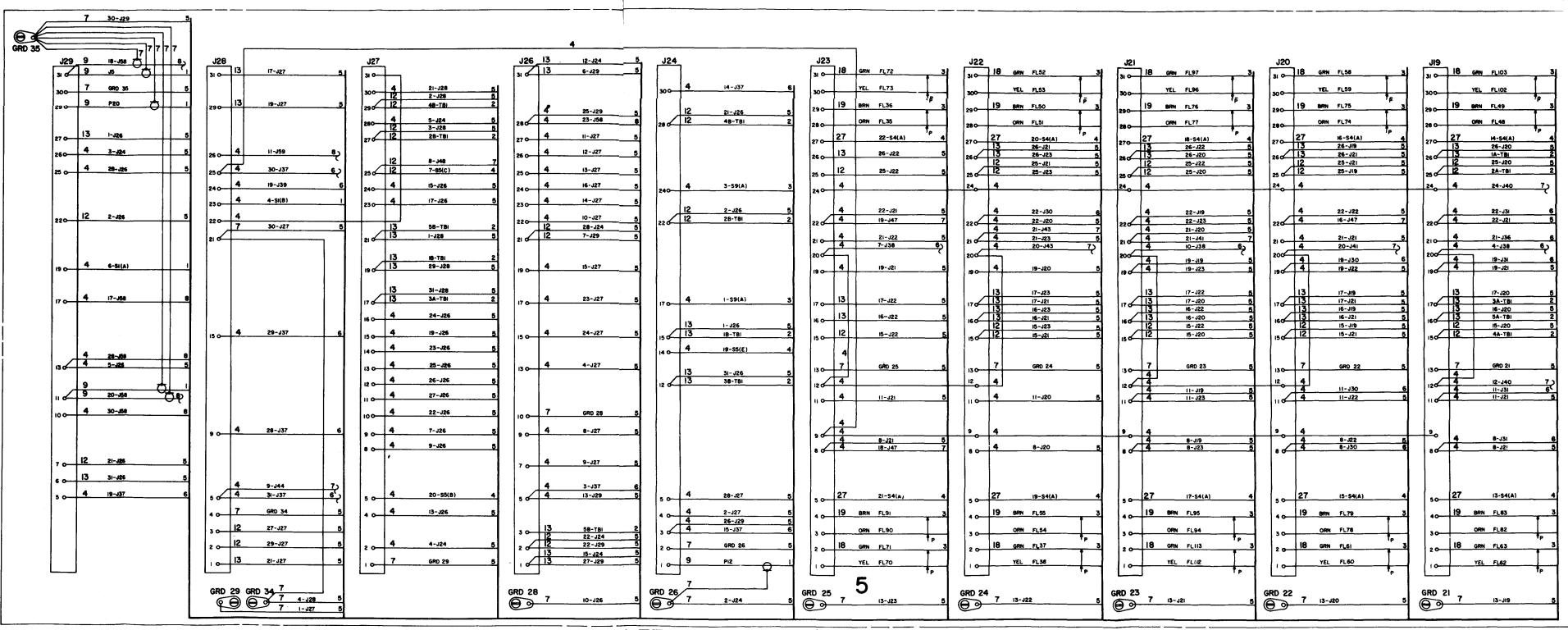

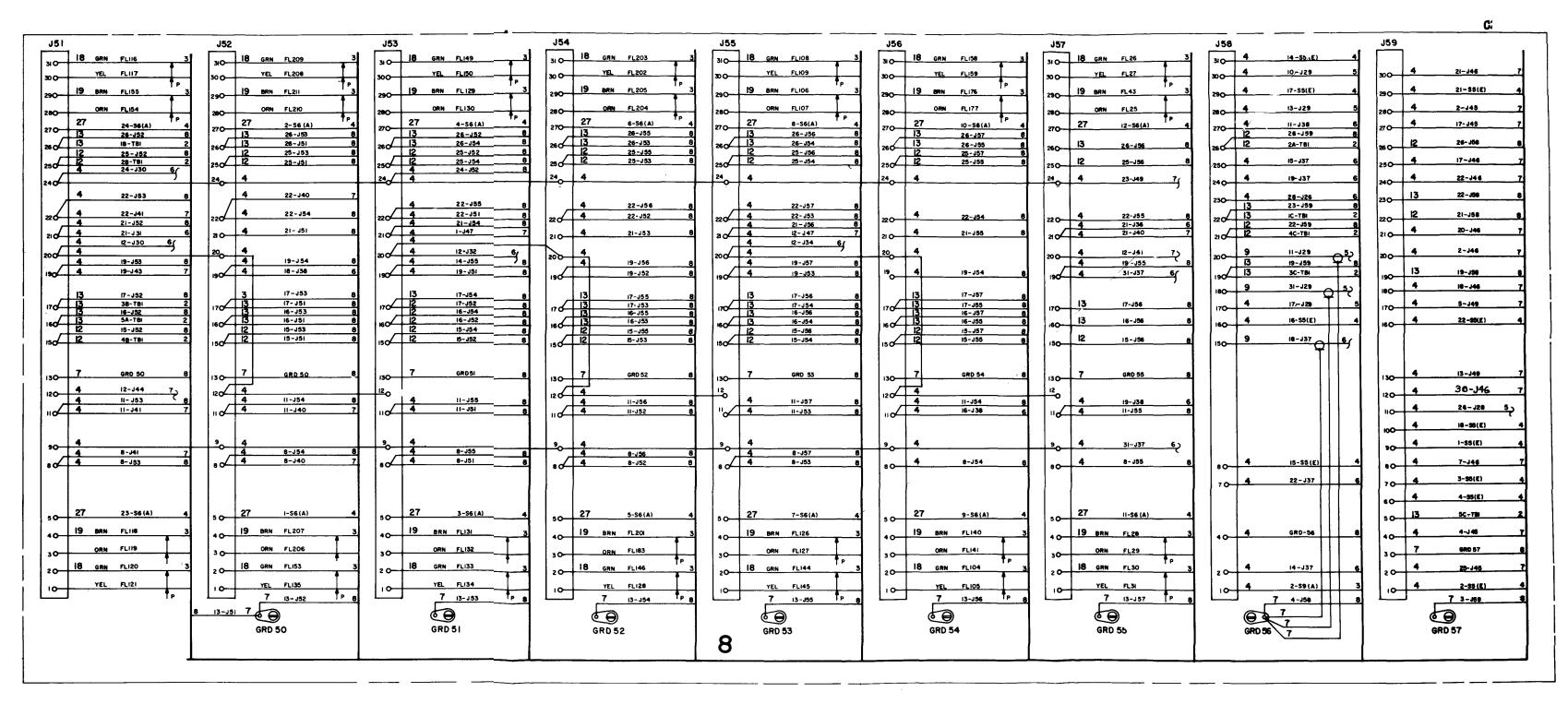

| <b>6-94</b> ① | Multiplexer TD-352/U, wiring diagram (part 1 of 4)         |         |

| <b>6-94</b> ② | Multiplexer TD-352/U, wiring diagram (part 2 of 4)         | Foldout |

| 6-943         | Multiplexer TD-352/U, wiring diagram (part 3 of 4)         |         |

| 6-94④         | Multiplexer TD-352/U, wiring diagram (part 4 of 4)         | Foldout |

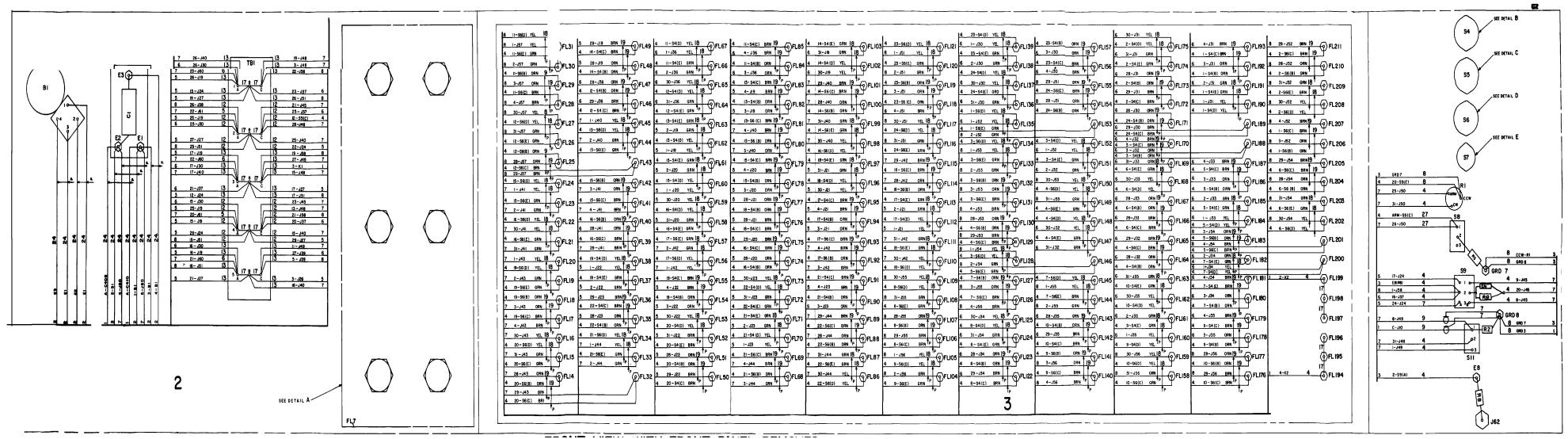

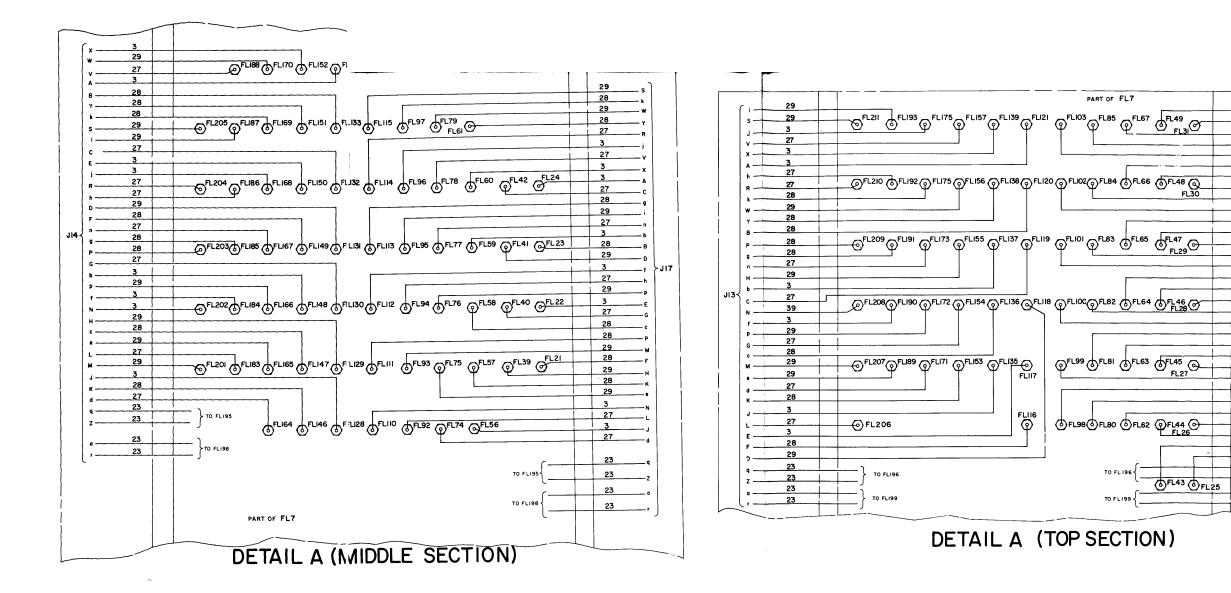

| 6-951         | Multiplexer TD-353/U, location of parts (part 1 of 3)      |         |

| 6-95©         | Multiplexer TD-353/U, location of parts (part 2 of 3)      |         |

| 6-953         | Multiplexer TD-353/U, location of parts (part 3 of 3)      |         |

| 6-961         | Multiplexer TD-353/U, schematic diagram (part 1 of 5)      |         |

| <b>6-96</b> ② | Multiplexer TD-353/U, schematic diagram (part 2 of 5)      |         |

| 6-963         | Multiplexer TD-353/U, schematic diagram (part 3 of 5)      |         |

| 6-96④         | Multiplexer TD-353/U, schematic diagram (part 4 of 5)      | Foldout |

| 6-965         | Multiplexer TD-353/U, schematic diagram (part 5 of 5)      |         |

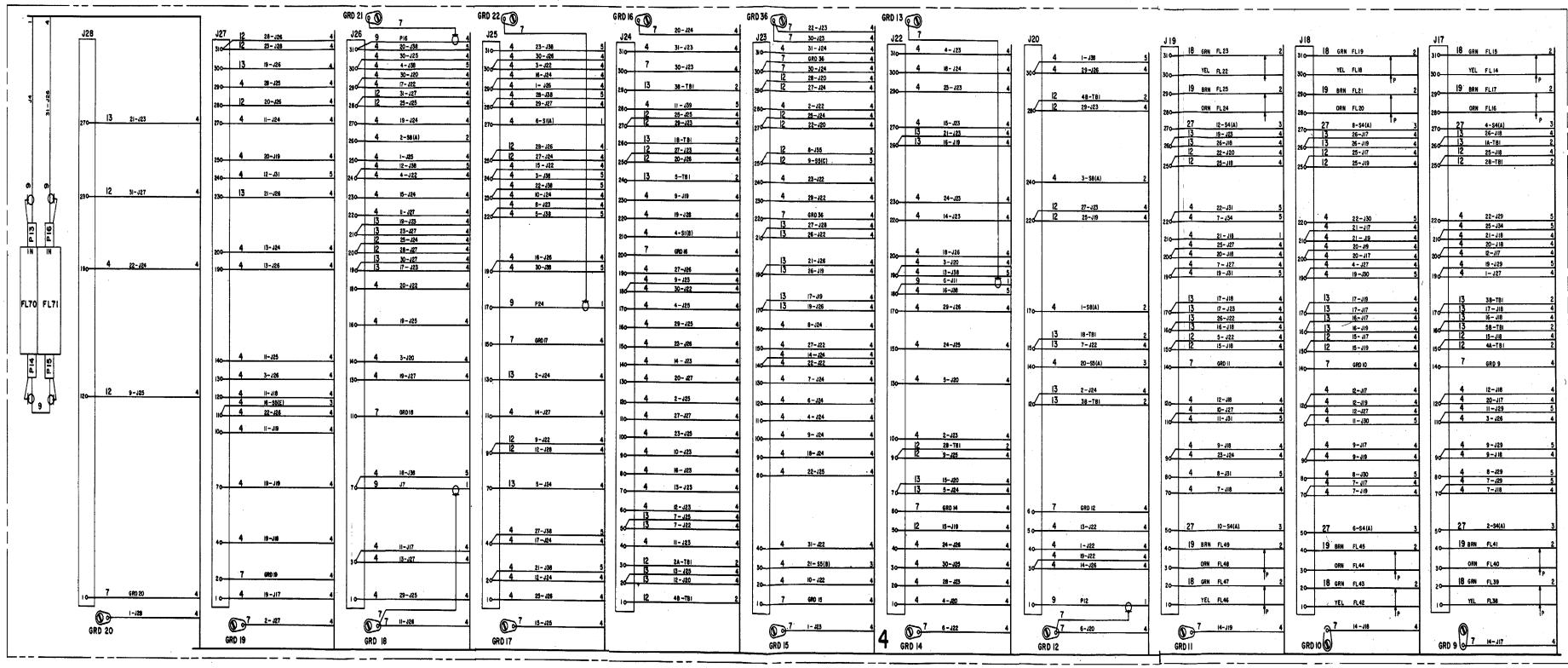

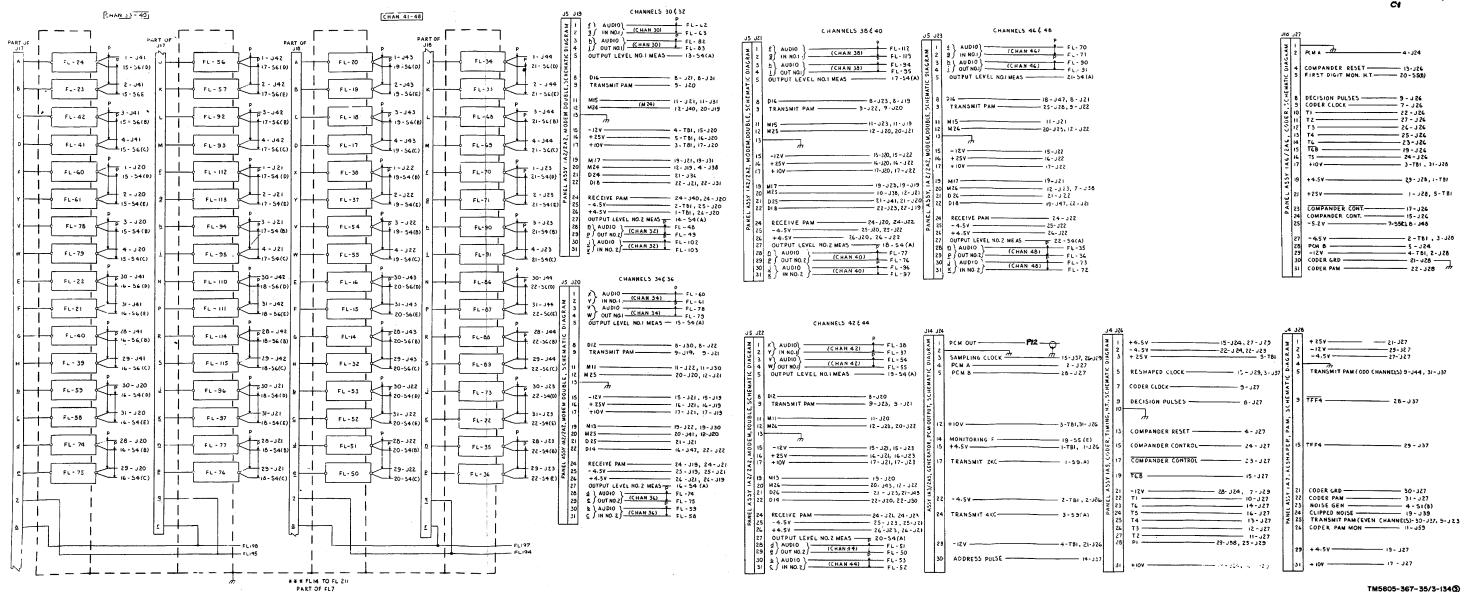

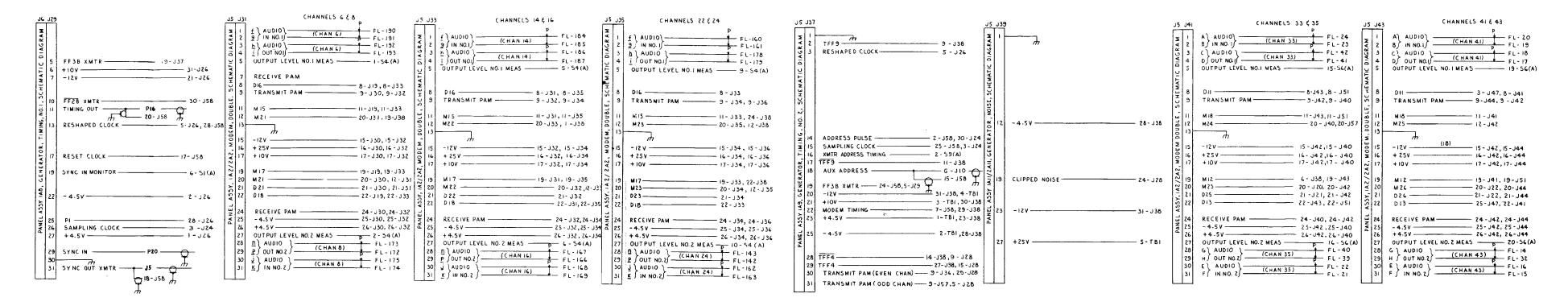

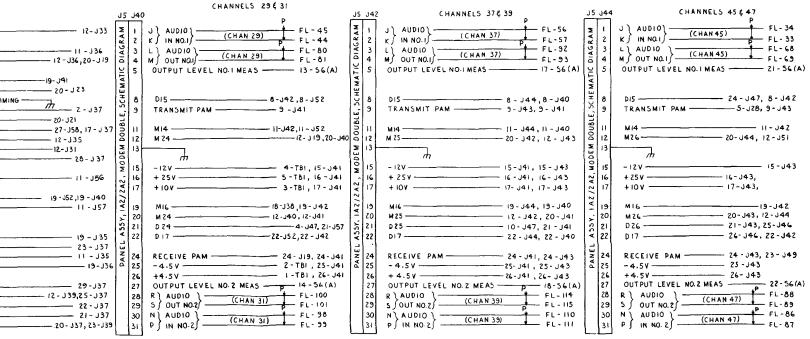

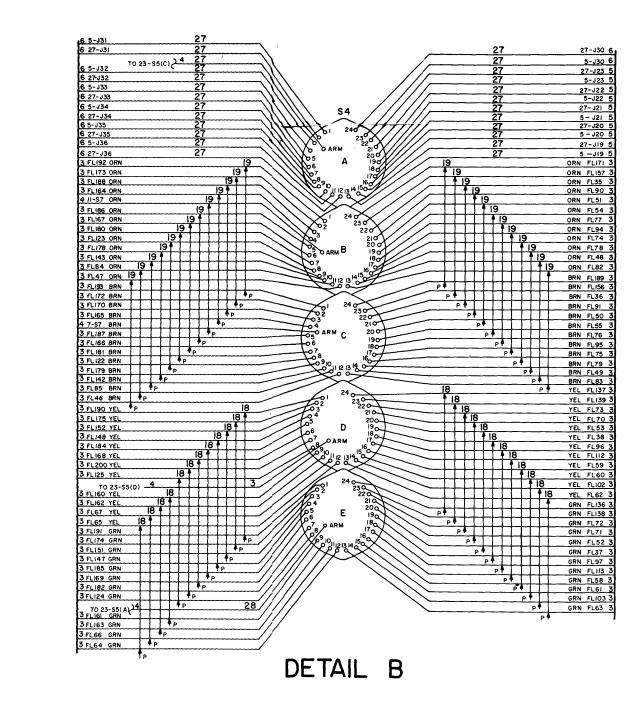

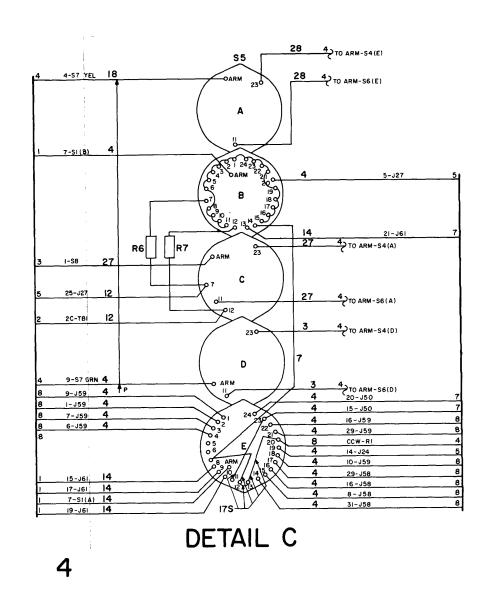

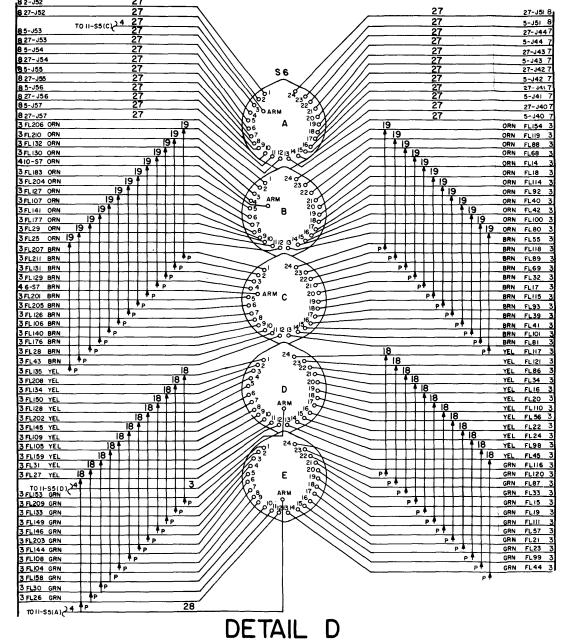

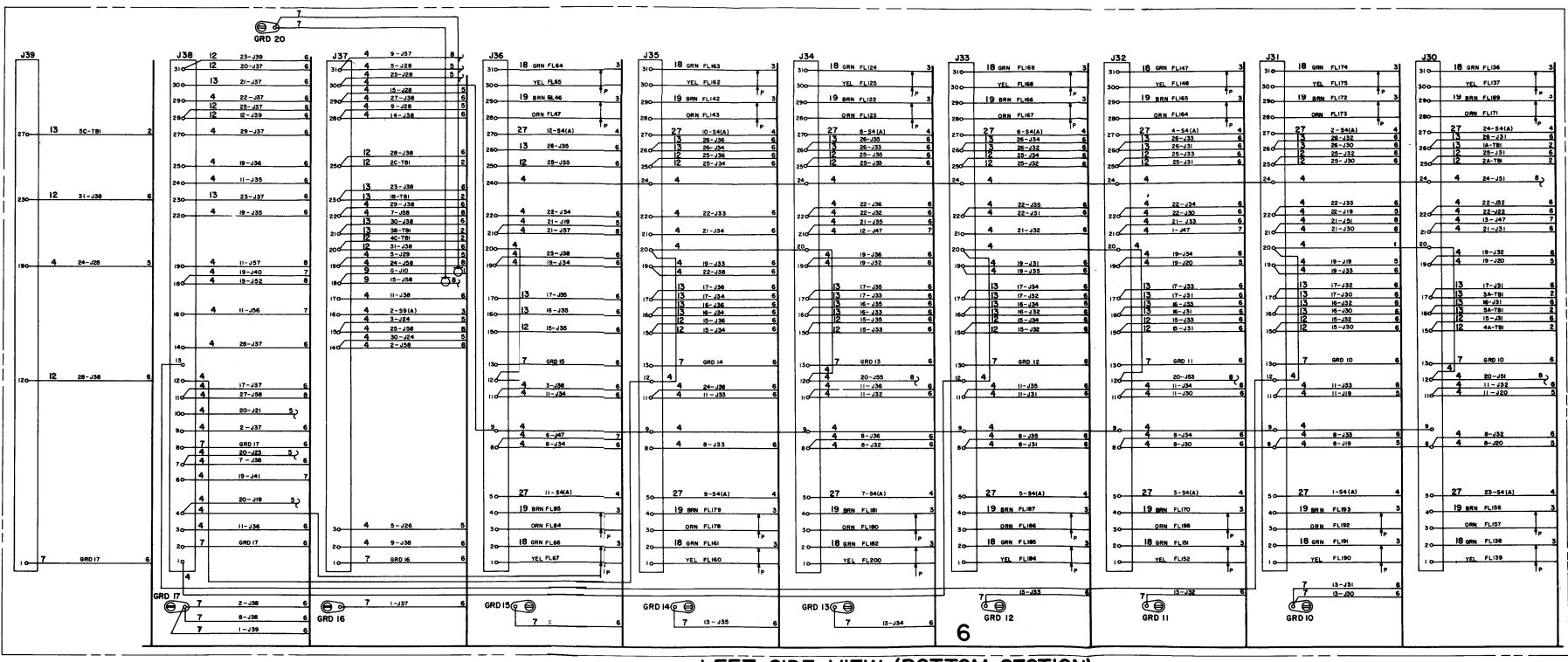

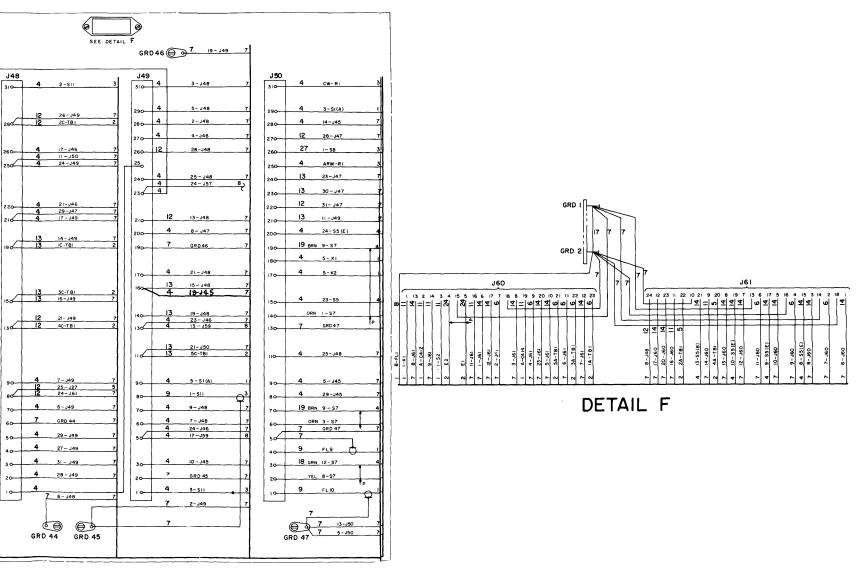

| <b>6-97</b> ① | Multiplexer TD-353/U, wiring diagram (part 1 of 8)         |         |

| <b>6-97</b> ② | Multiplexer TD-353/U, wiring diagram (part 2 of 8)         |         |

|               |                                                            |         |

Change 5 vi

# LIST OF ILLUSTRATIONS-CONTINUED

| Fig.#         | Title                                              | Page    |

|---------------|----------------------------------------------------|---------|

| 6-973         | Multiplexer TD-353/U, wiring diagram (part 3 of 8) | Foldout |

| 6-97④         | Multiplexer TD-353/U, wiring diagram (part 4 of 8) | Foldout |

| 6-975         | Multiplexer TD-353/U, wiring diagram (part 5 of 8) | Foldout |

| 6-97⑥         | Multiplexer TD-353/U, wiring diagram (part 6 of 8) | Foldout |

| <b>6-97</b> ⑦ | Multiplexer TD-353/U, wiring diagram (part 7 of 8) | Foldout |

| 6-97®         | Multiplexer TD-353/U, wiring diagram (page 8 of 8) | Foldout |

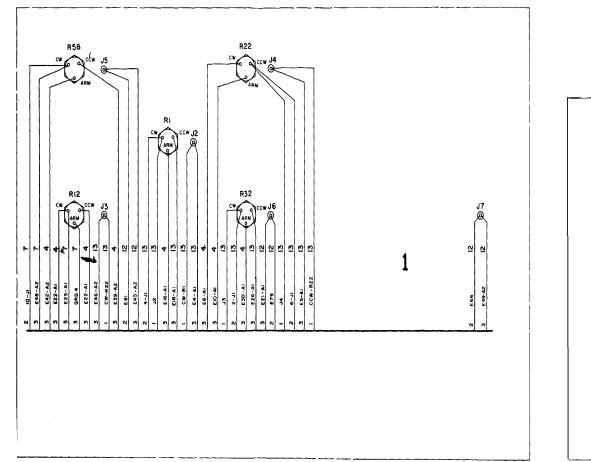

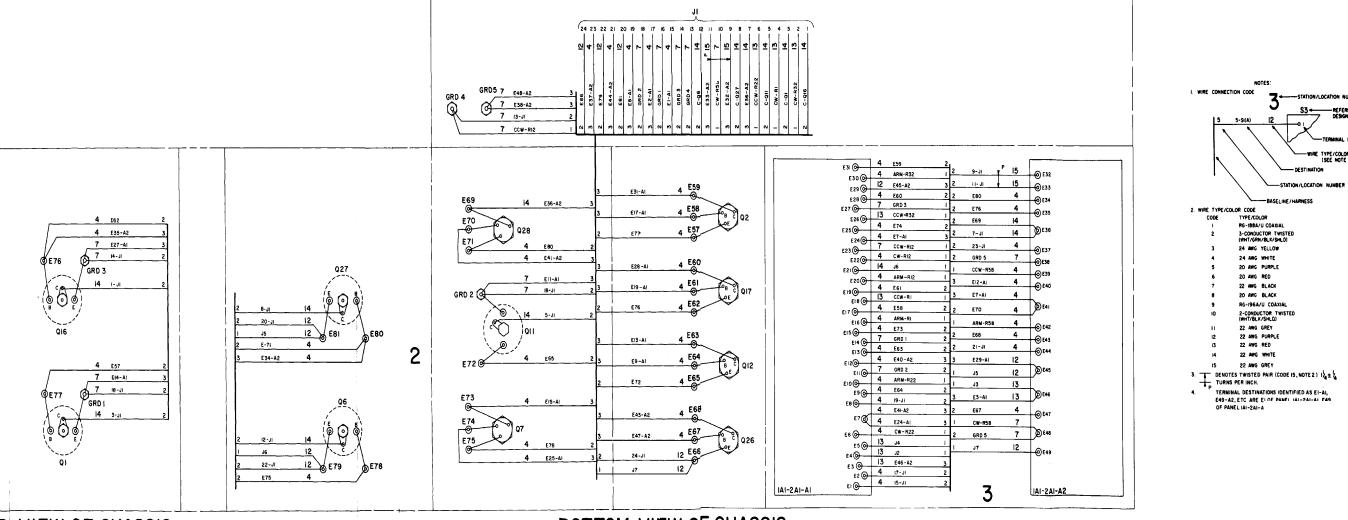

| 6-98          | Panel 1A1/2A1, wiring diagram                      | Foldout |

| 6-99          | Panel 1A19/2A19, wiring diagram                    |         |

Change 5 vi

#### **CHAPTER 1**

#### INTRODUCTION

#### 1-1. Scope

a. This manual covers direct and general support and depot maintenance for Multiplexers TD-352/U and TD353/U. It includes instructions for troubleshooting, testing, aligning, and repairing the equipment, replacing maintenance parts, and repairing specified maintenance parts. It also lists tools, materials, and test equipment required for direct and general support and depot maintenance. Detailed functions of the equipment are covered in paragraphs 2-1 through 2-9.

b. The complete technical instructions for this equipment include TM 11-5805-367-12.

c. Throughout this manual, reference to panel 1A6/2A6 also applies to panel 1A6A/2A6A. Reference to 1A14/2A14 also applies to panel 1A14A/2A14A and reference to panel 1A12/2A12 also applies to panel 1A12 unless otherwise specified. Reference to panel 1A2/2A2 also applies to 1A2A/2A2A.

#### 1-2. Consolidated Index of Army Publications and Blank Forms.

Refer to the latest issue of DA Pam 310-1 to determine whether there are new editions, changes or additional publications pertaining to the equipment.

#### 1-3. Maintenance Forms, Records and Reports

*a.* Reports of Maintenance and Unsatisfactory Equipment. Department of the Army forms and procedures used for equipment maintenance will be those prescribed by DA PAM 738-750 as contained in Management Maintenance Update.

*b.* Report of Packaging and Handling Deficiencies. Fill out and forward SF 364 (Report of Discrepancy (ROD)) as prescribed in AR-735-11-2/DLAR 4140.55/NAV-MATINST 4355.73B/AFR 400-54/MCO 4430.3H.

*c. Discrepancy in Shipment Report (DISREP)(SF361).* Fill out and forward Discrepancy in Shipment Report (DISREP){SF361) as prescribed in AR55-38/NAVSUPINST 4610.33C/AFR 75-18MCO P4610.19D/DLAR 4500.15.

#### 1-4. Deleted.

#### 1-5. Reporting Equipment Improvement Recommendations (EIR)

If your multiplexer TD-352/U or TD-353/U needs improvement, let us know. Send us an EIR. You, the user, are the only one who can tell us what you don't like about the design. Put it on an SF 368 (Quality Deficiency Report). Mail it to Commander, US Army Communications-Electronics Command and Fort Monmouth, ATTN: AMSEL-PA-MA-D, Fort Monmouth, NJ 07703-5000.

#### 1-6. Differences Between Semiconductor Subassemblies

This paragraph contains information covering redesigned multiplexer subassemblies 1A2/2A2, 1A2A/2A2A, and 1A6A/2A6A used in the TD-352/U and TD-353/U Multiplexers. These redesigned subassemblies use silicon semiconductors in lieu of germanium devices. Subassemblies equipped with silicon semiconductors have a black anodized frame and are identified by the suffix letter A. For example, 1A6A denotes a silicon version and 1A6 denotes a germanium version of the same multiplexer subassembly. It is possible that multiplexers in the field might be equipped with a combination of germanium and silicon subassemblies. The germanium subassemblies and the silicon subassemblies can be used interchangeably.

#### Note

Unless otherwise noted in this manual, data relating to the subassemblies containing germanium semiconductors apply to the subassemblies containing the silicon subassemblies.

Silicon subassemblies are considered to be non-repairable and should be returned to depot for final disposition.

Change 5 1-1/(1-2 Blank)

#### **CHAPTER 2**

#### FUNCTIONING

#### Section I. BLOCK DIAGRAM ANALYSIS, MULTIPLEXER TD-352/U

#### 2-1. General

In conjunction with other terminal equipment, Multiplexer TD-352/U delivers audio signals over radio relay or cable lines. The TD-352/U accepts 12 audio channels, samples each channel at an 8-kilocycle (kc) rate, and combines the resultant pulse amplitude modulated (pam) samples on a time division basis. It then codes the samples with a six-digit binary code and delivers the resulting pulse code modulated (pcm) output signal to either Multiplexer TD-202/U (radio interface unit) or TD-204/U (cable interface unit) for transmission. In the receive traffic direction, the TD-352/U accepts an incoming pcm pulse train from either the TD-202/U or TD-204/U and decodes it, thereby restoring the original Pam signals. The Pam signals are finally demodulated into the 12 audio channels.

#### 2-2. Transmit Circuits for TD-352/U

(fig.6-33)

a. Audio Circuits. The audio input for each channel is applied to a separate pam modulator. Six double modem panels 1A2/2A2, each containing two modulator circuits, are used. In the modulators, the audio signals are sequentially sampled at an 8-kc rate by timing signals developed by the modem timing matrix in panel 2A10. In this manner, the sampled audio signals are placed on the common transmit pam line and applied to panel 2A7 in proper time sequence. In panel 2A7, the pam signals are resampled at a 96-kc rate and reshaped in the sample and store circuits. The 96-kc timing signal, TFF5, is also obtained from panel 2A10. At this point, a cupped noise signal, obtained from noise generator panel 1A11/2A11 is inserted to insure a random one-level code change on the pam line in the absence of any audio input. This masks low level random noise caused by crosstalk between channels and prevents interference with audio reception. The output of the sample and store circuits is amplified and then applied to the pam-pcm converter circuits on panel 1A6/2A6.

*b. Coding Circuits.* In panel 1A6/2A6, the pam signals are either amplified or attenuated, depending on their individual input amplitude. The amplifier-attenuator (compander) circuit compresses high-level pam samples relative to the low-level pam samples <u>under control of</u> the compander control and compander control signals developed on panels 2A5 and 1A6/2A6. The pam signal, properly attenuated or amplified, is then applied to the coder circuits on panel 1A6/2A6. The coder, a sequential feedback circuit, consists of a decision network, storage flip-flops, and ladder network with associated clamping flip-flops. The clamping flip-flops and ladder network form a digital-to-analog converter. The coder timing signals (T pulses) are generated on panel 2A7 using timing signal inputs from panel 2A8. Six T pulses (T1 through T6) are used to drive the clamping flip-flops in proper sequence. Panel 2A8 also supplies the necessary decision pulses for operation of the decision circuit. The output of the decision circuit is a six-bit binary pulse equivalent in amplitude to the input pam pulse after amplification or attenuation. The output of the decision circuit is stored in a flip-flop that supplies half-width pam with a digit rate of 1,152 kc, applied from coder panel 1A6/2A6 to output panel 2A5.

*c.* Output Circuits. The half-width pcm signal is applied to a shift register on panel 2A5 where it is retimed under the control of the parallel shift, shift 1, and shift 2 signals. The output of the panel 2A5 shift register is retimed full-width pcm (570 kc). The retimed pcm is next applied to panel 1A3/2A3 where the selected master (4-kc) or slave (2-kc) address is inserted. After address insertion, the pcm signal is applied through the output circuit to the front panel PCM OUT connector.

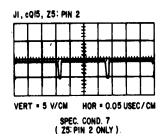

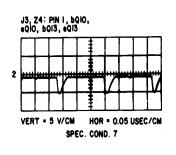

*d. Transmit Timing Circuits.* Panels 2A8, 2A9, and 2A10 comprise the transmit timing circuits. A crystal oscillator in panel 2A8 generates the basic 2,304-kc master clock signal from which all transmit timing signals in the TD-352/U are derived.

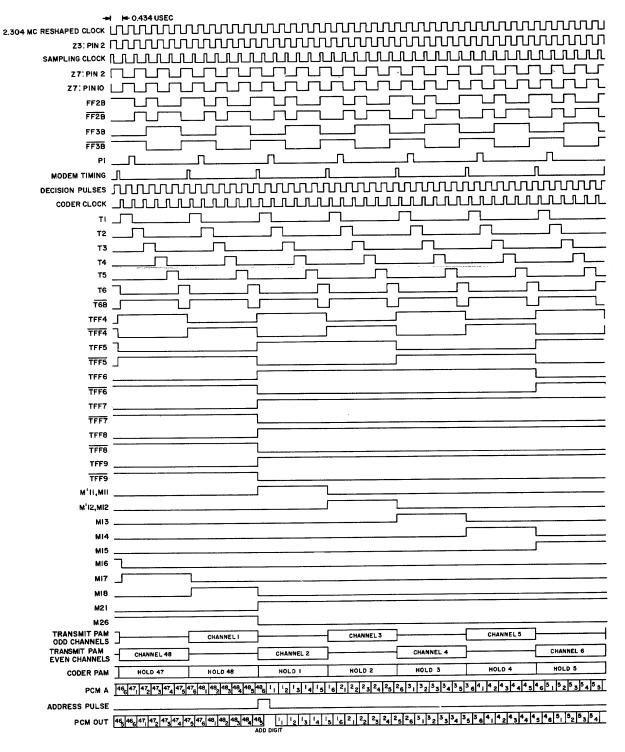

derived. In multichannel systems, the transmit timing signals of both master and slave multiplexers must be in synchronization. This condition is accomplished by synchronizing the basic clock in the multiplexer acting as the slave unit with a 576-kc signal obtained from the multiplexer acting as the master unit. The 576-kc signal used for this purpose originates in the master clock countdown circuits of panel 2A8 where it is termed TFF2 (576-kc). This signal is buffered in panel 2A9 and applied to a front panel output connector as the SYNC OUT XMTR signal. The 576-kc SYNC OUT XMTR signal from the master unit is applied to the SYNC IN connector on the slave unit. The SYNC IN signal is applied to an automatic switch circuit in panel 2A8 which synchronizes the output of the basic clock. When the TD-352/U is used in a 12-channel system, synchronization of the basic clock is unnecessary since all transmit timing signals in the unit are-referenced to the master 2,304-kc signal. Principal among the transmit timing signals generated in the countdown circuit of panel 2A8 is the modem timing (384-kc) signal. This signal is used to drive a second countdown chain on panel 2A10, the outputs of which are applied to the modern timing matrix. The outputs of the matrix are the 8kc modulator timing signals which control audio channel sampling-activity in modem panels 1A2/2A2. Other transmit timing signals are used in the pam sample and store, and coder timing circuits of panel 2A7; the pampcm conversion circuits of panels 1A6/2A6 and 2A5; and the pcm address and output circuits of panel 1A3/2A3. A timing diagram, using idealized transmit timing signal waveforms, is shown in figure 6-34.

#### 2-3. Receive Circuits for TD-352/U

#### (fig 6-35)

a. Pcm Input, Decoding, and Demodulating Circuits. The pcm input signal is applied to the front panel PCM IN connector and is fed to three sampler gates in panel 1A12/2A12. In 12-channel operation, the input signal consists of one pcm train and contains a 4-kc address. In 24-channel operation, the input signal consists of two interleaved pcm signal trains, one with a 4-kc address and one with a 2-kc address. The address is inserted in the pcm signal by operating the ADDRESS switch in the unit at the transmitting terminal to MASTER (4-kc) or SLAVE (2-kc), depending on whether the multiplexer is acting as a master or slave unit in the transmitting system. In 12-channel systems the ADDRESS switch is always in the MASTER position. The pcm train, which will be decoded, is determined by the setting of the ADDRESS switch in the unit at the receiving terminal. This signal is always sampled in sampler gate A and is designated pcm A. The other train, designated pcm B. is sampled in sampler gate B and is delivered directly to the front panel ALT PCM connector without being decoded. The pcm signal is also fed to sampler gate C for extraction of the address signal. Timing A, B. and C signals, from the receive timing circuits, are responsible for the operation of the sampler gates. The pcm A output of sampler gate A is reshaped and sent to decoder panel 1A14/2A14 through-either the auxiliary unit or an internal delay line in panel 2A15. The delay line compensates for the delay introduced by the auxiliary unit. In panel 1A14/2A14, the pcm signal is converted from a digital to an analog signal. The pcm signal is then shifted into a six-stage serial register by the 576-kc decoder clock signal generated in panel 2A13. The last digit of the 12th channel has a 2- or a 4-kc frame sync signal. This signal is removed (becomes inaudible) when the pcm is shifted from the serial to the parallel set of registers by the address digit gate. The decoder pam output is fed to expander panel 2A16, which expands the peaks of the signal. The pam expander output corresponds to the pam signal fed into the transmit coder circuit (para 2-2b). The decoder pam output is sent to the demodulator section of double modem panels 1A2/2A2 where it is sampled and stored to lengthen the pulse, filtered, and amplified. The amplified outputs are 600-ohm, balanced audio output signals and are applied to the front panel AUDIO CHAN receptacle. Demodulator timing signals from panel 2A10 control the sample and store circuits in panels 1A2/2A2.

*b.* Receiver Timing. The 576-kc timing in signal enters the front panel receptacle and is fed to a frequency doubler in panel 2A13. The 1,152-kc doubler output is fed to a pulse inhibitor. A skip pulse is also fed to the inhibitor from the skip-pulse gate on panel 1A12/2A12. When an out-of-frame condition occurs, the skip pulse causes one

pulse at a time to be dropped from the 1,152-kc input until the multiplexer frames in. The modified 1,152-kc output train is fed to the timing signal countdown circuits, where most of the timing signals for the receive section are generated. Timing A and timing B signals, which sample the incoming pcm signal, are generated here also. The 1,152-kc signal is counted down to provide the 8-kc timing signal C, which is sent to sampler gate C on panel 1A12/2A12. When the unit is in frame, the timing C pulse coincides with the frame pulse in the incoming pcm train. When the unit is in frame, the timing C signal samples the incoming pcm signal at the address digit rate. This information is fed to one side of an address comparator circuit. A local 2- or a 4-kc signal, selected through the ADDRESS switch, is fed to the other side of the comparator. When the unit is in frame, a number of 2- or 4-kc identical square wave pulses will exist on each side of the comparator, thereby causing no output to be generated. This action prevents the skip-pulse gate from generating skip pulses and the phase of the timing in signal is not changed. If the unit is not in, frame, the address digit will not be detected in sampler gate C and a 2- or 4-kc square wave will not be generated. A different signal will now exist on the two sides of the comparator circuit. When this condition exists, a signal is sent to the skip-pulse gate, causing it to pass one pulse of the 8-kc RFF9 signal to the 1,152-kc clock pulse inhibitor circuit in panel 2A13. The skip pulse drops out one pulse from the 1,152-kc signal, causing the phase of the receive timing signals to change by a time corresponding to one-digit width in the 24-channel operation. Therefore, this action continues until the timing C signal is coincident with the address digit. Therefore, when the timing C signal samples the proper address digit in the incoming pcm train, the skip pulses cease and the receive section of the TD-352/U is framed to the incoming pcm signal. The clock timing and countdown circuits also feed a 384-kc modem timing signal to panel 2A10. Panel 2A10 on the receive side is interchangeable with the 2A10 panel on the transmit side of the unit and performs the same functions (para 2-2d). The receive section timing diagram is shown in figure 6-36.

#### 2-4. Monitoring and Alarm Circuits for TD-352/U

#### (fig.6-37)

Alarm and monitoring circuits located on panel 1A16/2A16 provide visual and audible indications of incoming traffic framing failure and for monitoring the audio signal channels. Loss of the incoming pcm signal, or an out-of-frame condition, activates the tragic alarms and frame detector circuits, causing the FRAME indicator lamp (located on the front panel) to light and the buzzer to sound. Loss of frame due to an internal unit fault will also cause the FRAME lamp to light and the buzzer to sound. The 1,100-cycle per second (cps) test tone oscillator (nonsynchronous with system) generates a test tone for the purpose of aligning and testing the audio channel modems (panels 1A2/2A2). This is done by adjusting the OSC ADJUST knob on the service facility panel while observing the indication on the front panel TEST ALIGN meter. During normal operation, the BUZZER switch is ON and the FRAME lamp is extinguished. During normal operation, no alarm control signal is generated. If the TD-352/U drops out of frame, the alarm timing and the alarm control signals are applied to panel 1A16/2A16. This causes the FRAME lamp to light and relay K1 to energize, causing the buzzer to sound. Operating the BUZZER OFF switch (S2) connects the relay driver to the other output of the frame detector; silencing the buzzer. Loss of frame also causes a squelch signal to be sent to panels 1A14/2A14 and 2A15, preventing the pcm in signal from passing through to the demodulators while the unit is out of frame. This eliminates a disagreeable sound on the audio channels while the unit is out of frame. However, when the unit is in frame again, the flip-flop reverts to its original position, causing the buzzer to sound again. Operating the BUZZER OFF switch sets the relay to the deenergized condition and silences the buzzer. The microphone and earphone amplifiers on panel 1A16/2A16 are used in conjunction with Headset-Microphone H-91A/U. A bridging circuit is used to switch the headset in and out of a channel to prevent loading of the modem. These circuits are used for communicating over any channel selected by the SERV SEL

switch. In the audio measure circuits on panel 1A16/2A16, the audio output from any modem selected by the SERV SEL switch is amplified, buffered, and applied to the TEST ALIGN meter for alignment purposes.

#### 2-5. Fault Locator Circuits for TD-352/U

(figs.2-1 and 2-2)